一、实验目的

掌握用VHDL语句进行组合电路设计的方法,并熟悉程序的编译、调试与波形图的仿真。

二、实验内容

分别用VHDL的CASE语句及IF语句两种方法,设计6选1数据选择器。通过编译、仿真验证功能正确性。

三、实验设计

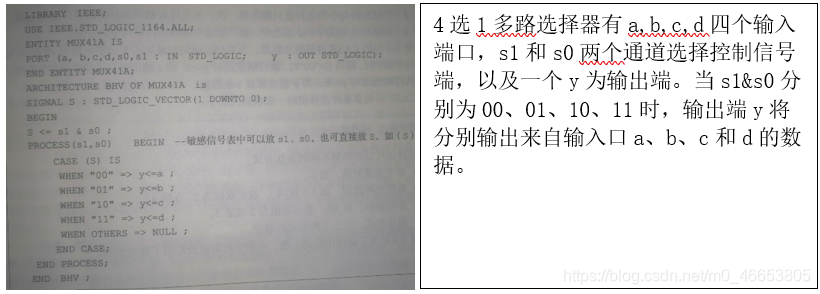

设计的依据:教材上3.3.1给出了“基于CASE语句的4选1多路选择器表述”,如下为“4选1多路选择器”的VHDL描述和功能描述。

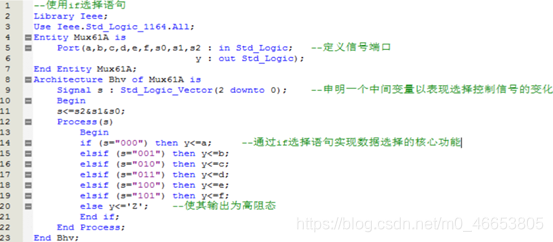

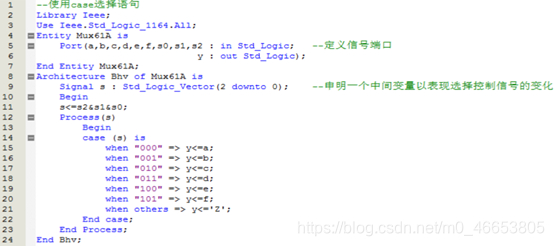

实验设计:根据“4选1多路选择器”的设计思路,考虑到“6选1多路选择器”有6个输入端口,则需要有三个通道选择控制信号端,一个输出端y。当s2&s1&s0分别为000、001、010、011、100、101时,输出端y将分别输出来自输入口a、b、c、d、e和f的数据。又考虑到三个通道选择控制信号组合成了8种情况,而前6种均有对应的操作,而后两种情况(110和111)没有对应的操作,可以使其情况下输出为高阻态。如下分别给出使用if选择语句和case选择语句的“6选1多路选择器”的VHDL描述和相关语句的解释。

四、实验结果及仿真

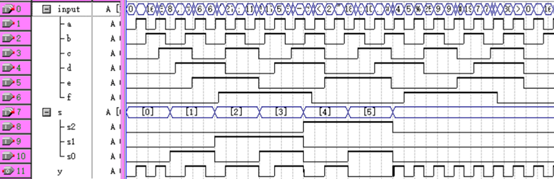

分别对a-f和s2-s0设置合适周期的方波信号输入,观察y输出信号。如下图所示。

观察输入与输出的波形可以分析出“6选1多路选择器”的功能已经实现。即当s2&s1&s0分别为000、001、010、011、100、101时,输出端y将分别输出来自输入口a、b、c、d、e和f的数据。

五、实验思考与总结

关于VHDL语言:VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。在我理解中,VHDL语言是一种更形象化的C语言,其编程格式类似于C语言那样,但其面向硬件使其较为形象化,且对程序本身的完整性提出了更高的要求,在大部分情况下,程序每个部分都需要“有头有尾”,即“End+”的存在。

关于“X选1多路选择器”:其中的X可以通过设计选择控制信号端来实现,而选择器的VHDL程序的核心部分即为if/case选择语句,其两者各有优缺,对于情况较多的情况,我认为使用case语句更加简介方便。

以下请忽略!

import numpy as np

import matplotlib.pyplot as plt

import matplotlib

list=[[1,2,3,4,5,6],[2,4,6,8,10,12],[1,3,5,7,9,11],[1.1,2.2,3.3,4.4,5.5,6.6],[3,6,9,12,15,18],[4,8,12,16,20,24

],[5,10,15,20,25,30],[1.5,2.5,3.5,4.5,5.5,6.5],[1,4,7,10,13,16],[2,5,8,11,14,17]]

a=np.array(list)

std=[]

avg=[]

x=[1,2,3,4,5,6,7,8,9,10]

for i in range(0,len(list)):

std.append(np.std(a[i]))

avg.append(np.mean(a[i]))

fig=plt.figure()

plt.xticks(x,x)

plt.plot(x,avg,marker="o",color='#858687',markeredgecolor='black',linewidth=3,label="Mean Value")

for i in range(len(avg)):

plt.text(x[i],avg[i],avg[i],fontsize=10)

y1=[]

y2=[]

for i in range(len(x)):

y1.append(avg[i]+std[i]/2)

y2.append(avg[i] - std[i] / 2)

plt.fill_between(x,y1,y2,color='#d2e3f0',label="Standard deviation")

plt.grid()

plt.legend(loc=2)

plt.show()

989

989

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?