代码:

// 约束引脚号

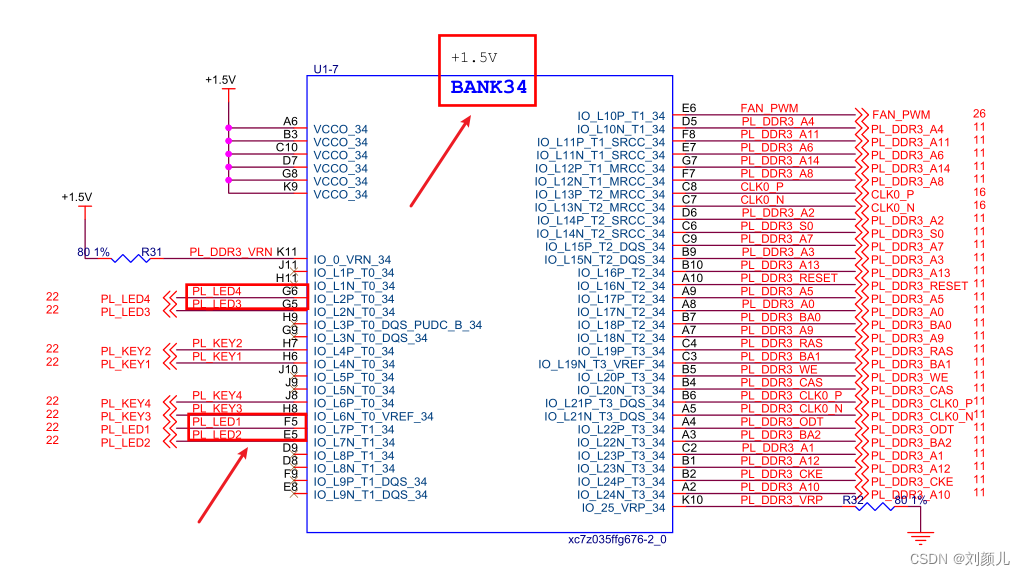

set_property PACKAGE_PIN F5 [get_ports {led_tri_o[0]}]

set_property PACKAGE_PIN E5 [get_ports {led_tri_o[1]}]

set_property PACKAGE_PIN G5 [get_ports {led_tri_o[2]}]

set_property PACKAGE_PIN G6 [get_ports {led_tri_o[3]}]

// 约束电压

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[3]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[2]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[1]}]

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[0]}]

XDC 编写的语法

约束引脚号:set_property PACKAGE_PIN " 引脚编号 " [ get_ports “端口名称”]

约束电压: set_property IOSTANDARD " 电平标准 " [ get_ports “端口名称” ]

重点

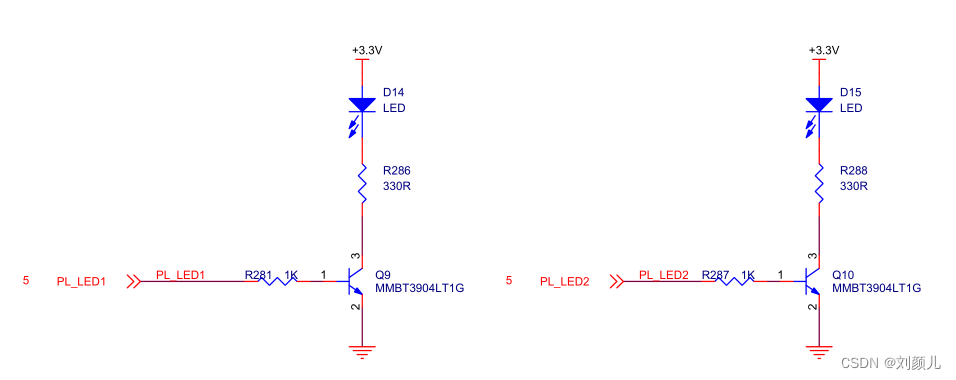

通过原理图,查看LED与FPGA中实际引脚相连位置,然后看驱动该FPGA的Bank是多大的电压,如果是1.5V电压驱动,那就是LVCMOS15 ,如果是1.8V驱动,那就是LVCMOS18

解读

set_property:设置属性

IOSTANDARD :IO标准

LVCMOS15 :1.5V

get_ports :获取端口

led_tri_o[3]:第3个led端口

PACKAGE_PIN :引脚

F5 :引脚约束到F5

通俗理解

set_property IOSTANDARD LVCMOS15 [get_ports {led_tri_o[3]}]修改led_tri_o[3]的IO标准为1.5V

set_property PACKAGE_PIN G6 [get_ports {led_tri_o[3]}] 将led_tri_o[3]约束到G6引脚

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?