1 前言

1.1 Quad SPI Flash

QSPI的I/O接口如图1所示,其中:

① CS:片选信号,低电平有效(FLASH被选中);

② CK:时钟信号,由主设备产生;

③ SI/SO: SI,即MOSI(master out slave in);SO,即MISO(master in slave out);

对于master(一般为芯片)来说,MOSI通常为数据发送口,MISO为数据接收口;

对于slave(一般为flash)来说,MOSI通常为数据接收口,MISO为数据发送口。

④ WP:写保护接口;

图1 QSPI I/O接口示意图

SI/SO组成了SPI(Serial Peripheral Interface)全双工通信的基础,可同时收发。对于传统SPI来说,SI对于主设备只能是输出,用于发送数据;SO对于主设备只能接收数据,即这两个I/O口是单向的。QSPI将这两个I/O口作为普通I/O口来使用,即数据可以双向传输,同时将WP和RESET口也用作数据传输的I/O口,组成了DQ0~DQ3双向四通道,数据传输速度直接起飞。

1.2 数据有效窗口(Data Valid Window)

1.2.1 传统DDR频率较低情形

如图2所示,DDR Quad在时钟的上升沿和下降沿读取数据。

图2 传统低频DDR时序示意图

其中:

① tv: clock-to-data-out time,表示从时钟上升沿或下降沿开始,到数据变得有效的这一过程所经历的时间;

② tHo: hold time,表示在一次时钟变化沿后,数据保持有效的时间;

③ Pck:clock period,时钟周期,对于DDR来说,显然是以半周期进行数据采样的;

④ tDV: 数据有效窗口的最小值(the minimum data valid window);

当DDR的频率较低时,若tv小于Pck,且tv和tho的值不变时,则由tdv = Pck/ 2- tv + tho可知,DDR的时钟(CK)频率越高,Pck越小,tv就越小。所以,DDR的CK频率存在上限(66 MHz),举例来说:

• Pck = 15 ns (66 MHz)

• tv [max] = 6.5 ns

• tho [min] = 1.5 ns

• tdv = Pck / 2 - tv + tho: 15 ns / 2 - 6.5 ns + 1.5 ns = 2.5 ns

1.2.2 高频率下数据有效窗口

当DDR的频率较高时,tv和tho正相关,这就使得数据有效窗口与tv和下一个时钟沿的到来时间强相关;才外,由于CK很高,这使得tv会很接近Pck,甚至会超过Pck,从而需要新的方法来确定数据有效窗口(如图3所示),并在窗口中找到合适的数据采样点(DLP正致力于此,by using the DLP feature an optimal strobe point can be found within the data window)。

图3 高频DDR时序示意图

2 DLP原理

2.1 DLP的作用及基本原理

如前文所述,SPI接口已经从单向单比特SDR I/O接口发展到SDR/DDR双向四比特Qaud接口,单向变双向,单车道变四车道, I/O效率显著提升。

随之而来的问题是,由于Quad SPI Flash 66MB /s (SDR@133 MHz)和80MB /s (DDR@80 MHz)的高时钟速率,使用tv(max)作为数据窗口内的数据采样点(strobe point)的传统方法不再奏效;DLP(data learn pattern)则闪亮登场,用于优化QSPI的数据读取性能。

DLP在每个数据信号上提供一个已知的数据序列(通常表现为在指定位置放置指定DLP数据,以用于主控制器的训练),使得主控制器(主设备)可以确定收数时最佳捕获数据时序。简单来说,可以理解为DLP是对读数据操作进行了标定,或者说时监督式的训练,从而帮助主控制器确定合适的数据读取时序。

总的来说,在数据读取过程中,主设备会使用DLP进行过采样,从而确定最佳的数据捕获点;此外,DLP会对读操作进行校准,对由于工艺、电压、温度等因素带来的误差进行补偿,使得DDR频率轻松上80MBps不是梦。

2.2 主设备抓取数据策略(Host Capture Strategy)

总的来说,主机控制器会将DLP的输入数据作为测试序列(即DLP数据已知),进而根据读该数据序列时系统的反馈确定tv和tDV,而一旦DLP找到合适的数据有效窗口,读数据的时间余量最大的那个采样点会被选为最优采样点(Once the data eye has been identified during the DLP portion of the read sequence, the controller selects the optimal data-capture point to maximize the timingmargin for the read data)。

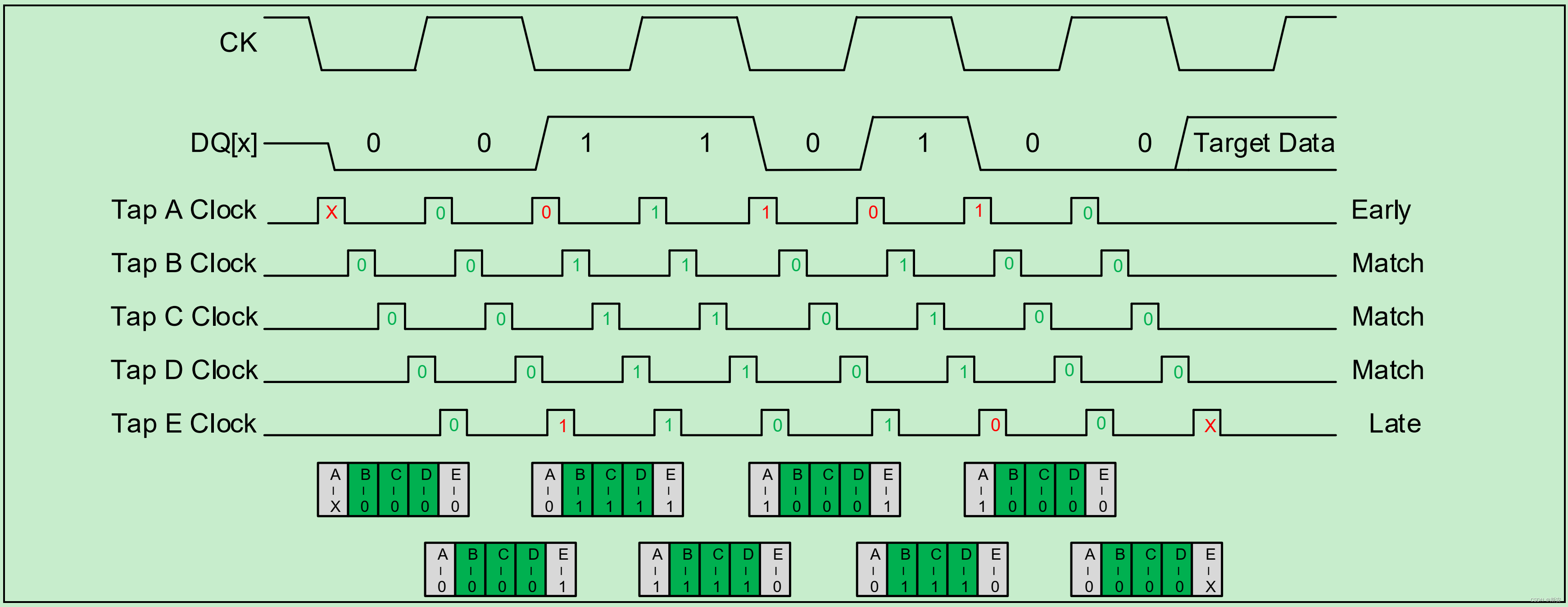

图4 Host Capture Strategy DDR

通常可以用过采样的方法,建立多个贯穿数据有效窗口 (data-valid window)的数据捕获点(data-capture points),以作为样本。如图4所示,单个DQ由五个样本通道组成,每个通道之间由固定的采样延迟。这五个通道延迟的采样点(A到E)可以用延迟锁定环路( delay-locked loop,DLL)或过采样时钟(oversampling clock)生成,过采样时钟又使用内部可用的更高频率时钟生成。当DLP输出时,主控制器对目标DQ进行采样。

其中,B/C/D三个通道都成功地抓取了DLP输入数据,且通道C的余量最大,因此被选为最佳训练参数。

3 结论

随着嵌入式应用程序性能要求的不断提高,传统的SPl接口和协议已无法满足读取速度进一步提高的需求。DLP方法的出现,使得基于Quad SPI的Flash可以实现更高的数据速率。这一增强型的解决方案,在合理的成本控制前提下,极大程度地提高了数据读取速率,同时最大限度地减少了引脚数、PCB复杂性、封装尺寸和成本,极大地改善了系统设计和性能。

3672

3672

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?