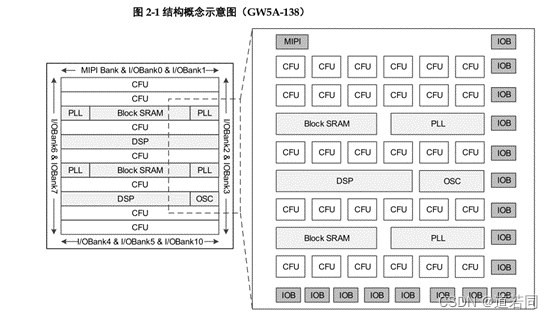

知识点1:高云FPGA的组成

高云FPGA的组成如图2-1所示,由输入输出I/O口、可配置功能单元(CFU)(xilinx叫可配置逻辑单元CLU)、块静态随机存储器BSRAM、锁相环PLL、数字信号处理器DSP。

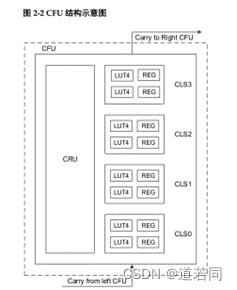

知识点2:可配置功能单元(CFU)的构成

可配置功能单元(CFU)是构成高云半导体 FPGA 产品内核的基本单元,如图2-2所示,每个基本单元可由四个可配置逻辑块(CLS)以及相应的可配置布线单元(CRU)组成,其中每个可配置逻辑块各包含两个四输入查找表(LUT)和两个寄存器(REG)。

(xilinx的基本逻辑单元是CLB,每个CLB包含2个逻辑块slices,每个slices由4个6输入LUT、8个寄存器、数据选择器扥组成,高云不同)

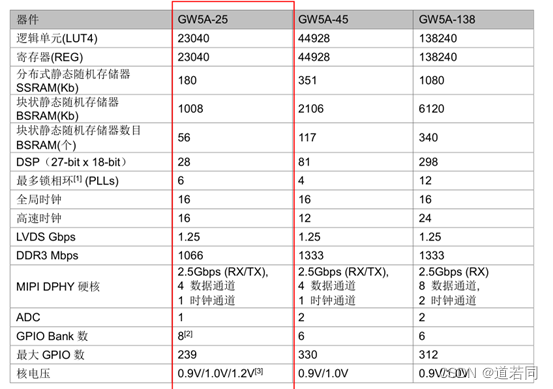

知识点3:高云FPGA资源情况

以型号为“GW5A-EV25MG196SC2/I1”的高云FPGA情况为例,该型号高云FPGA具有逻辑单元-查找表(LUT4)23040个,逻辑单元-寄存器(REG)23040个,BSRAM为1008Kb。

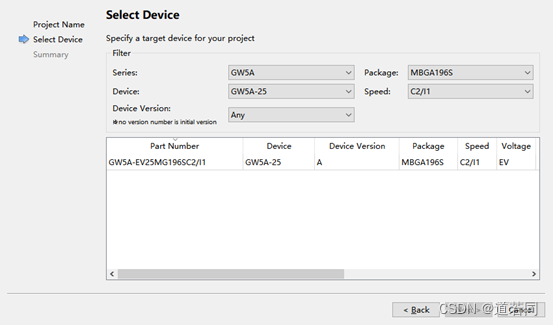

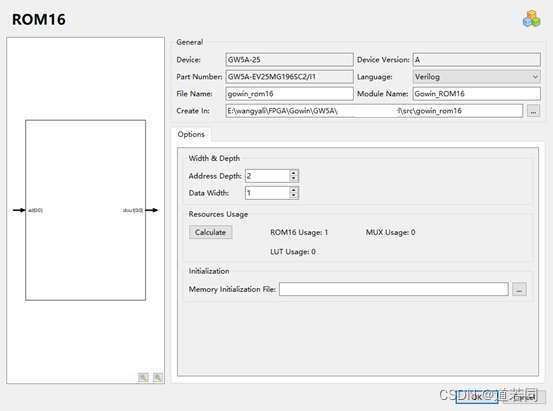

知识点4:高云FPGA配置界面

知识点5:不同产家的FPGA的替代

不同厂家的FPGA如果封装一致则,引脚编号是一致的。比如xilinx的XC6SLX16-3CPG196I和高云的MBGA196S封装为Pin to pin 兼容的,其引脚编号也是完全一致的。当时需要注意的是引脚的功能可能还会存在细小的区别,比如XC6SLX16-3CPG196I的复位引脚RECONFIG是默认内部上拉(低电平复位),而GW5A-EV25MG196SC2/I1是需要外部上拉的。

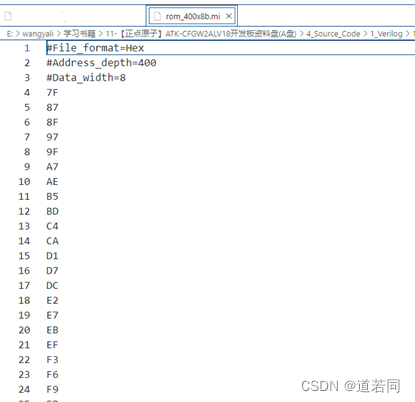

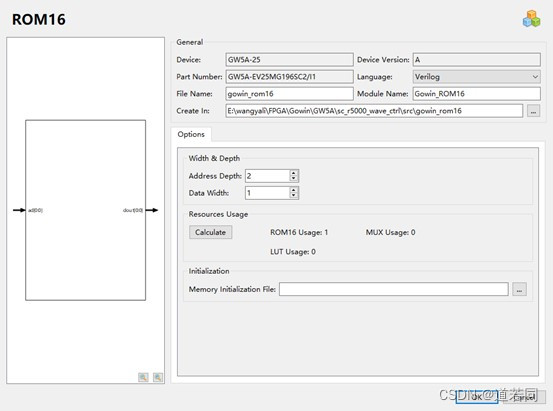

知识点6:高云DRAM IP核-RAM16配置,及使用的初始化文件为.mi文件

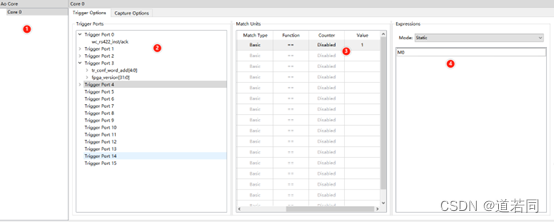

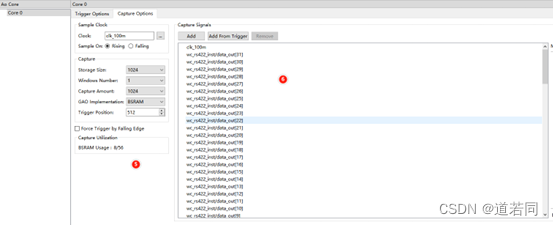

知识点7;在线逻辑分析仪配置

①首先添加一个加载 Standard Mode GAO 即”.rao”文件

配置“.rao”文件有以下7点需要配置,尤其是4点和6点(容易忘记)。

知识点8:高云Modelsim仿真注意事项

①按照视频进行配置会出现下面一个Error导致无法仿真

Error:(vopt-7052)D:/Program/Gowin/Gowin_V1.9.8.01/IDE/simlib/gw1n/prim_sim.v(*): Failed to find 'GSR' in hierarchical name '/GSR/GSRO'.

解决方法:

在Testbench中例化如下全局复位模块,原因是高云仿真库中调用了此模块:

GSR GSR(

.GSRI(1'b1)

);

详细仿真过程可以参考文章:高云FPGA系列教程(3):基本IP原语使用和仿真(https://blog.51cto.com/u_15468736/5979151)

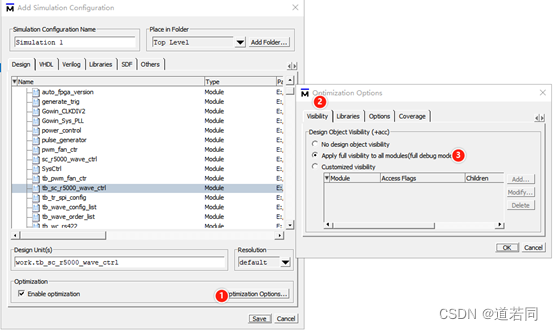

②进行仿真配置过程如下图,在进行仿真配置(鼠标右键--Add to Project--Simulation Configuration )的过程中有2个点是容易忘记的,在此提醒。一是添加仿真库、二是设置变量的权限。

4283

4283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?