目录

32.14.1 Source Event Flag Registers, Group x

32.14.2 Channel Event Flag Registers, Group x

32.14.3 Result Event Flag Registers, Group x

32.14.4 Global Event Flag Registers

32.14.5 Software Activation of Service Requests, Group x

32.14.6 Service Requests for Fast Compare Channels

32.2、概述

1:ADC组

主组ADC 提供8路输出 提供大约最少0.5us的转换时间。(1120页)

次组ADC 提供16路输出,需要比次主更长的采样时间。

快速比较组,每组提供一个专用的输入通道,提供大约200ns的比较时间。

2.转换模式和请求源

模拟数字转换可以通过三个请求源请求,并可以在几种转换模式下执行,请求源可以通过可配置的优先级并发启用。

固定通道转换(单次或连续):请求源请求转换一个可选通道(一次或重复)。

通道序列转换(单次或连续)请求源请求多达8/16(主/次组)任意可选通道的转换序列(一次或重复)。

可用的请求源可以同时使用转换模式,即可以同时启用不同模式的转换。每个源可以单独启用,并且可以由外部事件触发,例如PWM或定时器信号的边缘,或引脚转换。

3.请求源控制

由于可以同时启用所有请求源,因此当不同的请求源请求时,分为两种转换模式:

1.cancel- injection -repeat模式:具有较高优先级的请求可以取消正在运行的低优先级转换。

2.wait-for-start模式:在当前正在运行的转换之后立即进行转换。

某些通道也可以与其他ADC内核同步,因此可以并行转换多个信号。

1.输入通道选择

模拟输入多路复用器选择一个可用的模拟输入(CH0 - CHx)进行转换。三个源可以选择线性序列、任意序列或特定通道。这些源的优先级可以配置。(由于引脚的限制,并非所有的模拟输入通道都必须在所有封装中可用。参考特定于产品的附录中的实现描述)。

2.转换控制

转换参数,如采样相位持续时间或转换模式(降噪)可以配置为4个输入类(2个组特定类,2个全局类)。每个通道可以单独分配给这些输入类之一。

每个通道可以选择标准参考电压或备用参考电压(限制参见产品特定附录)。

因此,输入通道可以根据连接到ADC的传感器(或其他模拟源)的类型进行调整。

如果选择,该单元还控制内置多路复用器和外部模拟多路复用器。

3.模拟数字转换

所选输入通道通过首先对所选输入上的电压进行采样然后产生结果位来转换为数字值。

组的采样保持单元连接到SAR转换器。该转换器为采样信号生成数字结果值。

4.结果处理

每个模拟输入通道的转换结果可定向到16个组特定结果寄存器中的一个和一个存储在那里的全局结果寄存器。结果寄存器可以由一组通道使用,也可以由单个通道使用。

等待读取模式通过阻塞转换,直到读取前一个结果,从而避免由于结果覆盖而导致的数据丢失。

数据缩减(例如用于数字抗混叠滤波)可以在发出服务请求之前自动添加多达16个转换结果。

或者,可以启用FIR或IIR滤波器,在将转换结果发送到结果寄存器(可用于2个寄存器)之前对其进行预处理。

此外,可以将结果寄存器连接起来以构建FIFO结构,该结构可以存储许多转换结果,而不会覆盖先前的数据。这增加了从ADC检索转换数据时允许的CPU延迟。

可以在生成结果时自动确定并存储一系列转换的最小值或最大值。

5.服务请求产生

几个ADC事件可以向CPU或DMA发出服务请求:

“源事件指示相应请求源中转换序列的完成。此事件可用于触发新序列的设置。

通道事件表示某个通道的转换完成。这可以与限制检查相结合,因此只有当结果在定义的值范围内时才会生成中断。

结果事件表明在相应的结果寄存器中有新的结果数据可用。当数据约简模式为active时,只有经过完整的累积顺序才会产生事件。

每个事件可以分配给八个服务请求节点中的一个。这允许根据应用程序的需求对请求进行分组。

6.快速比较通道

专用的快速比较通道支持不需要精确的转换结果,而只是指示输入信号是否高于/低于给定阈值(例如峰值保持操作)的应用。比较需要大约200 ns。结果可以通过边界标志控制输出信号。

比较参考值可以由软件编写,也可以由斜坡发生器生成,或者可以由另一个模拟输入通道提供。

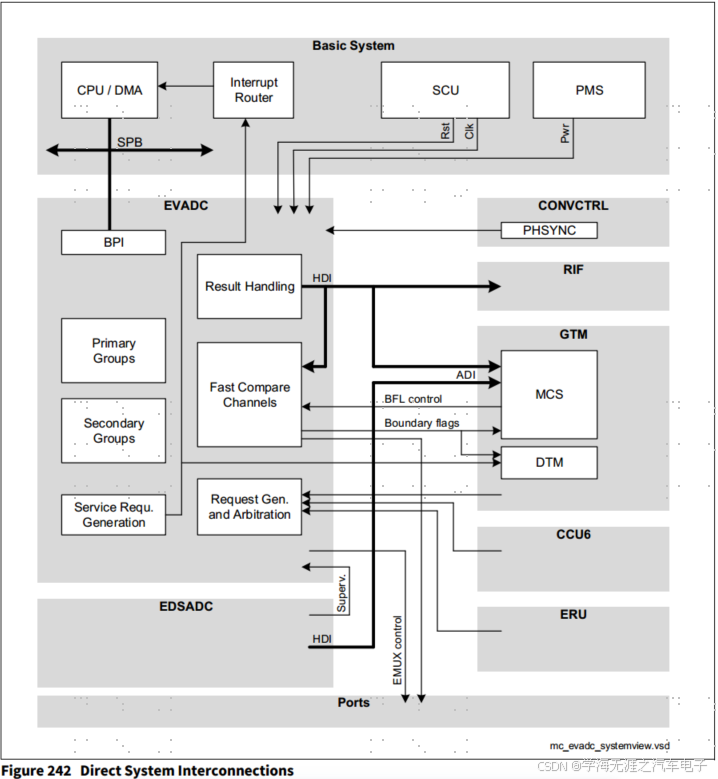

7.系统集成和通信

32.3、通用功能配置

可以为每个通道、源或组单独配置几个参数,也可以对所有ADC集群有效。这些参数使EVADC的功能适应实际应用的要求(参见第32.3.5节)。

32.3.1修改配置

| 配置 | 含义 |

| 通道属性(GxCHCTRy, GxICLASSi, GLOBICLASSi, GxALIAS) | 这些属性用于下一个要启动的转换,因此设置可能不一致。只有在没有安排相应通道的转换时才更改配置。 |

| 服务请求节点指针 (GxSEVNP, GxCEVNPi, GxREVNPi, GLOBEVNP) | 事件与服务请求输出的关联可能不明确。 确保在切换指针时不生成任何事件。 |

| 边界值(GxBOUND, GLOBBOUND) | 限制带与转换结果的关联可能不清楚。 仅在未生成相应结果时更改限制。 |

| 快速比较通道(FCzFCM、FCzFCHYST、FCzFCCTRL、FCzFCBFL, BFS除外) | 由于比较操作在大多数情况下是不断触发的,因此动态更改配置可能会导致意外的中间状态,例如错误的比较级别或遗漏的输出信号。 建议在重新配置时停止通道。 |

| 模拟控制(GxANCFG) | 可能会破坏当前的转换,导致错误的结果。 仅在不运行转换时进行更改。 |

| 基本配置(GLOBCFG) | 操作过程中更改基本配置参数可能导致故障或死锁。仅在关闭所有组时更改配置 |

| 仲裁器配置(GxARBPR) | 在操作过程中改变优先级等可能导致意外的转换序列。仅更改非活动请求队列的配置。 |

| 请求源控制(GxQCTRLi, GxQMRi, GxREQTMi GxTRCTR COV除外) | 修改触发信号的源和方式可能会产生非预期的触发事件。 仅在请求队列处于非活动状态时更改配置。 |

| 结果生成(GxRCRy, GLOBRCR) | 结果生成属性控制如何评估新结果。更改后的配置可能需要一些时间才能生效。 仅更改当前应用程序不针对的寄存器的配置。 |

| 外部多路复用控制(GxEMUXCTR, GxEMUXCS, EMUXSEL) | 操作期间的修改可能导致外部多路复用器控制中的不一致转换序列或中间转换。 仅在各自的组处于非活动状态时更改。 例外:子通道以稳定模式更新。 只有在所有组都处于非活动状态时才更改EMUXSEL。 |

| 同步转换 (GxSYNCTR) | 更改同步组的配置可能导致同步组内的设置不一致。 仅在所有涉及的转换器组处于非活动状态时更改同步组的设置 |

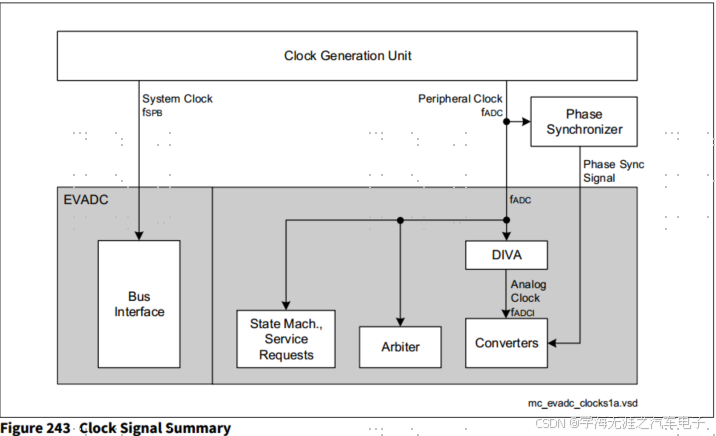

32.3.5通用时钟方案与控制

EVADC与外围时钟信号(fADC)一起工作。这个时钟信号控制所有逻辑块的所有功能,并决定整体定时。转换器的操作与模拟时钟fADCI(见下图)。模拟时钟是基于模拟相位同步器。相位同步器定义转换的初始时钟脉冲。这使模拟系统中的干扰最小化。然后在不引用相位同步器的情况下执行已启动的转换。这确保了应并联运行的转换器的确定性行为。(EVADC评估相位同步器信号的电平。在同步模式下,它将在相位同步器信号高时工作。在不同步模式下(GLOBCFG。USC = 1),转换是独立于相位同步器信号启动的。为了正常运行,在变换器空闲时,只更改相位同步器的配置。)

总线接口使用系统时钟fSPB时钟。

注意:为了保证EVADC时钟域之间的正常同步,外设时钟不能比总线时钟慢,即fADC >= fSPB。

全局配置

全局配置寄存器GLOBCFG提供对所有转换器有效的全局控制和配置选项。

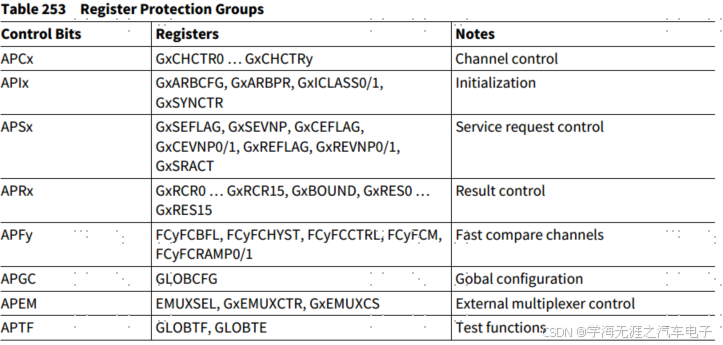

32.3.6 寄存器访问控制

提供了几种保护方案来防止对EVADC控制位域的非预期写访问。

“EVADC的寄存器由寄存器ACCEN0配置的通用访问控制机制保护。

“一个特定的寄存器访问控制方案提供了一个通用的保护方案,防止寄存器内容意外损坏。寄存器ACCPROT0/1/2允许对几组寄存器的写访问进行限制。要保护的寄存器可以由用户选择。表253列出了属于每个寄存器组的寄存器。

注册ACCPROT0/1/2本身受到安全Endinit功能的保护。

寄存器内的位域组也可以由一个相关的写控制位来保护。这个写控制位(xxWC)必须用1和对预期位域的写访问一起写。

访问保护寄存器0控制对初始化寄存器和通道控制寄存器的写访问。控制对初始化寄存器和通道控制寄存器的写访问。

访问保护寄存器1控制对结果寄存器和服务请求控制寄存器的写访问。控制对结果寄存器和服务请求控制寄存器的写访问。位场APR或APS的每一位控制相关的转换器组。

访问保护寄存器2控制对快速比较通道寄存器和全局控制寄存器的写访问。每个位场APF控制相关的快速比较通道。

32.4模拟模块激活与控制

EVADC的模拟转换器是由所选输入电压产生数字结果值的功能模块。它在运行过程中产生永久电流,可以在转换之间停用,以减少消耗的总能量。

注意:复位后模拟转换器关闭。在触发涉及转换器的任何操作之前,必须启用它们。

转换的准确性是通过执行启动校准(第25页的“校准”)来建立的。

32.4.1模拟转换器控制

如果应用程序不需要转换器的永久活动,它可以间歇性地禁用该转换器以节省能源。这可以在软件控制下或自动完成。

操作模式由位域GxARBCFG (x=0-11)决定。

- " ANONS = 11B: 正常操作模式 转换是激活的,转换立即开始。初始沉降后不需要唤醒时间(见下面的注释)。

- ANONS = 10B:快速待机模式在不需要任何活动的情况下,转换器进入功率降低模式。当请求转换时,它会自动返回到操作模式。快速待机模式降低了ADC电源的整体功耗。需要标准唤醒时间(见下文)。

- " ANONS = 01B:慢待机模式转换器进入省电模式,而不需要任何活动。当请求转换时,它会自动返回到操作模式。慢速待机模式使ADC电源的总功耗最低。需要延长唤醒时间(见下文)。

- ANONS = 00B:转换器关闭(复位后默认)转换器本身关闭。此外,将数字逻辑块设置为其初始状态。在开始转换之前,请选择ANONS的活动模式。

模拟下电唤醒时间

当转换器被激活时,它需要一定的唤醒时间(取决于操作模式)才能正确执行转换。这个唤醒时间可以通过将其添加到预期的采样时间中来确定。

标准唤醒时间约为1µs,延长唤醒时间约为5µs。

具体数字可在相应的数据表中找到。

注意:在初始启用转换器后,还需要延长唤醒时间。

32.4.2 模拟信号缓冲

在工作过程中,变换器电容必须多次充放电。在采样阶段,它从选定的信号输入充电,在转换阶段,它从选定的参考充电。

通过从电源电压中提取一部分所需电荷来卸载各自的模拟输入,从而支持这两个相位。

模拟输入的缓冲器

当使能时,模拟输入缓冲器将所选模拟输入信号增强一段时间。通过寄存器GxICLASSi (i=0-1;x=0-11) / GLOBICLASSi (i=0-1)中的位域AIPS/AIPE或寄存器FCxFCCTRL (x=0-7)中的位域AIPF,可以使输入缓冲区处于活动状态的时间适应配置的采样时间。输入预充时间可配置为fADC的8、16或32个时钟。

在设定的缓冲时间之后,直接从选定的输入继续采样。剩余的直接采样时间必须覆盖指定的最小采样时间(数据表),即编程采样时间必须覆盖缓冲采样和直接采样两个阶段。数据表中指定的采样时间考虑200ns的缓冲采样时间,这意味着输入预充电时间必须配置为32个fADC时钟。当输入预充电时间低于200 ns时,模拟输入的电荷消耗相应增加。

当模拟输入缓冲区被激活时(在寄存器GxANCFG中BE = 1 (x=0-11)),需要一定的设置时间才能正确执行转换。

输入缓冲器设置时间约为1µs。

具体数字可在相应的数据表中找到。

预充参考输入

当使能时,预充特性在转换过程中对电容器进行一段时间的充电。之后,电容器连接到选定的参考电压,以实现最大的精度。这减少了从参考中提取的电荷(值见数据表)。

参考预充由寄存器GxANCFG (x=0-11)或FCxFCCTRL (x=0-7)中的位RPE = 1控制。清除位RPE将禁用参考预充。复位后,启用预充功能。

32.4.3备选参考选择

EVADC控制功能允许为每个通道选择一个备用参考。这个参考信号取自一个组的通道0。参考源由通道控制寄存器中的位REFSEL选择,因此可以为每个输入单独配置。

34.4.4 校准

校准自动补偿由工艺变化和老化引起的偏差。这确保了整个操作时间的精确结果。

所有启用的转换器(快速比较通道除外)复位后需要进行一次初始启动校准。所有转换器必须启用(ANONS = 11B)。通过将1写入寄存器GLOBCFG中的位sual来全局启动校准。

启动校准阶段的持续时间取决于编程,请参阅第86页的“转换时间”。

注意:在启动校准期间,所有转换器必须处于非活动状态。重置后,情况就是这样。只有在校准完成后才开始转换(由位CAL = 0表示)。

之后,如果不禁用,校准周期可以补偿漂移的外部参数的影响。转换器本身不需要进一步校准。

后校准步骤可以附加到每个转换。由于老化引起的变化非常缓慢,并且后校准使电容器放电,因此对于当前版本的转换器,后校准应禁用(大多数应用程序定期重新启动,因此也要重复启动校准)。

这也提供了最高的转换率(参见第88页的表259“转换时间概述”)。

34.4.5降噪方法

模拟输入信号几乎总是包含一定量的噪声。这可以在传感器本身内产生,也可以沿着信号路径添加到转换器输入。

由于模数转换器集成在一个微控制器中,微控制器的数字块产生的一些噪声也可能影响转换器的工作。

EVADC提供了几种方法来衰减影响其工作和性能的噪声成分。

具体详情参考数据手册1142页。

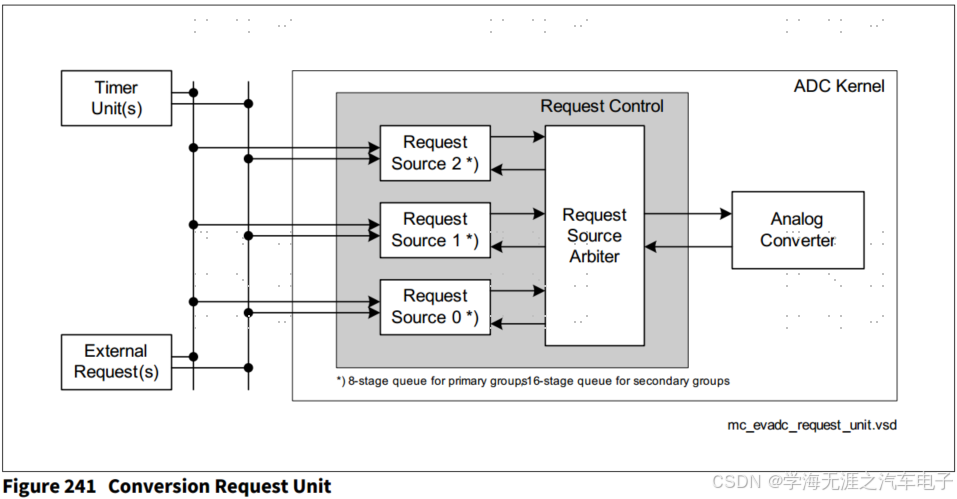

32.5 生成转换请求

组的转换请求单元自主地处理转换请求的生成。三个请求源可以生成模拟信道转换的请求。仲裁器解析并发请求并选择接下来要转换的通道。

在触发事件发生时,请求源请求转换某个模拟输入通道或通道序列。

- 软件触发器直接激活相应的请求源。

- 自定时触发器由各自源的请求计时器生成。

- 外部触发器将请求源激活与外部事件同步,例如来自产生PWM信号的定时器或来自端口引脚的触发脉冲。

应用软件选择触发类型和源、要转换的通道和请求源优先级。请求源也可以由软件直接激活,而不需要外部触发器。

仲裁器定期扫描请求源以查找挂起的转换请求,并选择具有最高优先级的转换请求。然后将此转换请求转发给转换器,以启动所请求通道的采样和转换。

每个请求源可以在单次或连续模式下运行:

- 在单发模式下,程序转换(序列)被触发后要求一次。必须再次触发后续的转换(序列)。

- 在连续模式下,程序转换(序列)在触发一次后自动重复请求。

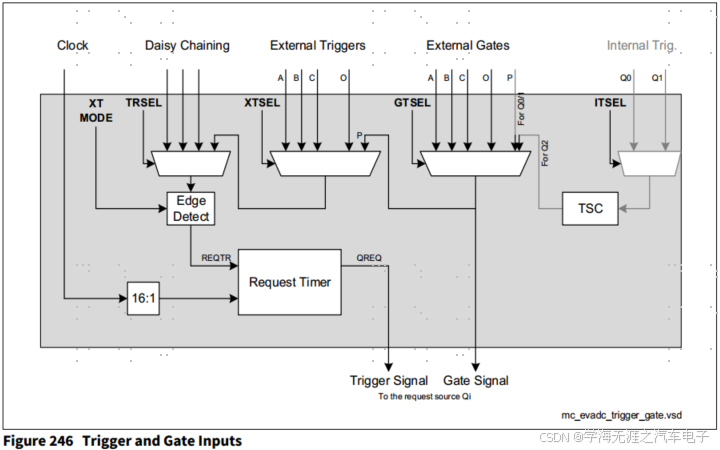

对于组的每个请求源,外部触发器由15个可选触发器中的一个(REQTRx[O: a])输入和16个可选门控中的一个生成(REQGTx[P: a])输入。具体产品的附录中列出了可用的触发信号。

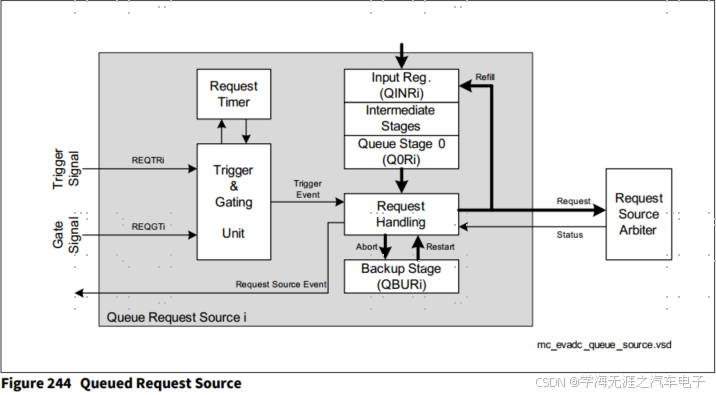

排队请求源的属性

排队请求源提供了构建队列的几个缓冲阶段,并且可以处理特定于应用程序的任意转换序列,直至队列大小。

主通道配置8级队列,次通道配置16级队列。因此,每个队列可以处理与相应组关联的所有通道。

这个序列的通道号可以自由编程。此外,还支持序列中同一通道的多个转换。程序序列存储在队列缓冲区中(基于FIFO机制)。请求的通道号通过队列输入,而队列阶段0定义接下来要转换的通道。每个条目可以执行一次,也可以自动重新加载以形成连续重复的序列。

只有在队列阶段0中存储了有效条目时,才会向请求源仲裁器发出转换请求。

如果仲裁器由于更高优先级的请求而终止由排队请求源触发的转换,则相应的转换参数将自动保存在备份阶段。这确保了被终止的转换不会丢失,而是会参与下一个仲裁步骤(在阶段0之前)。

所选的门控输入可以用作触发信号(REQTRxP)。

注意:保存在备份阶段的转换请求将在其优先级允许的情况下立即执行,即使原始转换请求正在等待触发事件

触发和门控单元从选定的内部或外部(ADC外部)触发和门控信号产生触发事件。例如,定时器单元可以发出请求信号来同步转换到PWM事件。

触发事件启动一个排队序列,可以通过软件或通过选定的硬件触发器生成。触发事件的发生由位QSRx.EV表示。当相应的转换开始或写入位QMRx.CEV时,此标志被清除。

序列是通过将转换请求输入队列寄存器(GxQINRi (i=0-2;x=0-11))来定义的。

每个条目选择要转换的通道,并可以启用外部触发器,生成中断和自动重新填充(即在转换后将该条目复制到队列的顶部)。条目存储在队列缓冲区阶段中。

阶段0的内容(GxQ0Ri (i=0-2;x=0-11))选择接下来要转换的通道。当请求的转换开始时,此队列阶段的内容将失效并复制到备份阶段。然后可以处理下一个队列条目(如果可用)。

不能直接修改队列阶段的内容,只能通过写入队列输入或刷新队列来修改。

队列的当前状态显示在寄存器GxQSRi中(i=0-2;x=0-11)。

如果所有队列条目都选择了自动重新填充,则可以重复定义的转换序列而无需重新编程。

32.5.1 排队源操作

通过执行以下操作配置排队请求源:

- “通过将条目写入队列输入GxQINRi (i=0-2;x=0-11)来定义序列。在启用请求源之前初始化完整的序列,因为启用了重新填充功能后,不允许软件写入QINRx。

- 如果需要硬件触发或门控,通过编程GxQCTRLi (i=0-2;x=0-11)选择适当的触发和门控输入和适当的转换。通过在寄存器GxQMRi (i=0-2;x=011)中编程位场ENGT,使能触发器并选择门控模式。

- 启用相应的仲裁器输入以接受来自排队源的转换请求(参见寄存器GxARBPR (x=0-11))

通过生成触发事件启动队列序列:

- “如果硬件触发器被选中并启用,在选择的输入信号(例如,从定时器或输入引脚)处生成配置的转换。

- 通过设置GxQMRi.Trev = 1生成软件触发事件。

- "向空队列的队列输入写入一个新条目。这导致一个(新的)有效队列条目被转发到队列阶段0,并启动一个转换请求(如果GxQMRi启用了)。而无需等待外部触发)。

如果重新填充机制被激活,已处理的条目将自动重新加载到队列中。这将永久地重复相应的序列(autoscan)。

在这种情况下,不要在队列源运行时写入队列输入。

对完全填满的队列的写操作将被忽略。

通过执行以下操作之一来停止或中止正在进行的队列序列:

- “如果启用了外部门控,将门控信号切换到定义的非活动级别。这不会修改队列条目,而只是阻止向仲裁器发出转换请求。

- "在仲裁器中禁用相应的仲裁器输入。这不会修改队列条目,而只是阻止仲裁器接受来自请求处理块的请求。

- “禁用排队源:

-通过清除位域ENGT = 00B来阻止转换请求到仲裁器。

-通过设置位GxQMRi.CLRV = 1使下一个等待队列条目无效。。

-如果备份阶段包含有效条目,则此条目无效,否则阶段0无效。

-通过设置位GxQMRi.Flush = 1从队列中删除所有条目。

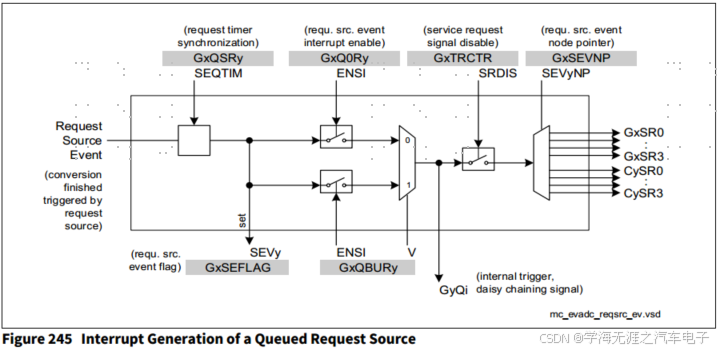

队列请求源事件和服务请求

当转换完成且请求计时器已过期时,将发生排队源的请求源事件。源事件服务请求可以根据图245所示的结构基于请求源事件生成。如果检测到请求源事件,它将在寄存器GxSEFLAG (x=0-11)中设置相应的指示标志。这些标志也可以通过向相应的位位置写入1来设置,而写入0则不起作用。通过向寄存器GxSEFCLR (x=0-11)中的相应位位置写入1,SW可以清除指示标志。

中断使能位在正常顺序转换时从阶段0取,在中断后重复转换时从备份阶段取。

由请求源事件中断节点指针位域在寄存器 GxSEVNP(x = 0 - 11)中选择的服务请求输出线 SRx,每当检测到相关的请求源事件时(并且分别由 GxQ0R0.ENSI 或 GxQBUR0.ENSI 启用),或者当在寄存器 GxSEFLAG(x = 0 - 11)中的相关位位置写入 1 时(此写入操作模拟请求源事件),就会被激活。

32.5.2触发器和门信号

每个源都可以由可选择的触发器启动,并且 / 或者其操作可以由门控信号从外部进行控制。这些触发 / 门控信号可以从一组输入中单独选择。实际的信号源在产品特定的附录中进行了描述。

通过使用外部门控输入来生成触发信号,可提供更高的灵活性。将选定的门控输入内部连接到最高的触发输入(GxREQTRyP,XTSEL = 1111B)可访问外部门控输入。

此外,队列源 Q2 也可以由同一组的其他请求源触发。选定的内部触发信号在内部连接到 Q2 外部门控输入的最高位(GxREQGT2P,GTSEL = 1111B)。

菊花链连接相邻的组,用于包含多个多路复用器的序列。这样,单个外部触发事件可以触发扩展序列。

另请参阅第 36 页的 “通过串联实现扩展转换序列”。

转换序列的自定时执行

内置的请求定时器可以在可配置的间隔内请求程序序列的转换。16:1的预分频器产生0.1µs的时基(对于fADC = 160 MHz)。10位定时器可创建高达102.4µs的间隔。

定时器由触发事件启动(由硬件或软件生成),当队列运行为空时,它不会重新启动。当请求计时器运行时,附加的触发器输入将被忽略。

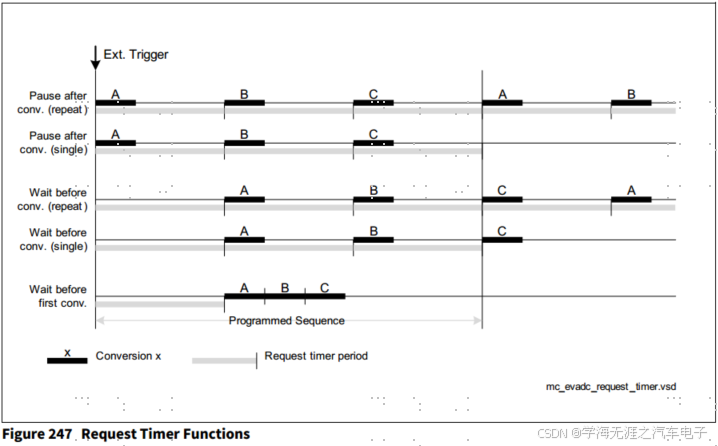

可以选择几种操作模式:

“每次转换后暂停”触发事件后,立即请求第一次转换。在请求计时器计算了配置的时钟周期数之后,请求每个后续转换。

“在第一次转换之前等待”触发事件后,请求计时器启动。在请求计时器计算了配置的时钟周期数之后,请求转换序列。计时器不再产生进一步的延迟。

“在每次转换之前等待”触发事件后,请求计时器启动。在请求计时器计算了配置的时钟周期数之后,请求序列的每次转换。

注意:请求计时器为请求源生成触发信号。请求源中的转换命令确定转换是否等待此触发器。

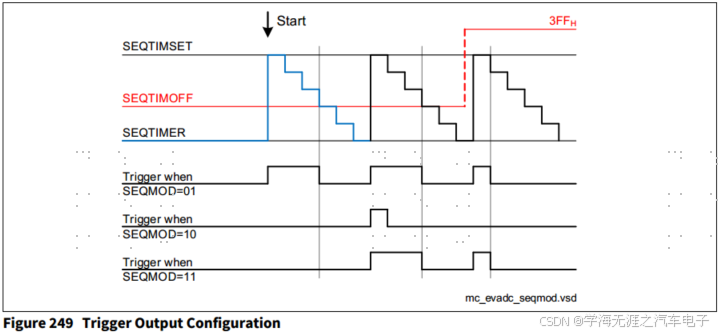

图247中的第一个示例假设所有命令(A、B、C)都在等待触发器,最后一个示例假设仅等待第一个命令(A)的触发器。当请求定时器处于活动状态时(即 GxREQTMi.SEQMOD ≠ 00B),服务请求信号与定时器同步。源事件仅在配置的定时器周期结束时发出信号。这确保了在使用多个组连接序列的情况下具有相等的转换步骤。对于此功能,必须启用定时器,并且配置的周期必须足够长,以便在相应的转换后结束。

当请求定时器处于活动状态(即 GxREQTMi.SEQMOD ≠ 00B)时,服务请求信号与定时器同步。只有在配置的定时器周期结束时才会发出源事件信号。这样在使用多个组连接序列的情况下,能够确保转换步骤相等。要实现此功能,必须启用定时器,并且配置的周期必须足够长,以便在相应的转换完成后结束。

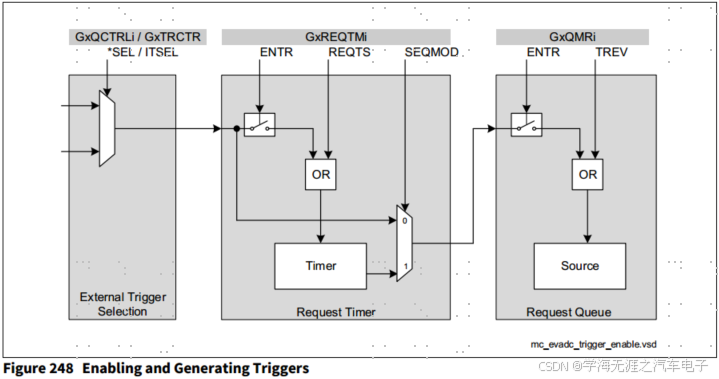

内部控制和外部触发器

触发事件可以通过在所选硬件触发信号上的转换或通过软件生成。在后一种情况下,可以将外部触发器排除在生成触发器事件之外。

当启用请求计时器时,所选的外部触发信号控制计时器本身,而相应请求队列的触发信号由请求计时器在本地生成。

下图总结了接合块的控制路径。

触发信号的控制

触发信号通常是一个脉冲,它的形状可以通过写一个适当的值到位场SEQTIMOFF来控制。这对于生成定时器模式的序言时间很有用,参见第112页的“等距采样”。

32.5.3通过连接扩展转换序列

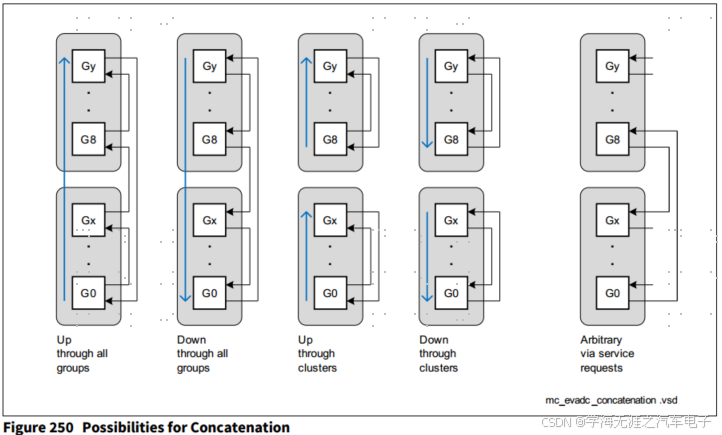

请求源可以自动处理多达8或16个转换的序列。如果需要用单个触发事件启动较长的序列,则可以将多个请求源连接起来,以便一个源触发另一个源。

有三种可能的连接模式:

- 在一个组内:源2 (Q2)可以由同一组的另一个请求源在内部触发。在配置的序列被Q0或Q1转换后,直接触发Q2(参见图246中的“内部触发”)。这对于扩展单个队列可以处理的序列或在一系列应用程序转换之后自动执行测试转换(请参阅Q2的其他功能)非常有用。如果扩展序列覆盖的信道比给定组的各自多路复用器的可用信道多,则请求源也可以由相邻组的源事件触发。

- 菊花链:可以建立在一个集群内或跨越所有组,测序可以在两个方向上完成,环绕是可能的。这些连接位于模块内,不会造成任何同步延迟。这对于配置具有多个通道的扩展序列非常有用。

- 多组:通过使用另一个组的服务请求信号,也可以在组之间建立触发器。这对于使用来自不同组的通道配置任意序列非常有用。

建立菊花链连接

组可以在一个可配置的菊花链中连接。每个组选择其前身组的源事件作为触发器输入。

举例:从组连接9-10-11-8:

“从 G9 触发输入(上升沿)到 G10:G10QCTRLi.TRSEL = 01B,G10QCTRLi.XTMODE = 10B,G10QMRi.ENTR = 1,G10QINRi.EXTR = 1。

“从 G10 触发输入(上升沿)到 G11:G11QCTRLi.TRSEL = 01B,G11QCTRLi.XTMODE = 10B,G11QMRi.ENTR = 1,G11QINRi.EXTR = 1。

“从 G11 触发输入(上升沿)到 G8:G8QCTRLi.TRSEL = 10B,G8QCTRLi.XTMODE = 10B,G8QMRi.ENTR = 1,G8QINRi.EXTR = 1。

“G9 的触发输出(无服务请求):G9QINRi.ENSI = 1,G9SEVNP.SEViNP = 1111B。

“G10 的触发输出(无服务请求):G10QINRi.ENSI = 1,G10SEVNP.SEViNP = 1111B。

“G11 的触发输出(无服务请求):G11QINRi.ENSI = 1,G11SEVNP.SEViNP = 1111B。

建立多组连接

组可以通过服务请求线进行连接(请参阅产品特定的附录)。前一组将源事件路由到特定的服务请求线,后一组选择此服务请求线作为触发输入。

例如:将组 1 的队列 0 连接到组 3 的队列 0:

“生成源事件:G1QINR0.ENSI = 1。

“将源事件路由到服务请求输出:G1SEVNP.SEV0NP = 0101B(公共服务请求 C1SR1)。

“选择服务请求作为触发输入:G3QCTRL0.XTSEL = 1110B,G3QCTRL0.XTMODE = 10B

“激活后一组的触发:G3QMR0.ENTR = 1,G3QINR0.EXTR = 1。

这种配置方式允许通过服务请求线将不同的组连接起来,实现更加复杂的操作序列。通过设置特定的寄存器值,可以控制源事件的生成、路由以及触发输入的选择,从而实现多组之间的协同工作。这样的连接方式在需要处理多个相关任务或实现复杂的系统功能时非常有用。

注意:不要将其他事件路由到选定的服务请求线。

32.5.4队列请求源控制寄存器

下面的一组寄存器提供了对队列请求源操作的初始化和控制。

注意:对超过组最大可用通道的通道号的请求将被视为对通道0的请求。对更高的通道号使用ALIAS特性(参见第32.7.2节)。

与其他源Q0和Q1相比,队列请求源Q2提供了两个增强功能:

- Internal TriggersQ2:也可以由同一组的请求源Q0/Q1内部触发(参见GxTRCTR (x=0-11))。

- TestfunctionsQ2:可用于自动控制面向安全的测试转换序列。因此,它提供了额外的控制位域CDSEL, CDEN, MDPU, MDPD, PDD,这些在Q0/Q1中是不可用的。

队列1源控制器寄存器,组x

队列源的控制寄存器选择外部门和/或触发信号。还可以选择来自其他组的触发器,以允许组的连接来执行扩展的转换序列。写控制位允许通过简单的写访问对每个功能进行单独控制。

队列i状态寄存器,组x

队列状态寄存器指示排队源的当前状态。填充级别和空信息指的是队列中间阶段(如果可用)和队列寄存器0。存储在备份阶段的终止转换不会由这些位表示(因此,请参阅QBURx.V)。

队列i输入寄存器,组x

队列输入寄存器是排队请求源的转换请求的入口点。

队列i备份寄存器,组x

队列备份寄存器监视已终止的排队请求的状态。

队列i请求。定时器模式, x组

请求定时器模式寄存器配置特定于源的请求定时器的操作模式。

队列i请求。定时器状态表, x组

请求定时器状态寄存器返回特定于源的请求定时器的当前值。

触发控制寄存器,组x

对于排队请求源Q2,触发控制寄存器配置触发序列计数器和内部触发源。

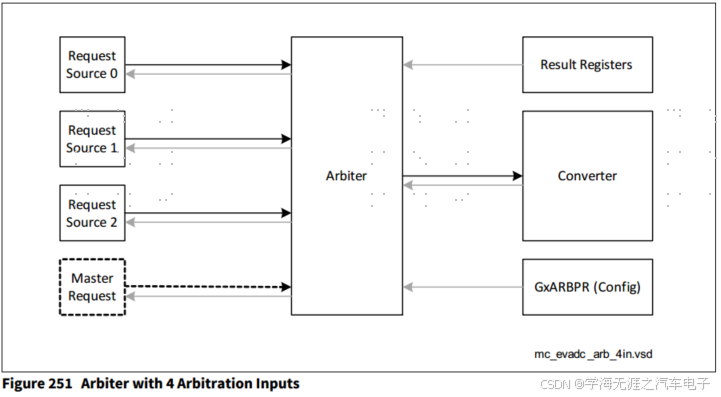

32.6请求源仲裁

请求源仲裁器扫描请求源以查找待处理的转换请求。每个请求源都连接到仲裁器的特定输入。

每个请求源的优先级可通过寄存器 GxARBPR(x = 0 - 11)由用户配置,因此在多个源同时发出请求的情况下,仲裁器可以根据应用需求选择下一个要转换的通道。同步源始终具有比所有其他源更高的优先级。

复位后,所有输入都被禁用,必须启用(寄存器 GxARBPR(x = 0 - 11))才能参与仲裁过程。

仲裁器确定最高优先级的转换请求。如果此请求具有足够的优先级,则相应的转换将开始。

以下是可用的请求源:

- “输入 0:排队请求源 Q0,可任意顺序的 8/16 级序列。

- “输入 1:排队请求源 Q1,可任意顺序的 8/16 级序列。

- “输入 2:排队请求源 Q2,可任意顺序的 8/16 级序列、组内连接、测试。

- “输入 3:同步源,来自另一个 ADC 主内核的同步转换请求(在同步从内核中始终以最高优先级处理)。

32.6.1仲裁器操作与配置

每个请求源都有一个可配置的优先级(0 =最低,3 =最高),因此仲裁器可以解析来自不同源的并发转换请求。选择具有最高优先级的请求进行转换。

这些优先级可以适应给定应用程序的需求(参见寄存器GxARBPR (x=0-11))。

仲裁器由寄存器GxARBCFG和GxARBPR中的位控制。如果任何转换请求处于活动状态,则在一个时钟周期内做出决定。当没有活动的转换请求时,仲裁器保持空闲状态。

转换开始模式确定对赢得仲裁的转换请求的处理。

为了在转换请求的触发事件(例如由计时器单元或由于外部事件)和相关转换的开始之间实现可重复的反应时间(无抖动的恒定延迟),转换器必须空闲。计时器模式特别支持这一点(参见第112页的“等距采样”)。

仲裁配置 Register, Group x

仲裁配置Register选择仲裁的时间和行为。这里还可以选择一些特定于组的配置。

仲裁优先级寄存器,组x

仲裁优先级寄存器定义请求源的优先级和每个请求源的转换开始方式。

注意:只有当请求源被禁用,并且该源请求的当前正在运行的转换已经完成时,才能更改请求源的优先级和转换启动模式设置。

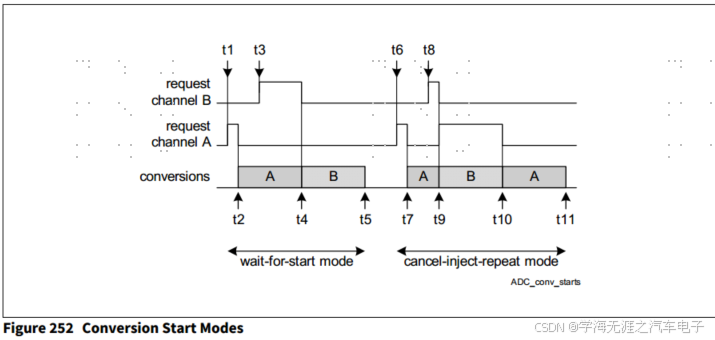

32.6.2转换启动模式

当仲裁者选择了接下来要转换的请求时,该通道的处理取决于转换器的当前活动:

- “转换器当前空闲:仲裁获胜者的转换立即开始。

- 当前转换具有相同或更高的优先级:当前转换完成,仲裁赢家的转换在此之后开始。

- 当前转换具有较低的优先级:该操作是用户可配置的;

—等待启动模式:当前转换完成,待当前转换完成后才启动仲裁仲裁员的转换。这种模式提供 了最大的吞吐量,但是对于高优先级的转换会产生抖动。

图252中的示例:

转换A被请求(t1)并启动(t2)。然后请求转换B (t3),但只有在转换A (t4)完成后才开始。

—Cancel-inject-repeat模式:终止当前的转换,终止后(3个fADC周期)开始仲裁赢家的转换。

被中止的转换请求将在相应的请求源中恢复,并在下一个仲裁步骤中再次参与。这种模式 为高优先级转换提供最小的抖动,但降低了总体吞吐量。

图252中的示例:请求转换A (t6)并启动转换A (t7)。然后请求转换B (t8)并启动转换B (t9), 而转换A被中止但再次请求。转换B完成后(t10),重新启动转换A。

异常:如果两个请求都以相同的结果寄存器为目标并激活了wait-for-read模式(参见章节 32.10.3),当前的转换不能被中止。

转换启动模式可以通过寄存器 GxARBPR(x = 0 - 11)中的位为每个请求源单独编程,并应用于该源请求的所有通道。在这个例子中,通道 A 由一个优先级低于请求转换通道 B 的请求源发出。

被取消的转换在每种情况下都可以自动重复,或者如果被取消则可以丢弃。这是通过相应源的模式寄存器中的位 RPTDIS 为每个源进行选择的。

注意:当外部多路复用器以序列模式运行时,不可能丢弃被取消的转换。在这种情况下,位 RPTDIS 必须为 0。

32.7模拟输入通道配置

对于每个模拟输入通道,可以配置一些参数来控制该通道的转换。通道控制寄存器定义以下参数:

“通道参数:该通道的采样时间和模拟输入预充电选项通过输入类别定义。每个通道可以选择其所在组的两个类别之一或两个全局类别之一。

“参考选择:大多数通道可以选择一个备用参考电压(产品特定附录中标记了例外情况)。

“结果目标:转换结果值存储在特定组的结果寄存器中或全局结果寄存器中。特定组的结果寄存器有多种选择方式:

- 通道参数:该通道的采样时间和模拟输入预充电选项通过输入类别来定义。每个通道可以从其所在组的两个类别之一或者两个全局类别之一中进行选择。

- 参考选择:大多数通道可以选择一个备用参考电压(例外情况在产品特定的附录中进行了标记)。

- 结果目标:转换结果值存储在特定组的结果寄存器或全局结果寄存器中。特定组的结果寄存器可以通过以下几种方式进行选择: -特定于通道的选择,通过寄存器 GxCHCTRy(x = 0 - 7;y = 0 - 7)等中的位域 RESREG 进行选择,此时位域 SRCRESREG = 0000B。-特定于源的选择,通过寄存器 GxQCTRLi(i = 0 - 2;x = 0 - 11)等中的位域 SRCRESREG 进行选择,当位域 SRCRESREG 不等于 0000B 时。-当 SRCRESREG = 0000B 且 RESTGT = 1 时,选择全局结果寄存器。

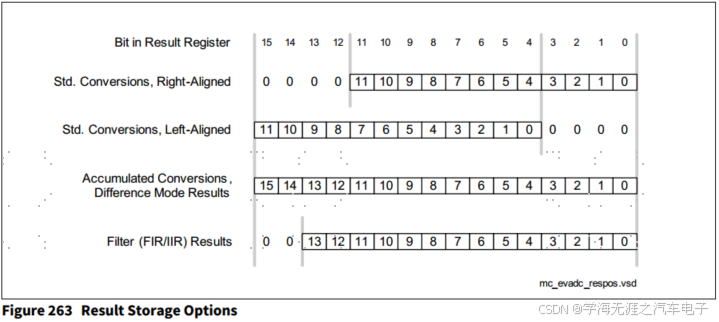

- 结果位置:标准转换的结果值可以左对齐或右对齐存储,其他结果为右对齐存储。全局结果寄存器GLOBRES总是以右对齐的方式存储结果。参见第98页的图263“结果存储选项”。

- 与标准转换(限制检查)相比:只要有新的结果值可用,就可以生成通道事件。通道事件生成可以限制为位于用户可配置频带内部或外部的值。

- 断线检测:此安全功能可以检测到模拟信号源(传感器)的缺失连接。

- 转换的同步:同步转换在几个转换器上同时执行。

别名功能将通道CH0和/或CH1的转换请求重定向到其他通道。

32.7.1通道参数说明

每个模拟输入通道由其相关联的通道控制寄存器配置。

组0,通道0控制寄存器可以为每个通道定义以下特征:“转换类定义转换模式(降噪)和采样时间”通道事件和结果值带的生成,如果使用“结果的目标定义目标寄存器和寄存器内的位置”。

GxCHCTRy (x=0-7;y=0-7)

GxCHCTRy (x=8-11;y=0-15)

以上说明组0-7有8个通道,组8-11有15个通道。

Input Class Register i, Group x

特定于组的输入类寄存器通过通道控制寄存器GxCHCTRy中的位域ICLSEL为任何组的每个通道定义采样时间和数据转换模式。

Input Class Register i, Global

全局输入类寄存器通过通道控制寄存器GxCHCTRy中的位域ICLSEL为各自组的每个通道定义采样时间和数据转换模式。

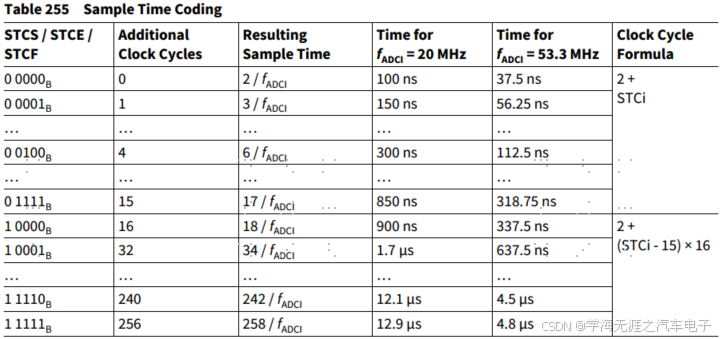

Sample Time Control

采样时间由可配置的采样时钟周期数定义。采样时钟为模拟时钟fADCI。因此,采样时间可以配置为tADCI = 50/37.5/25 ns(对于fADCI = 20/26.7/40 MHz)。

配置的采样时间必须包括输入缓冲时间(如果由位域AIPi选择)和由采样点扩展减去的时间跨度(如果由位域SESPi选择)。

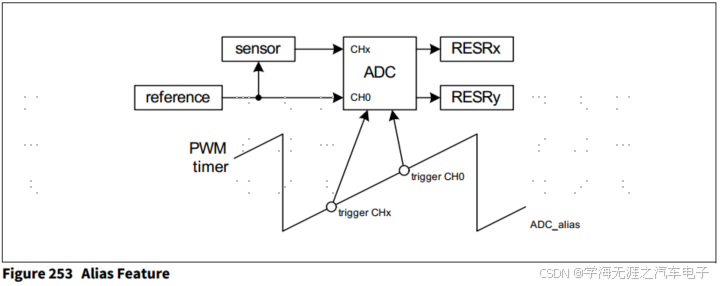

32.7.2 别名特性

别名功能将通道CH0和/或CH1的转换请求重定向到其他通道号。此特性可用于通过独立事件触发相同输入通道的转换,并将转换结果存储在不同的结果寄存器中。

- 同一信号可以测量两次,不需要读出转换结果,避免数据丢失。

- 这允许快速地一个接一个地触发两个转换,并且独立于CPU/DMA服务请求延迟。

- 传感器信号仅连接到一个模拟输入(而不是两个模拟输入)。这在低成本应用中节省了输入引脚,并且在误差计算中只需考虑一个输入的泄漏。

- 即使模拟输入CH0被用作替代参考(见图253),通道CH0的内部触发和数据处理功能也可以使用。

- 两个转换的通道设置可以不同(边界值、服务请求等)。

在典型的低成本交流驱动应用中,仅使用一个通用电流传感器来确定相电流。根据所应用的PWM模式,测量值具有不同的含义,采样点必须精确定位在PWM周期内。图253显示了一个示例,其中传感器信号连接到一个输入通道(CHx),但两个转换被两个不同的通道(CHx和CH0)触发。使用别名功能,对CH0的转换请求导致模拟输入CHx而不是CH0的转换,但考虑到CH0的设置。虽然已经测量了相同的模拟输入(CHx),但转换结果可以从结果寄存器RESx (CHx触发的转换)和RESy (CH0触发的转换)中存储和读出。此外,可以选择、启用或禁用不同的中断或限制边界。

Alias Register, Group x

别名寄存器可以用另一个通道号替换通道CH0和CH1的通道号。重置值禁用此重定向。

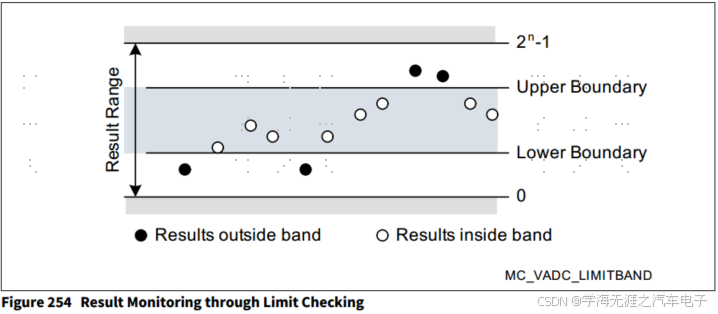

32.7.3 与标准转换的比较(限制检查)

限位检查机构可以自动将每个数字转换结果与上下边界值进行比较。然后,当转换/比较的结果在用户定义的频带内或外时,可以生成通道事件(参见位场CHEVMODE和图254)。

该特性支持自动范围监控,并通过仅在某些预定义条件下发出服务请求来最小化CPU负载。

注意:通道事件也可以为每个结果值生成(忽略频带),或者可以完全抑制通道事件。

比较结果的边界值可以从几个来源中选择(参见寄存器GxCHCTRy)。

当位域BNDSELX = 0000B时,位域BNDSELU和BNDSELL从组特定的边界寄存器GxBOUND (x=0-11)或全局边界寄存器GLOBBOUND中选择有效的上/下边界值。所述组边界寄存器可为各自组的每个通道选择,所述全局边界寄存器可由每个可用通道选择。

否则,比较值从结果寄存器的低12位获取,其中位域BNDSELX选择上边界值(GxRES1…GxRES15),连接的位域BNDSELU||BNDSELL选择下边界值(GxRES0…GxRES15)。

当以下两个条件同时满足时,结果值被认为在定义的频带内:

"该值小于或等于所选的上边界

"该值大于或等于所选的下边界

结果范围也可以分为两个区域:选择下一部分作为有效波段,将下边界设置为最小值(000H),将上边界设置为期望的最大值。

如果要选择上一部分作为有效波段,则将上边界设置为最大值(FFFH),将下边界设置为最低期望值。

Finding Extrema (Peak Detection)

限制检查机制使用标准转换,因此总是可以提供用于比较的实际转换结果。将此与特殊的FIFO模式(参见第99页的“结果FIFO缓冲区”)相结合,只有在结果高于(或低于)阶段的当前值时才更新相应的FIFO阶段,提供通常的转换结果,同时存储转换序列的最高(或最低)结果。对于该操作,必须选择低于标准结果的FIFO阶段作为比较值。模式选择是通过寄存器GxRCRy中的位场FEN完成的。

在开始峰值检测序列之前,在峰值结果寄存器的结果位域中写入一个合理的起始值(例如,0000H查找最大值,0FFFH查找最小值)。

注意:只比较低的12位!因此,建议只使用标准的右对齐转换。

Selecting Compare Values

数字比较操作的值可以从几个来源中选择。单独的GxBOUND寄存器或通用的GLOBBOUND寄存器提供软件定义的比较值。比较值也可以从结果寄存器中获取,结果寄存器可以由构建引用的另一个通道提供。

比较值通过寄存器GxCHCTR中的位域BNDSELL/BNDSELU和BNDSELX来选择。

Boundary Select Register, Group x

本地边界寄存器GxBOUND定义特定于组的边界值。

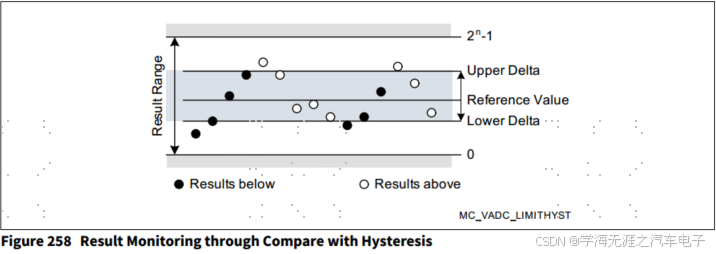

32.8 快速比较通道操作

快速比较通道将输入信号直接与寄存器FCxFCM (x=0-7)中存储在位域FCREF中的参考值进行比较。Delta值定义了迟滞。这个比较返回一个二进制结果(在位FCR中可用),它表明比较的输入电压是高于还是低于给定的参考值。这种比较只需要几个时钟周期,因此允许高采样率。

请求计时器为每个比较操作生成内部比较触发器。触发间隔定义了16…4096个时钟范围内的比较速率(fADC = 160 MHz时0.1…25.6µs)。

注意:根据配置的比较时间间隔(interval >比较时间)选择触发时间间隔。

当输入信号比参考值高(或低)时,可以产生一个通道事件,其中包含一个可以非对称定义的迟滞(见图258)。

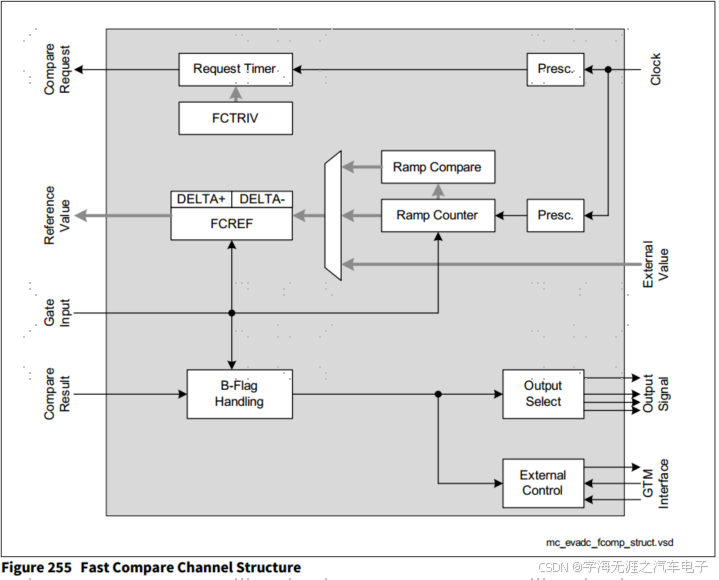

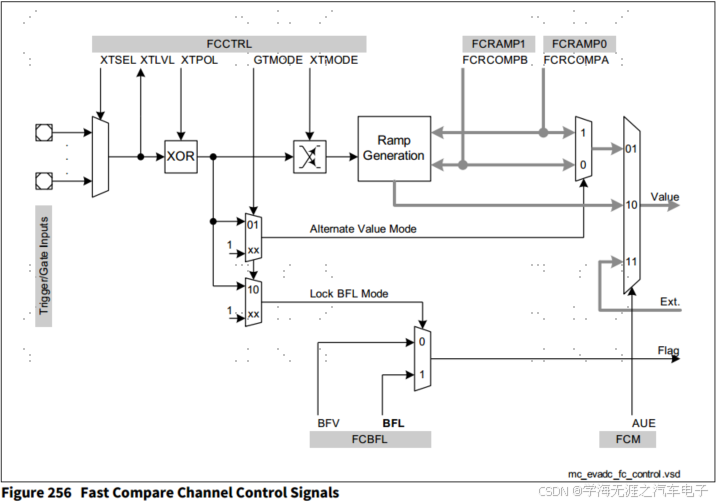

快速比较通道的控制界面针对其特定功能进行了优化。下图总结了可用的控制功能。

32.8.1 峰值保持操作

快速比较通道可以实现硬件控制的峰值保持控制回路,而无需软件支持。要控制的值(如电流)通过模拟输入观察,目标值由参考值给出,边界标志输出控制外部电路(如电源开关)。

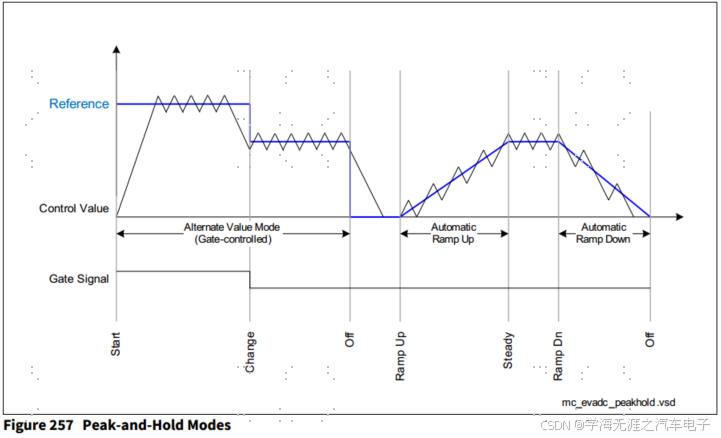

参考值可以从几个来源生成。四种工作模式:

- "软件模式

- "备选值模式

- "斜坡模式

- "外部模式

通过寄存器FCxFCM (x=0-7)中的位场AUE选择预期的工作模式。

软件模式

使用静态参考值,写入寄存器FCxFCM (x=0-7)的位域FCREF。软件可以改变这个参考值来产生被控信号的某种波形(见图257中的“更新”)。

备选值模式

在这种模式下,外部门信号选择两个预定义参考值中的一个。参考值由位场FCRCOMPA和位场FCRCOMPB定义,取决于所选硬件门信号的电平。

当门信号处于活动状态(高电平)时,应用FCRCOMPA中的参考值(FCxFCRAMP0 (x=0-7))。

当门信号处于非活动状态(低)时,应用FCRCOMPB中的参考值(FCxFCRAMP1 (x=0-7))。

斜坡模式

快速比较通道可以自动生成控制信号的斜坡波形。寄存器FCxFCRAMP0 (x=0-7)中的位域FCRCOMPA和寄存器FCxFCRAMP1 (x=0-7)中的位域FCRCOMPB定义了引用的起始值和结束值。Bitfield FCRSTEP定义生成斜坡的速度。

步进宽度定义为(FCRSTEP+1) × 8 / fADC,即50 ns至12.8µs (fADC = 160 MHz)。

这个特性可以在没有软件支持的情况下实现软启动(参见图257中的“上升/下降”)。

定义的斜率也可以表示控制回路一个周期内的自适应阈值。这是通过在门信号的前缘启动坡道计数器来支持的(门变得活跃)。

也可以通过向寄存器FCxFCRAMP0写入一个启动值来自动启动斜坡。

当计数器到达FCRCOMPB或可选地由外部信号触发时,斜坡停止。

见寄存器FCxFCM (x=0-7)。

外部模式

快速比较通道的参考值可以从关联的转换器组导出。该组模拟输入的结果可以自动复制到寄存器FCxFCM (x=0-7)中的位场FCREF。在此模式下,被控信号将跟随相关转换器组的选定输入通道(参见图257中的“更新”)。

参考转换器组使用第107页的“硬件数据接口”来复制其结果值。

在特定于产品的附录中描述了组和快速比较通道的关联。

32.8.2 快速比较通道控制寄存器

下面的一组寄存器提供了对快速比较通道操作的初始化和控制。

注意:仅在各自的通道停止时更改配置。

Fast Compare Control Register, FC Channel x

快速比较通道的控制寄存器选择外部门和/或触发信号。写控制位允许通过简单的写访问对每个功能进行单独控制。

Fast Compare Mode Register, FC Channel x

快速比较模式寄存器配置快速比较通道的操作模式。

注:当位域AUE = 00B时,软件只能写入位域FCREF。

Fast Compare Ramp Register 0, FC Channel x

快速比较斜坡寄存器为比较值定义一个斜坡(起始水平,结束水平)。这可以用来实现软启动/停止功能或自适应阈值。

Fast Compare Ramp Register 1, FC Channel x

32.8.3 边界定义

实际边界以参考值FCxFCM (x=0-7)定义。FCREF和定义迟滞带的正负δ值。

寄存器FCxFCHYST (x=0-7)中的位域DELTAMINUS和DELTAPLUS存储增量值。

实际使用的比较值取决于当前结果值FCR(见FCxFCBFL (x=0-7)):“FCR =0:参考值+上增量(FCREF + DELTAPLUS)”FCR = 1:参考值-下增量(FCREF - DELTAMINUS)注:结果比较值是饱和的,以适应固定的结果范围(000H…3FFH)。

Fast Comp. Hysteresis Register, FC Channel x

快速比较操作的上限和下限在快速比较迟滞寄存器中定义。

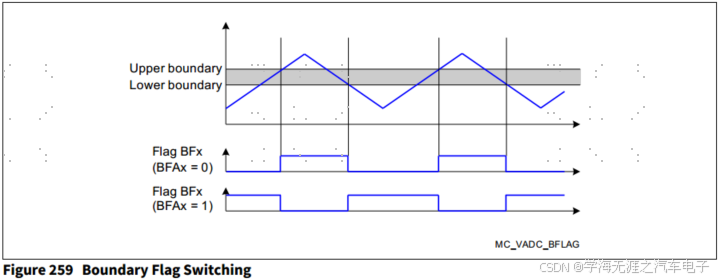

32.8.4 边界标志控制

可以将限制检查机制配置为自动控制边界标志。这些边界标志也可用作其他模块的控制信号。当超过定义的电平时,可以设置或清除标志,并且可以选择输出信号的极性。当门处于活动状态时,可以选择一个门信号来启用边界标志操作。

边界标志反映与上边界或下边界比较的结果。基本比较值在位域FCxFCM中提供。FCREF,寄存器FCxFCHYST中的增量值在比较值周围定义了一个迟滞带。

边界标志可以通过以下几个事件进行修改:

“当生成比较结果时,如果 FCxFCBFL.BFM = 1,则按照位 FCxFCBFL.BFA 配置的方式清除或设置边界标志。

“当软件写入位域 FCxFCBFL.BFS 时,边界标志被清除、设置或翻转。

“当通道被禁用(ANON = 0)时,结果标志 FCR 被清除,如果 FCxFCBFL.BFM = 1,则边界标志按照位 FCxFCBFL.BFA 配置的方式被清除或设置。

每个边界标志在组特定的输出行中可用。节点指针还将它们路由到四个公共边界信号之一或相关的公共服务请求线之一,参见位域BFLNP。

注意:清除寄存器GxFCHYST(即增量),如果迟滞是不需要的。

边界标志可以反映比较操作的结果,或者可以强制到一个可配置的水平(位BFV),而相应的请求源门信号是不活动的(低)。参见寄存器FCxFCCTRL (x=0-7)中的位域GTMODE。

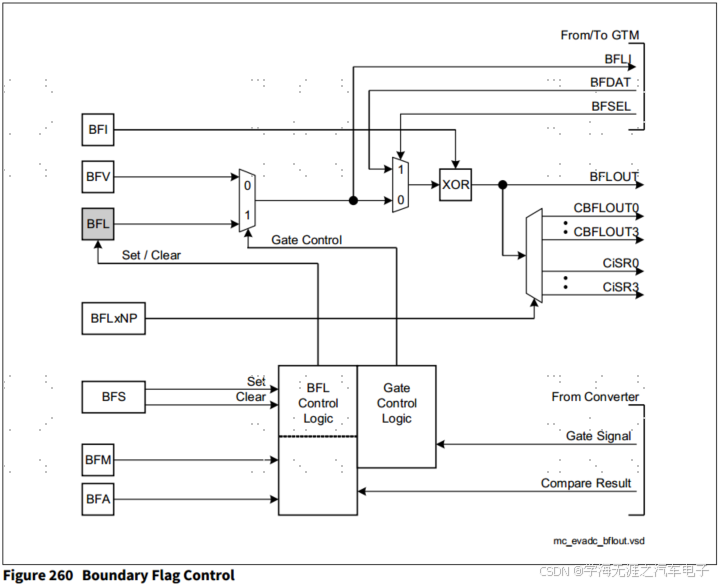

由边界标志导出的输出信号可以由GTM控制。在将边界标志信号发送到输出引脚之前,可以使用选择输入和数据输入临时替换边界标志信号(参见图260)。

软件交互

虽然在应用中,快速比较通道很可能会通过边界标志输出直接控制外部硬件,但也可以进行软件交互,例如在低速下用于调试目的。位 FCxFCBFL.FCR 中有新的比较结果可用时,会通过设置有效标志 FCxFCBFL.VF 来指示。读取寄存器 FCxFCBFL 会自动清除有效标志。由于内部同步,这需要几个时钟周期。

仅建议在低速操作时轮询有效标志,因为:

- 由于位 VF 的清除延迟,设置的有效标志可能会被多次读取。

- 高速率的比较操作可能会在软件检测到 VF = 0 之前设置一个已清除的有效标志。

位 FCxFCBFL.FCR 中有新的比较结果可用也可以通过生成服务请求来指示。选择 FCxFCM.SRG = 11B 且 FCxFCCTRL.CHEVMODE ≠ 00(取决于预期的操作)以启用服务请求路径。这在低速操作中可能很有用,因为短的触发间隔会为系统生成高的服务请求率。

图中展示了边界标志输出的控制逻辑,包括设置 / 清除 BFLOUT、BFL、异或门、BFM、BFI、BFL 的控制逻辑,以及来自 / 去往 GTM 的门信号、BFLI、BFDAT、BFSEL、BFA、比较结果、来自转换器的 BFS、设置、清除、CBFLOUT0、CiSR0、CBFLOUT3、CiSR3、BFLxNP、BFV 和门控制逻辑等部分。

Boundary Flag Register, FC Channel x

边界标志寄存器将边界标志本身与选择激活条件、输出信号极性和基本操作模式的位一起保存。

节点指针引导信号FCxBFLOUT与其他模块(除了特定于组的输出)的片上连接。可能的目标是相应的公共服务请求行或公共边界标志输出(CBFLOUT0…CBFLOUT3)。

此外,软件可以设置或清除边界标志。

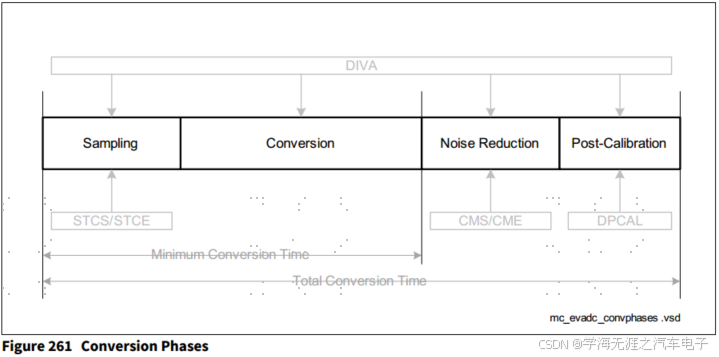

32.9 转换时间

术语“转换时序”不仅包括转换到数字结果本身所需的时间,还包括对各自输入信号进行采样所需的时间、校准所需的时间和额外的内部步骤。

转换的所有阶段都可以由应用程序配置。因此,转换时间也取决于各自的配置。下面的部分列出了可配置的因素,并给出了一些转换时间的示例。

注意:从请求相应转换的触发事件到示例阶段开始的时间取决于仲裁,因此只能使用已知的系统设置来确定。

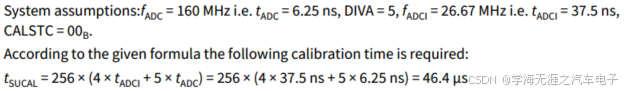

32.9.1 启动校准定时

在操作EVADC通道之前,需要进行启动校准。校正时间可由下式计算:

![]()

时序示例启动校准

注:启动校准不是实际转换的一部分。同时,相应的校准时间对转换时间也没有影响。然而,这是准确转换结果的先决条件。

32.9.2 标准转换器通道定时

总转换时间包括从采样阶段开始到结果可用的时间。

触发转换的频率也取决于几个可配置的因素:

- 选取的样本时间,根据输入类定义。对于使用外部多路复用器的转换,还包括扩展的采样时间计数。

- “由于取消转换而导致的延迟必须重复。

- "由于其他信道的等距采样而导致的延迟。

- 外部触发信号的频率,如果启用。

- "请求计时器的周期,如果启用,

转换时间取决于以下用户可定义的因素:

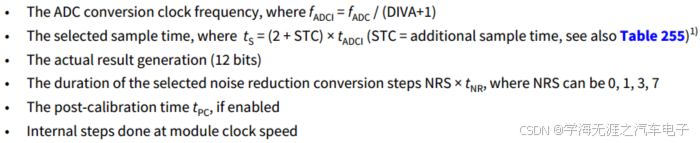

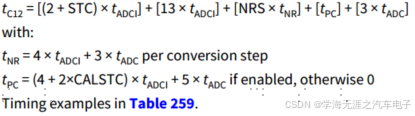

转换时间是采样时间、转换步长和内部步长之和。其计算公式如下:

32.9.3 快速比较通道定时

快速比较通道执行单个比较操作,而不是完整的SAR算法。在任何情况下都需要采样时间。

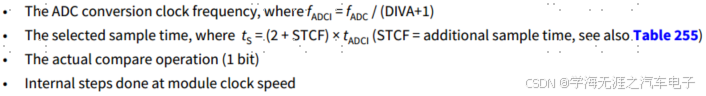

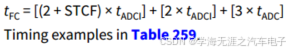

转换时间取决于以下用户可定义的因素:

比较时间是采样时间、比较步长和内部步长之和。其计算公式如下:

注:为了确保等距结果,请确保编程请求周期大于最大比较时间。

32.9.4 转换定时配置

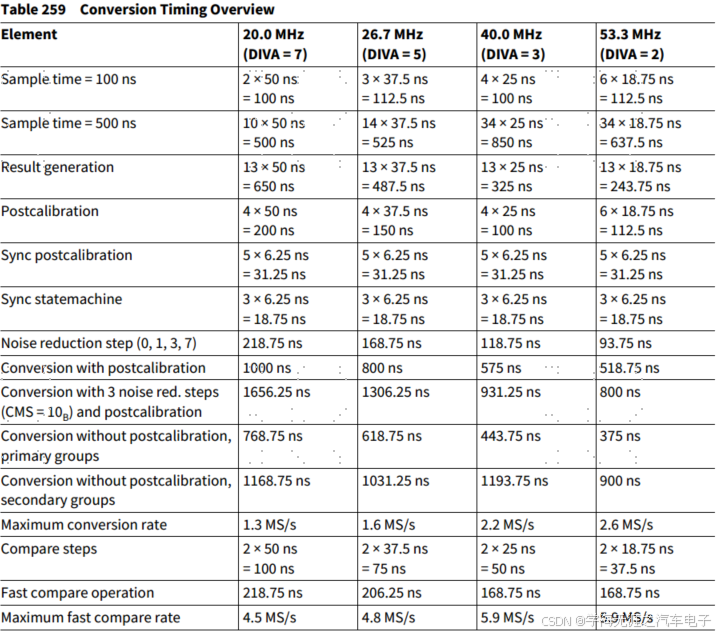

下表中的示例假设主要组所需的最小采样时间为100 ns。

二次组或外部信号源的特性需要更长的采样时间,导致总转换时间增加。

最大转换率可以实现后校准禁用。这可以是临时的,也可以是永久的,这取决于应用程序的需求。

系统假设:fADC = 160 MHz,即tdac = 6.25 ns,单个MSB, fADCI≤40 MHz时CALSTC = 0, fADCI = 53.3 MHz时CALSTC = 1。

32.10 转换结果处理

A/D转换器可以对转换结果数据进行一定程度的预处理,然后存储以供CPU或DMA通道检索。这支持应用程序软件对结果数据的后续处理。

转换结果处理包括以下功能:

32.10.1 转换结果的存储

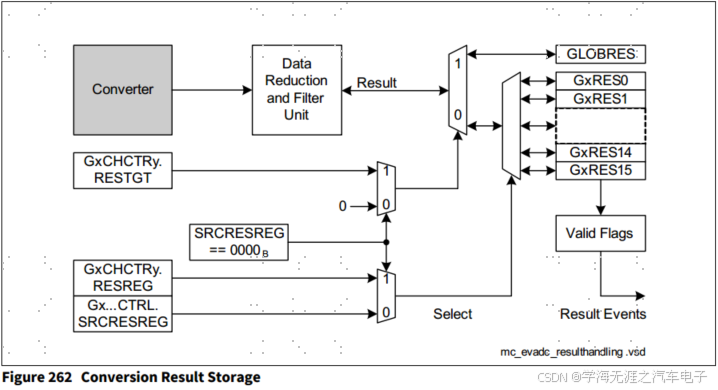

某个组的转换结果值可以存储在16个关联的组结果寄存器之一中,也可以存储在通用的全局结果寄存器中(参见选择结果寄存器)。

这种结构为不同频道集的转换结果提供了不同的位置。根据应用程序的需要(数据减少、自动扫描、别名功能等),用户可以分配转换结果,以最小化CPU负载和/或优化DMA传输的性能。

快速比较通道的比较结果值存储在寄存器FCxFCBFL (x=0-7)的位FCR中。

每个结果寄存器都有一个单独的数据有效标志(VF)。此标志表示“新的”有效数据何时已存储在相应的结果寄存器或位中并可以读出。

注意:有效标志表示由转换器生成的结果。标准的结果寄存器也可以用软件编写。在这种情况下,写入结果寄存器后,有效标志是未定义的。

对于标准转换,结果值在位域result中可用。

结果寄存器可以通过两个不同的视图(views)读取。这些视图使用不同的地址,但访问相同的寄存器数据:

- 当通过应用程序视图读取结果寄存器时,在读取结果时自动清除相应的有效标志。这在结果生成和检索之间提供了一个简单的握手。这也支持wait-for-read模式。

- 当通过调试视图读取结果寄存器时,相应的有效标志在读取结果时保持不变。这支持通过交付结果值而不干扰与应用程序的握手来进行调试。

应用程序可以通过几个结果寄存器检索转换结果:

- “组结果寄存器:返回结果值和通道号”

- 全局结果寄存器:返回结果值、通道号和组号。

选择结果寄存器:

转换结果存储在结果寄存器中,用户可以根据应用程序的要求分配结果寄存器。以下位域将结果指向寄存器:

- “寄存器 GxQCTRLi(i = 0 - 2;x = 0 - 11)中的 SRCRESREG 等。当使用特定于源的结果寄存器时,选择特定组的结果寄存器 GxRES1……GxRES15。

- “寄存器 GxCHCTRy 中的 RESTGT。选择全局结果寄存器而不是特定组的结果寄存器。

- “寄存器 GxCHCTRy 中的 RESREG。当使用特定于通道的结果寄存器时(见下文),选择特定组的结果寄存器 GxRES0……GxRES15。

使用特定于源的结果寄存器允许从不同请求源请求的同一通道中分离结果。通常,这些请求源由不同的任务使用,并在不同的时间触发。

使用全局结果寄存器可以方便地处理来自不同组的结果,例如在菊花链的情况下。这样,单个DMA通道就可以卸载所有结果。

当使用GLOBRES作为目标时,请确保一次只向其写入一个结果,这样就不会丢失结果值。

注意:对于由另一个主机触发的同步转换,将忽略位域SRCRESREG。在这种情况下,不涉及请求源,选择来自通道控制寄存器。

Group x Result Control Register y

组结果控制寄存器选择给定组的结果寄存器的行为。

GxRCRy (x=0-11;y=0-15)

Group x Result Control Register y

组结果寄存器为给定组的所有通道提供可选择的存储位置。

注:结果寄存器GxRES15的内容在硬件数据接口上可用。

GxRESy (x=0-11;y=0-15)

Group x Result Register y (0700H+x*400H+y*4) Application Reset Value: 0000 0000H

但是,组结果寄存器的调试视图提供对给定组的所有结果寄存器的访问,而不清除有效标志。

GxRESDy (x=0-11;y=0-15)

Group x Result Reg. y, Debug

Global Result Control Register

全局结果控制寄存器选择全局结果寄存器的行为。

GLOBRCR

Global Result Control Register

Global Result Register:全局结果寄存器为所有组的所有通道提供公共存储位置。

Global Result Register, Debug:但是,全局结果寄存器的调试视图提供对全局结果寄存器的访问,而不清除有效标志。

Valid Flag Register, Group x:有效标志寄存器汇总所有结果寄存器的有效标志。通过向相应的位位置写入1来清除有效的标志。

32.10.2 数据对齐

所选结果寄存器中转换结果值的有效位数取决于配置(参见图263):

- "选择的结果位置(Left/ right-aligned d1),用于标准转换结果"

- "选择的数据修改模式(累积、差异、过滤器:始终右对齐,RESPOS = 0!)

这些选项以最小化应用程序软件的数据处理的方式提供转换结果。

32.10.3 Wait-for-Read模式

读等待模式可防止由于在 CPU(或 DMA)读取先前数据之前用新的转换结果覆盖结果寄存器而导致的数据丢失。例如,自动扫描转换序列或其他具有 “宽松” 时序要求的序列可能使用一个公共结果寄存器。然而,结果来自不同的输入通道,所以覆盖会破坏前一次转换的结果。

读等待模式会自动暂停该通道从该源开始的转换,直到当前结果被读取。因此,硬件或软件触发可以请求一次转换或一个转换序列,而每次转换只有在前一次转换的结果被读取后才会开始。这会自动使转换序列与 CPU/DMA 读取先前转换结果的能力(延迟)保持一致。

如果为结果寄存器启用读等待模式(位 GxRCRy.WFR = 1),当目标结果寄存器包含有效数据(由有效标志 VF = 1 指示)或当前正在进行的转换目标为同一结果寄存器时,请求源不会生成转换请求。

如果两个请求源以选择了读等待模式的方式针对同一结果寄存器,那么较高优先级的源不能中断在较高优先级源请求其转换之前启动的较低优先级转换请求。在这种情况下,取消 - 注入 - 重复模式不起作用。如果较高优先级请求针对不同的结果寄存器,较低优先级的转换可以被取消并在之后重复。

1) RESPOS = 1将读取结果值左移4位。因此,这只对标准的12位转换结果有意义。全局结果寄存器GLOBRES总是以右对齐的方式存储结果。

2) 使用单独结果寄存器的单个通道的重复转换不会破坏其他结果,而是更新自己先前的结果值。这样,实际的信号数据在结果寄存器中总是可用的。

如果来自不同组的请求源以选择了读等待模式(位 GLOBRCR.WFR = 1)针对全局结果寄存器,那么只有当 GLOBRES.VF 已经被设置时,转换请求才会被抑制。并发请求可能会导致冲突,因为在序列开始时,几个请求源可能会看到全局有效标志被清除。

为了避免这种情况,确保这些转换仅按顺序请求,就像菊花链的情况一样。

注意:Wait-for-read模式在同步slave的同步转换中被忽略(参见章节32.11)。

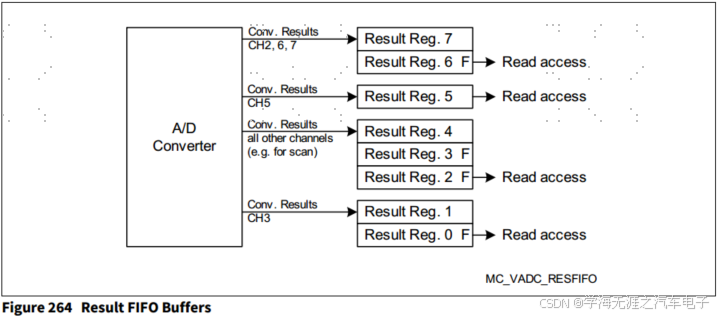

32.10.4 结果FIFO缓冲区

结果寄存器既可以用作转换结果的直接目标,也可以与其同一 ADC 组的上一个相邻结果寄存器连接起来,形成一个结果 FIFO 缓冲区(先进先出缓冲机制)。结果 FIFO 存储了几个测量结果,可以在稍后以 “宽松” 的 CPU 响应时间读出。可以使用可用的结果寄存器设置多个 FIFO 缓冲区结构。

由两个或多个寄存器组成的结果 FIFO 结构是通过将结果寄存器连接到它们的上一个相邻结果寄存器(具有更高的索引,见图 264)来构建的。这可以通过设置位域 GxRCRy.FEN = 01B 来启用。

转换结果存储在 FIFO 结构中索引最高的寄存器中(GxRCRy.FEN = 00B)。

软件从具有最低索引的 FIFO 寄存器中读取值。

在示例中,结果寄存器已按以下方式配置:

注意:如果GxRES15是FIFO缓冲区的输入阶段,那么写入到它的结果值只有在该值完全填充FIFO时才会反映在HDI上。中间结果不写入HDI。如果要使用HDI,请选择较低的结果寄存器作为输入级。

最小/最大检测

一种特殊的 FIFO 模式,如果结果高于(或低于)该级的当前值,则仅更新相应的 FIFO 级,存储转换序列的最高(或最低)结果。这可以通过设置位域 GxRCRy.FEN = 10B(最大值)或 GxRCRy.FEN = 11B(最小值)来启用。

注意:在要监视的转换序列开始之前,在峰值结果寄存器的结果位域中写入一个合理的起始值。

使用0000H查找最大值,使用0FFFH查找最小值(只比较较低的12位!)

实际的结果值可以从各自通道所针对的结果寄存器中获得。

结果FIFO缓冲定时

为了更新结果FIFO缓冲区的输出,有6个系统外围总线周期(fSPB)和6个ADC时钟周期(fADC)的延迟。这个延迟必须考虑CPU或DMA的读出:

结果 FIFO 缓冲区到 CPU 的数据传输通常通过连续的单个读取命令过程来完成。从 CPU 到系统外设总线的架构定义的访问时间为 5 个系统外设总线周期(fSPB)。因此,在连续读取之间必须考虑 1 个 fSPB 周期和 6 个 fADC 周期的等待时间。

“为确保数据完整性,必须使用考虑上述 FIFO 时序的 DMA 配置。从 DMA 的角度来看,基于单次传输和多次数据移动的配置将是首选。然而,这种配置不能满足 FIFO 时序。对于初始数据移动,执行时间由 6 个系统外设总线时钟周期(fSPB)和 13 个系统资源接口时钟周期(fSRI)定义。所有后续的数据移动需要 3 个 fSPB 时钟周期和 11 个(fSRI)时钟周期。为了将结果 FIFO 缓冲区与 DMA 一起使用,可以使用链表 DMA 配置。使用这种配置,可以确保 DMA 延迟(6×fSPB + 13×fSRI)比结果 FIFO 缓冲区的更新时间(6×fSPB + 6×fADC)更长。

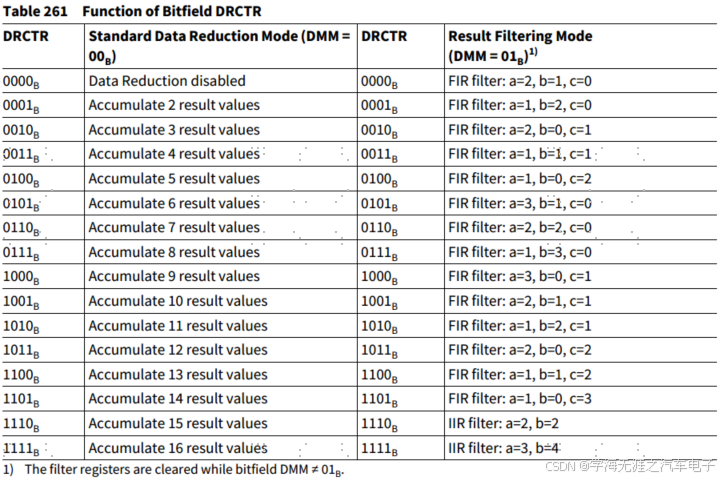

32.10.5 数据修改

转换产生的数据可以在应用程序使用之前自动修改。可以选择几个选项(寄存器GxRCRy中的位域DMM (x=0-11;y=0-15)等),这减少了卸载和/或处理转换数据所需的CPU/DMA负载。

标准数据缩减模式(适用于 GxRES0……GxRES15):在每个结果寄存器中累积 2 到 16 个结果值,然后生成结果中断。这可以去除输入信号中的噪声或为应用程序预处理结果数据。

“结果滤波模式(FIR,适用于 GxRES7、GxRES15):对所选结果寄存器的转换结果应用具有可选系数的三阶有限脉冲响应滤波器(FIR)。

“结果滤波模式(IIR,适用于 GxRES7、GxRES15):对所选结果寄存器的转换结果应用具有可选系数的一阶无限脉冲响应滤波器(IIR)。

“差值模式(适用于 GxRES1……GxRES15):从所选结果寄存器的转换结果中减去结果寄存器 GxRES0 的内容。在此模式下,位域 DRCTR 不被使用。

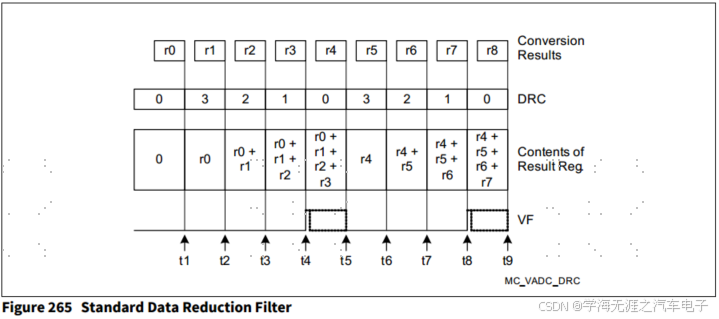

标准数据简化模式

数据缩减模式可作为数字滤波器用于抗混叠或抽取目的。它最多累积16个转换值以生成最终结果。

每个结果寄存器可以单独启用数据缩减,由寄存器GxRCRy和GLOBRCR中的位场DRCTR控制。数据约简计数器DRC表示积累的实际状态。

注意:其他结果寄存器的转换可以插入到要累积的转换之间。

这个例子展示了一个包含4个累计转换结果的数据约简序列。8个转换结果(r0…r7)被累积并产生2个最终结果。

当转换完成并将数据存储到启用了数据缩减模式的结果寄存器时,数据处理由数据缩减计数器DRC控制:

- 如果DRC = 0(示例中的t1, t5, t9),则转换结果存储到寄存器中。DRC加载了位域DRCTR的内容(即开始积累)。

- 如果DRC > 0(例中为t2, t3, t4和t6, t7, t8),则转换结果加到结果寄存器的值中。DRC减1。

- 如果DRC变为0,从1开始递减(在示例中为t4和t8)或从DRCTR加载,则设置各自结果寄存器的有效位并发生结果寄存器事件。必须在下一个数据约简序列开始之前读取最终结果(在本例中是在t5或t9之前)。这将自动清除有效标志。

注:软件可以通过清除相应的有效标志(通过GxVFR (x=0-11))来清除数据缩减计数器DRC。

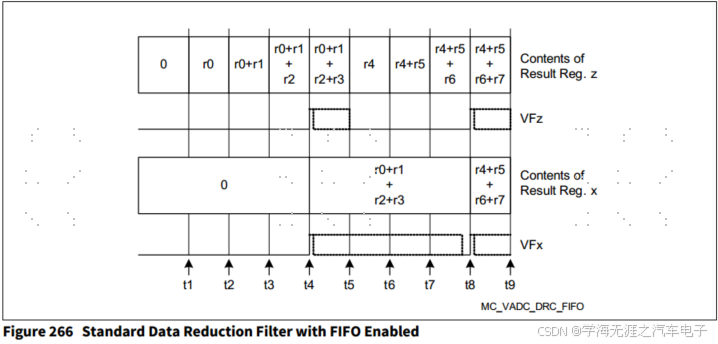

通过关联相邻的结果寄存器来构建结果FIFO,可以增加读取最终数据缩减结果的响应时间(参见图266)。在这种情况下,数据约简序列的最终结果被加载到相邻的寄存器中。这个值可以从这个寄存器中读取,直到下一个数据缩减序列完成(在第二个示例中是t8)。

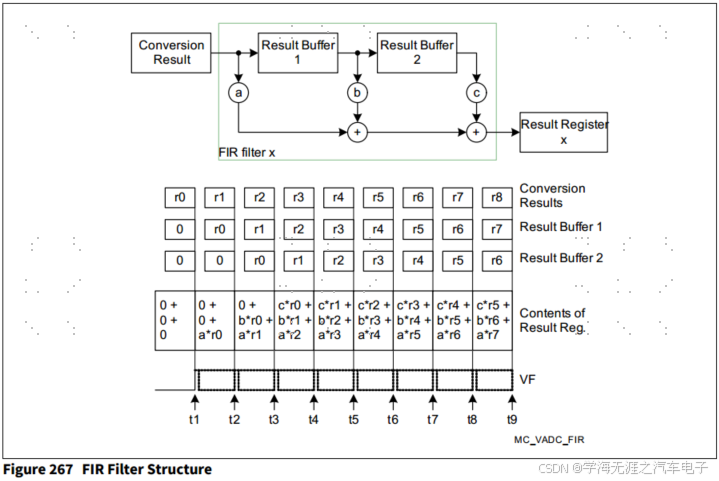

有限脉冲响应滤波模式(FIR)

FIR滤波器(见图267)为中间结果(RB1、RB2)提供2个结果缓冲区和3个可配置抽头系数(a、b、c)。

将转换结果和中间结果缓冲值加以各自的系数加权,形成结果寄存器的最终值。可以通过寄存器GxRCR7和GxRCR15中的位域DRCTR(编码如表261所示)选择几个预定义的系数集。这些系数导致ADC结果的增益为3或4,产生14位值。激活后每个样本的有效标志(VF)被激活,即每个样本产生一个有效的结果。

注意:可以在要过滤的转换之间插入其他结果寄存器的转换。

注:当位域DMM≠01B时,滤波器寄存器被清除。

无限脉冲响应滤波模式(IIR)

IIR滤波器(见图268)提供了一个结果缓冲区(RB)和2个可配置系数(a, b)。它表示一个一阶低通滤波器。

转换结果(用各自的系数加权)和前一个结果的一小部分相加,形成结果寄存器的最终值。可以通过寄存器GxRCR7和GxRCR15中的位域DRCTR(编码如表261所示)选择几个预定义的系数集。这些系数导致ADC结果的增益为4,产生14位值。激活后每个样本的有效标志(VF)被激活,即每个样本产生一个有效的结果。

注意:可以在要过滤的转换之间插入其他结果寄存器的转换。

注:当位域DMM≠01B时,滤波器寄存器被清除。

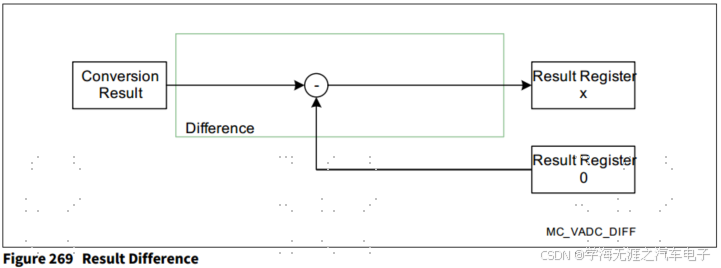

差异模式

从实际结果中减去结果寄存器0的内容,将各自通道的结果与另一个信号相关联。不需要任何软件操作。

引用通道必须将其结果存储到结果寄存器0中。可以一次确定参考值,然后将其用于一系列转换,也可以在每次相关转换之前进行转换。

32.10.6 结果事件产生

当将新值存储到结果寄存器时,可以生成结果事件。结果事件可能会因为数据积累而受到限制,只有当数据积累完成后才会生成结果事件。

结果事件也可以完全被抑制。

32.10.7 硬件数据接口

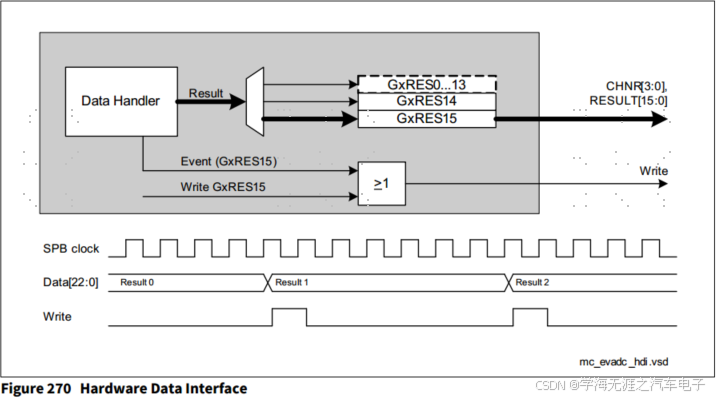

数字转换结果可通过硬件数据接口(HDI)直接提供给其他模块。结果寄存器GxRES15将其内容输出到该接口。每次更新GxRES15时,HDI都会更新数据向量并生成一个写频闪,指示新结果值的可用性。

来自该接口的数据可用于以下几个目的:

- “更新相关快速比较通道的参考值(见附录)。

- “通过雷达接口(RIF)将结果写入信号处理单元(SPU)。

- “将结果写入通用定时器模块(GTM),以便为配备模拟数据接口(ADI)的微控制器子系统(MCSs)提供这些结果。

注意:如果GxRES15是FIFO缓冲区的输入阶段,那么写入到它的结果值只有在该值完全填充FIFO时才会反映在HDI上。中间结果不写入HDI。如果要使用HDI,请选择较低的结果寄存器作为输入级。

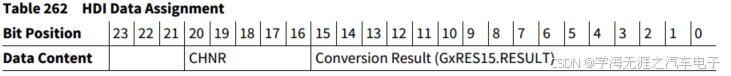

硬件接口提供对各组结果寄存器15的结果数据的访问。通过人类发展指数可获得以下数据要素:

注意:有效 CHNR 位的数量取决于相应的多路复用器。未使用的位为 0。

当通过软件更新 GxRES15 时,HDI 的 20:16 位反映存储在位域 GxRES15.CHNR 中的最后一个值,因为位域 GxRES15.CHNR 不可写。

32.11 同步转换

ADC内核的转换可以根据内核的配置进行自定时调度,也可以由外部(ADC外部)信号触发:

同步转换支持同步组内通道的并行转换。这优化了例如电力驱动的控制。

等距采样支持在最小抖动的固定光栅中进行转换。这可以优化过滤器算法或音频应用程序。

32.11.1 并行采样的同步转换

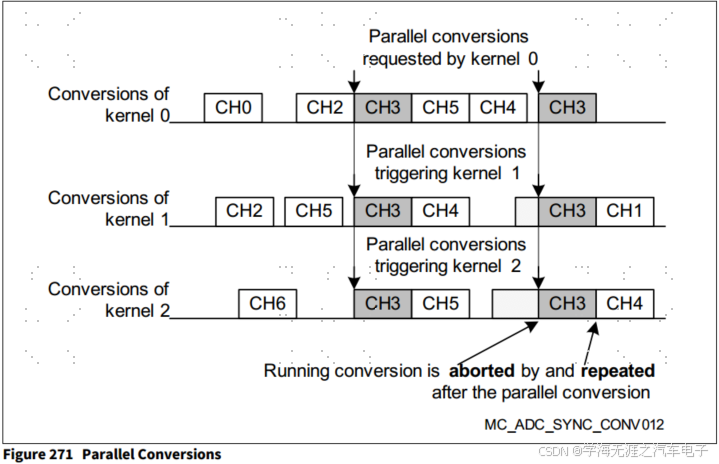

几个独立的ADC内核(1)可以同步用于模拟输入通道的同时测量。虽然不需要并行转换,但内核可以独立工作。

并行转换的同步机制确保相关通道的采样相位同时启动。同步内核转换主服务器请求的相同通道。支持并行转换的每个内核的样例相位长度的不同值。

可以为每个输入通道(一个或多个)单独请求并行转换。在图271所示的示例中,ADC内核0、1、2的输入通道CH3是同步转换的,而其他输入通道不会导致并行转换。

一个内核作为同步主内核运行,另一个内核作为同步从内核运行。每个内核都可以扮演其中一个角色。

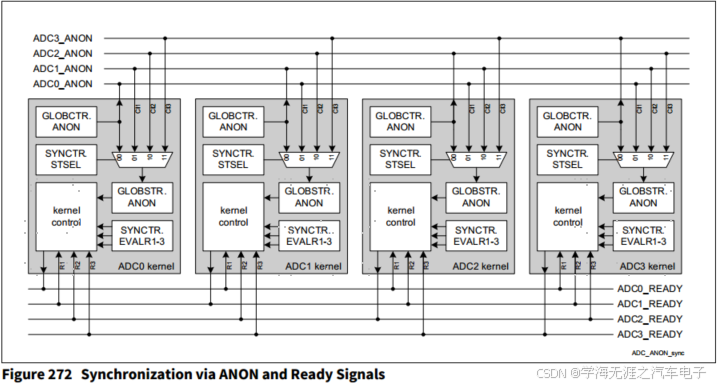

主内核和从内核组成一个“同步组”来控制并行采样:

同步主设备通过提供控制信息 GxARBCFG(x = 0 - 11).ANONS(见图 272)和请求的通道编号来控制从设备。

- 位域 GxSYNCTR(x = 0 - 11).STSEL = 00B 选择主设备的 ANON 信息作为同步组中所有内核的 ANON 信息源。

- 就绪信号指示从内核何时准备好开始并行转换的采样阶段。位 GxSYNCTR(x = 0 - 11).EVALRy = 1 启用由就绪信号进行的控制(在示例中,内核 1 和 2 是从设备,所以 EVALR1 = EVALR2 = 1)。

- 主设备请求对特定通道进行同步转换(在相应的通道控制寄存器 GxCHCTRy 中 SYNC = 1),这也在连接的从 ADC 内核中被请求。

- 主设备支持读等待模式。

同步从设备对来自主设备的同步转换请求做出响应。当没有同步转换请求时,从内核可以执行 “本地” 转换。

- 位域 GxSYNCTR(x = 0 - 11).STSEL = 01B/10B/11B 选择主设备的 ANON 信息作为同步组中所有内核的 ANON 信息源(在示例中内核 0 是主设备,所以 STSEL = 01B)。

- 就绪信号指示主内核和其他从内核何时准备好开始并行转换的采样阶段。位 GxSYNCTR(x = 0 - 11).EVALRy = 1 启用由就绪信号进行的控制(在示例中内核 0 是主设备,所以 EVALR1 = 1,内核 1 和 2 是从设备,所以 EVALR2 = 1)。

- 并行转换请求始终以最高优先级处理,并采用取消 - 注入 - 重复模式。

- 从设备中忽略读等待模式。先前的结果可能会被覆盖,特别是如果其他转换也使用相同的结果寄存器。

一旦启动,就不能中止并行转换。这可确保各个同步组的结果一致。要在应用程序中实现确定性行为,请确保主服务器获得同步转换的最高优先级,这样它就不会被中断。这样,同步转换和标准转换将以相同的方式进行仲裁。

注意:同步转换请求相同的通道号,由主机定义。使用别名特性(参见32.7.2节),可以转换来自不同输入通道的模拟信号。这是有利的,例如,如果使用CH0作为替代参考。

STSEL = 00B选择自己的ANON信息。其他控制输入(STSEL = 01B /10B /11B)按升序连接到同步组的其他内核(参见产品特定附录中的“同步组”)。

Synchronization Control Register, Group x

同步控制寄存器控制并行转换的内核同步。

注意:程序只注册GxSYNCTR,而位域GxARBCFG。同步组所有ADC内核中的ANONS = 00B。然后将主位字段ANONC设置为11B。

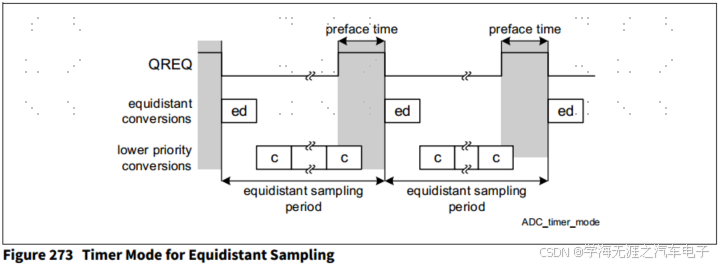

32.11.2 等距采样

为了优化输入数据,例如在滤波器应用中,可以在固定的时间栅格中执行转换。等距采样的转换由定时器信号触发。

对于等距转换的预期源,选择定时器模式(在寄存器 GxQCTRLi(i = 0 - 2;x = 0 - 11)等中,TMEN = 1)。在定时器模式下,该源的请求被触发(由上升沿触发信号触发)并进行仲裁,但只有在触发信号被移除(见图 273)且转换器处于空闲状态时才开始。触发信号 REQTRx 的频率定义了采样率。其高电平时间定义了前言时间间隔,在此期间相应的请求源参与仲裁,而不会启动其他转换。

前言时间(见图 273)必须长于两个时钟周期加上最高可能的转换时间。触发信号的周期必须足够长,以便在下次上升沿触发之前,等距转换和可选的低优先级转换能够完成。

定时器模式的触发信号可以由源请求定时器在模块时钟上本地生成。它可以生成高达约 100µs 的周期。前言时间可以通过位域 SEQTIMOFF 进行选择。

定时器模式的触发信号也可以由外部定时器生成。这允许有更宽范围的周期,但会以同步抖动为代价,因为定时器具有独立的时基。

为了确保转换器处于空闲状态且转换的开始可以由触发信号控制,等距转换请求必须具有最高优先级。请求触发和转换开始之间的前言时间必须足够长,以便当前正在进行的转换能够完成。

等距采样也支持一系列通道。如果前言时间和等距转换不重叠,也可以为多个请求源并行进行等距采样。

注意:在定时器模式下,触发边缘检测器对每个上升沿作出反应。要实现确定性行为(即只有一个触发器),仅在计时器模式激活时使用XTMODE = 10B(即上升沿)。

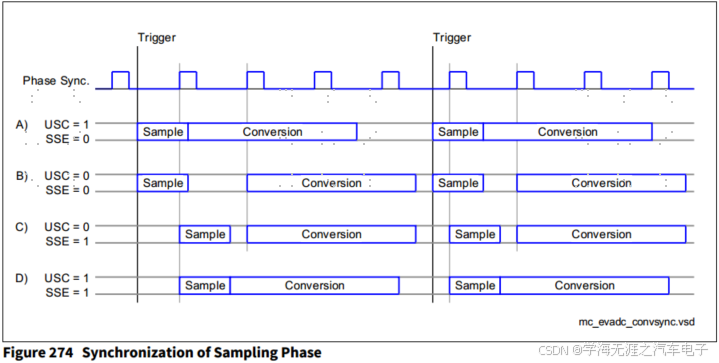

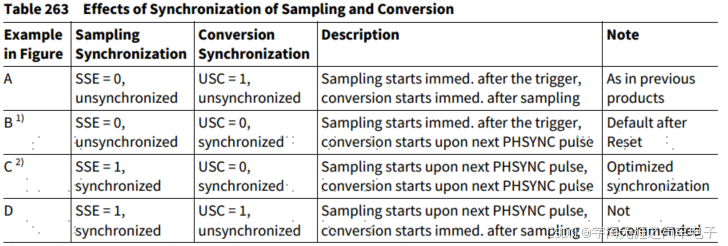

32.11.3 同步采样

采样相位也可以与相位同步器对齐。在这种情况下(通过在寄存器GxANCFG (x=0-11)中设置位SSE启用),采样相位仅在来自相位同步器的触发信号上启动。

下图总结了采样相位同步与转换同步相结合的效果。

1)提供最小的采样抖动相对于触发信号。

2) EDSADC通道激活时,进一步降低了耦合效应。

注:位SSE控制模拟输入的采样。如果对模拟参考电压进行采样(直接通过CH30, CH31,或在断线检测启用时在采样阶段隐式采样),则采样由寄存器GLOBCFG中的位USC控制。

32.12 安全特性

略

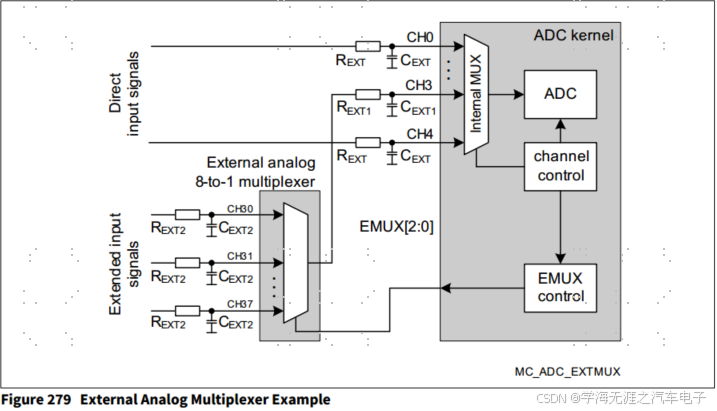

32.13 外部多路复用控制

可以通过将外部模拟多路复用器连接到输入通道来增加模拟输入通道的数量。EVADC可以配置为自动控制这些外部多路复用器。

每个可用的EMUX控制接口都可以由任意组控制(参见寄存器EMUXSEL)。可以选择该组中的一个通道或一组通道用于此操作模式(参见寄存器GxEMUXCS (x=0-11))。EVADC支持1 / 8多路复用器,有几个控制选项:

“稳定模式:在遇到所选通道时转换配置的外部通道。转换序列:

--4 - 32 - 2 - 1 - 0 - -4 - 32 - 2 - 1 - 0 - -4 - 32 - 2 - 1 - 0 - -…(对于如图 279 所示的配置)

--4 - 32 - 2 - 12 - 0 - -4 - 32 - 2 - 12 - 0 - -4 - 32 - 2 - 12 - 0 - -…(对于配置了 EMUX 通道 1 和 3 的情况)。

“单步模式:在遇到所选通道时转换配置序列中的一个外部通道。转换序列:

--4 - 32 - 2 - 1 - 0 - -4 - 31 - 2 - 1 - 0 - -4 - 30 - 2 - 1 - 0 - -4 - 32 -…(对于如图 279 所示的配置)

--4 - 32 - 2 - 11 - 0 - -4 - 30 - 2 - 12 - 0 - -4 - 31 - 2 - 10 - 0 - -4 - 32 -…(对于配置了 EMUX 通道 1 和 3 的情况)(单步模式在只有一个通道时效果最佳)。

“序列模式:在遇到所选通道时自动转换所有配置的外部通道 1)。转换序列:

--4 - 32 - 31 - 30 - 2 - 1 - 0 - -4 - 32 - 31 - 30 - 2 - 1 - 0 - -…(对于如图 279 所示的配置)

--4 - 32 - 31 - 30 - 2 - 12 - 11 - 10 - 0 - -4 - 32 - 31 - 30 - 2 -…(对于配置了 EMUX 通道 1 和 3 的情况)。

“块模式:在遇到所选通道时,为所有 EMUX 通道 2)转换配置序列中的相同外部通道。转换序列:

--4 - 32 - 2 - 12 - 0 - -4 - 31 - 2 - 11 - 0 - -4 - 30 - 2 - 10 - 0 - -4 - 32 -…(对于配置了 EMUX 通道 1 和 3、EMUXCCB = 01H 的情况)。

注意:图279中的示例有一个连接到通道CH3的外部多路复用器。假设起始选择值EMUXSET为2。假设转换顺序为4-3-2-1-0。

上述列表中描述的备选序列假设通道CH1上有类似的EMUX电路。

位域 EMUXACT 确定发送到外部多路复用器的控制信息。

在单步模式下,每次启用通道的转换后都会更新 EMUXACT。如果 EMUXACT = 000B,它将从位域 EMUXSET 重新加载,否则它将递减 1。

由于信号路径的改变,额外的外部通道可能具有不同的特性。在额外的输入处可以使用本地滤波器(图 279 中 CH3x 上的 REXT2 - CEXT2)。对于外部多路复用器远离 ADC 模拟输入的应用,建议在 ADC 的模拟输入处直接添加一个 RC 滤波器(图 279 中 CH3 上的 REXT1 - CEXT1)。每个 RC 滤波器限制模拟输入信号的带宽。在切换外部多路复用器后,CEXT1 必须从相应的 CEXT2 电路充电。

因此,外部通道的转换使用在 ICLASS 寄存器中定义的备用设置(AIPE、CME、SESPE)。如果需要,这会自动选择不同的转换模式。

切换外部多路复用器通常需要输入信号有额外的建立时间。因此,每次外部通道改变时都会应用备用采样时间设置 STCE。在这种情况下,这会自动满足不同的采样时间要求。如果由位 EMXST 启用,STCE 也可以应用于外部通道的每次转换。

1)在序列模式下,主通道编号保存在寄存器 GxQBURi 中(见第 32.5 节)。使 GxQBURi 无效会中止当前的 EMUX 序列,必须避免这种情况。请注意以下限制:

- 当外部多路复用器在序列模式下运行时,不能丢弃已取消的转换。在这种情况下,位 RPTDIS 必须为 0。另见第 32.6.2 节。

- 不要通过软件清除有效标志(GxQMR.CLRV)。

2)当转换位域 EMUXCCB 中定义的通道时,外部通道编号会切换。因此,EMUXCCB 应包含在序列中最后转换的通道。

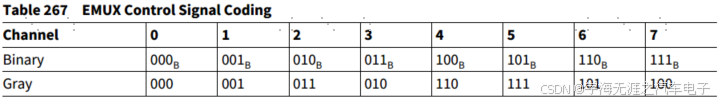

控制信号

控制外部多路复用器的外部通道号可以以标准二进制格式或灰度编码输出。在选择信道序列时,灰色码避免了中间多路复用器切换,因为一次只改变一个比特。表267显示了结果代码。

无需外部多路复用器的操作

如果应用程序中没有使用外部多路复用器,则控制寄存器的重置值提供适当的设置。

EMUXMODE = 00B禁用EMUX自动控制。

由于控制输出信号是备用端口输出信号,如果明确选择,它们仅在各自的引脚上可见。

在每个组中,任意通道(EMXCCS =0)或通道集(EMXCCS = 1)可以通过寄存器GxEMUXCS (x=0-11)分配给外部多路复用器控制。

每个可用的端口接口选择控制线为输出的组(寄存器EMUXSEL)。

External Multiplexer Control Reg., Group x

1)对于单步模式、顺序模式和块模式:先选择EMUXMODE=000B的启动值,再选择各自的模式。

2)单步模式每次转换EMUX通道时修改EMUX通道号。因此,单步模式最好使用单个通道,否则可能会跳过一些外部通道。

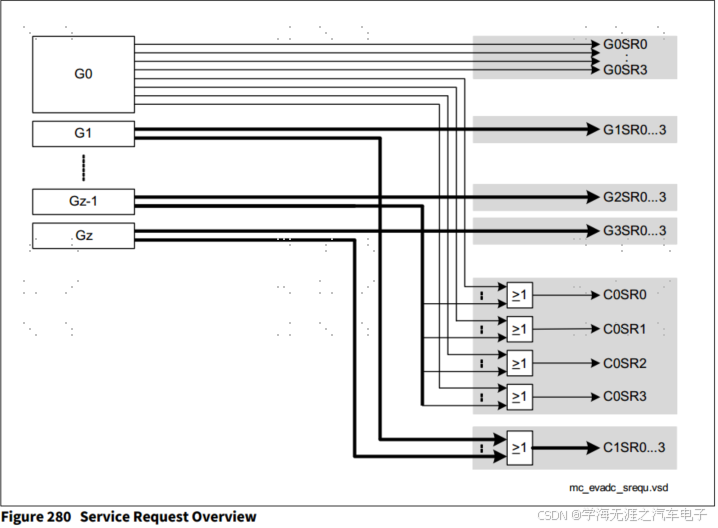

32.14 服务请求生成

每个A/D转换器可以激活多达4个组特定的服务请求输出信号和多达4个共享服务请求输出信号来发出中断或触发DMA通道。有两个常见的服务请求组可用,请参见特定于产品的附录。

可以为每个服务请求输出分配多个事件。服务请求可以通过三种类型的事件生成:

- 请求源事件:表示请求源已完成请求的转换序列,并且应用程序软件可以启动进一步的操作。对于组队列源,事件根据编程生成,即当具有启用的源中断的通道已被转换或遇到无效条目时。

- “通道事件:表示转换已完成。可选地,可以将通道事件限制为在可编程值范围内的结果值。这减轻了 CPU/DMA 的后台任务负担,即仅在满足或超过指定的转换结果范围时才激活服务请求。

- “结果事件:表示结果寄存器中有新的有效结果。通常,这会触发 CPU(或 DMA)的读取操作。可选地,如果数据缩减处于活动状态,则可以仅以降低的速率生成结果事件。例如,如果序列的所有通道都针对同一结果寄存器,并且传输由结果事件触发,那么单个 DMA 通道可以读取完整的自动扫描序列的结果。

每个ADC事件都有一个专用标志,可以通过软件清除。如果为某个事件启用了服务请求,则为每个事件生成服务请求,而与相应事件的状态无关。

事件指示标志。这确保了ADC事件的高效DMA处理(ADC事件可以生成服务请求,而不需要清除指示标志)。事件标志寄存器表示ADC操作期间发生的所有类型的事件。软件可以通过在寄存器GxCEFLAG/GxREFLAG的相应位置上写一个1来设置每个标志,从而触发一个事件。软件可以通过在寄存器GxCEFCLR/GxREFCLR中分别写一个1来清除每个标志。如果启用,则为每次事件的发生生成服务请求,即使相关标志仍然设置。

节点指针

寄存器来自每个事件源的请求可以通过关联的节点指针定向到一组服务请求节点。

来自多个源的请求可以定向到同一节点;在这种情况下,它们被发送到服务请求输出信号。

32.14.1 Source Event Flag Registers, Group x

这些寄存器处理转换请求源(Q0、Q1、Q2)生成的事件。

注:软件可以设置寄存器GxSEFLAG中的所有标志,并通过将1写入相应的位来触发相应的事件。写0没有效果。

通过将1写入寄存器GxSEFCLR中的相应位,软件可以清除寄存器GxSEFLAG中的所有标志。

32.14.2 Channel Event Flag Registers, Group x

这些寄存器处理转换生成的事件,特别是在限制检查期间。

注:软件可以设置寄存器GxCEFLAG中的所有标志,并通过将1写入相应的位触发相应的事件。写0没有效果。

软件可以通过将1写入寄存器GxCEFCLR中的相应位来清除寄存器GxCEFLAG中的所有标志。

Channel Event Flag Register, Group x

这个寄存器的布局取决于多路复用器的配置。

主组有8个通道,因此有8个通道事件标志(CEV7…CEV0)。

辅助组有16个通道/通道事件标志(CEV15…CEV0)。

Channel Event Flag Clear Register, Group x

这个寄存器的布局取决于多路复用器的配置。

主组有8个通道,因此有8个通道事件清除标志(CEV7…CEV0)。

辅助组有16个通道/通道事件清除标志(CEV15…CEV0)。

32.14.3 Result Event Flag Registers, Group x

这些寄存器处理由结果寄存器中可用的新结果值生成的事件。

注:软件可以设置寄存器GxREFLAG中的所有标志,并通过将1写入相应的位来触发相应的事件。写0没有效果。

软件可以通过将1写入寄存器GxREFCLR中的相应位来清除寄存器GxREFLAG中的所有标志。

Result Event Flag Register, Group x

Result Event Flag Clear Register, Group x

Result Event Node Pointer Reg. 0, Group x

Result Event Node Pointer Reg. 1, Group x

32.14.4 Global Event Flag Registers

这些寄存器处理由全局结果寄存器中可用的新结果生成的事件。

注:软件可以设置标志位REVGLB,并通过向REVGLB写入1触发相应的事件。写0没有效果。

软件可以通过写入1到位REVGLBCLR来清除这个标志。

同时设置这两个位清除标志。

Global Event Flag Register

Global Event Node Pointer Register

32.14.5 Software Activation of Service Requests, Group x

此寄存器为服务请求线路提供软件控制。

Service Request Software Activation Trigger, Group x

通过将“1”写入寄存器GxSRACT中的相应位,可以通过软件激活每个服务请求。

这可以用于评估和测试目的。

注意:有关共享服务请求行,请参阅特定于产品的附录中的公共组。

GxSRACT (x=0-11)

32.14.6 Service Requests for Fast Compare Channels

每个快速比较通道都可以通过专用的服务请求线发出服务请求。每个服务请求都可以通过几个可配置的事件来激活。

活动事件由寄存器FCxFCM中的位域SRG (x=0-7)和寄存器FCxFCCTRL中的位域CHEVMODE (x=0-7)选择。

下图总结了触发服务请求的Fast Compare Channel事件的配置。

1764

1764

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?