1.偶分频

1.1 普通偶分频

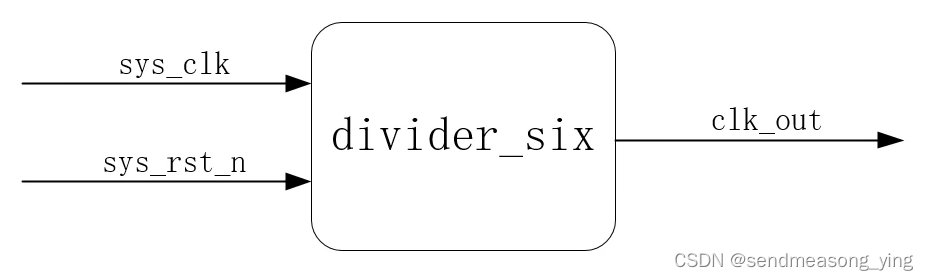

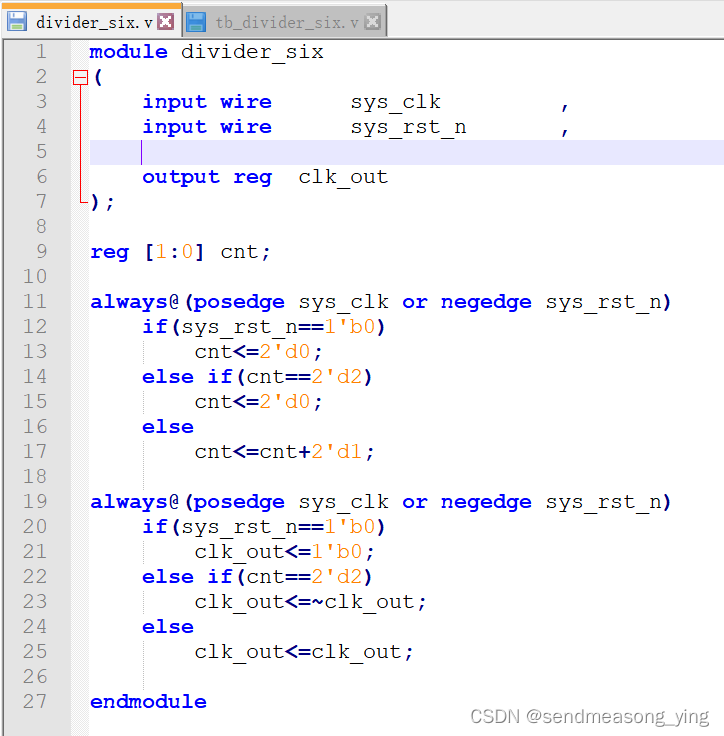

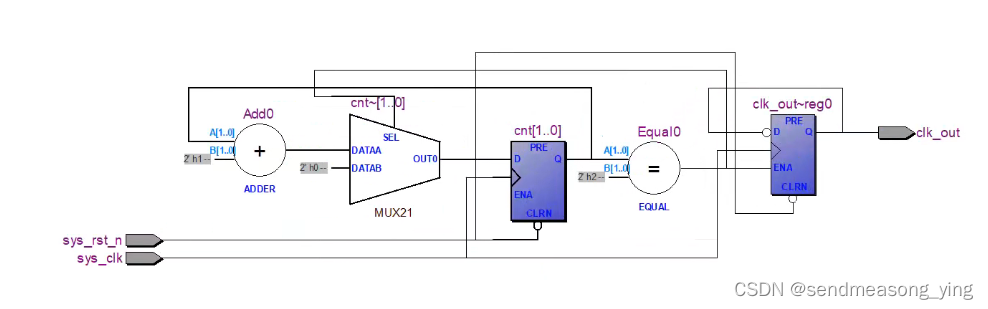

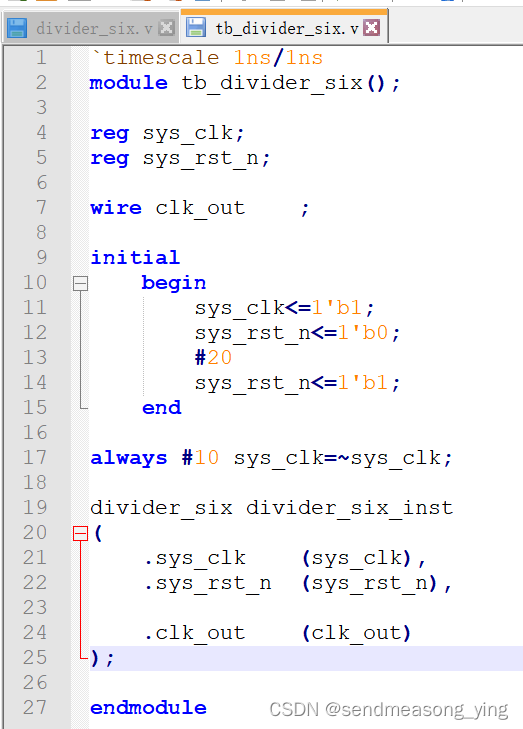

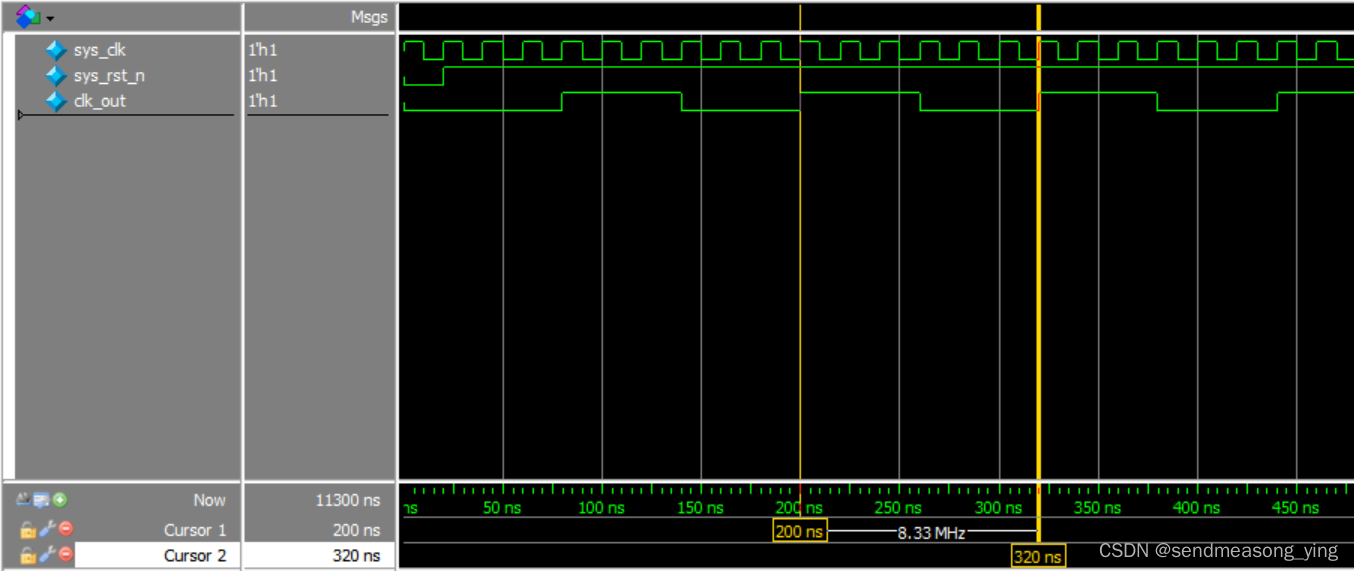

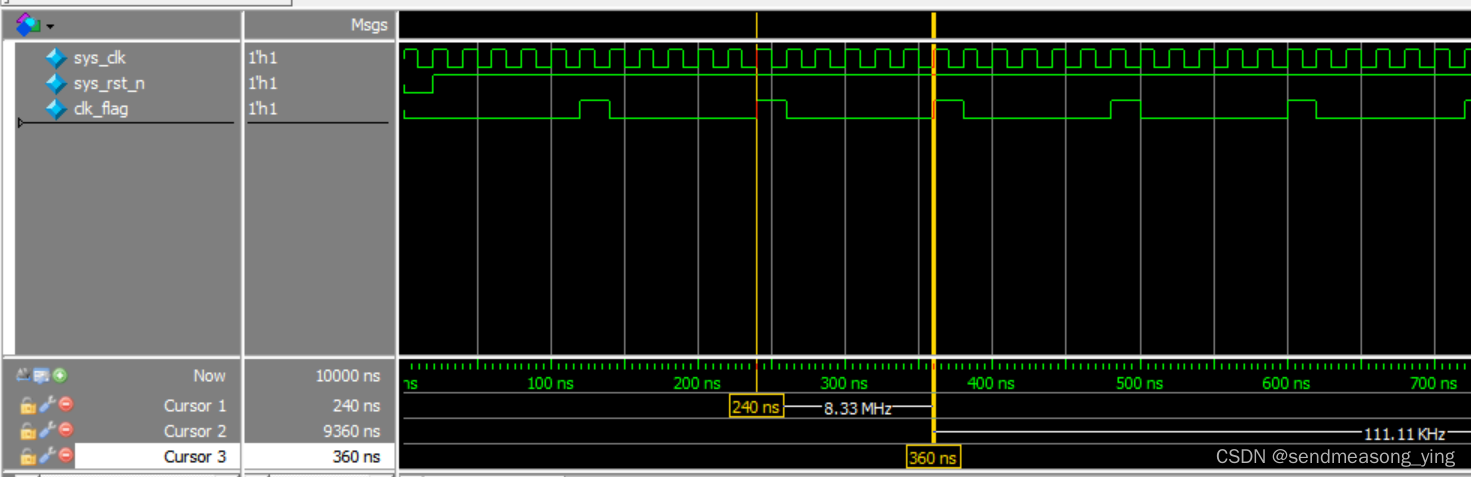

看底下的频率一个周期8.33NHZ是50MHZ的6分频。

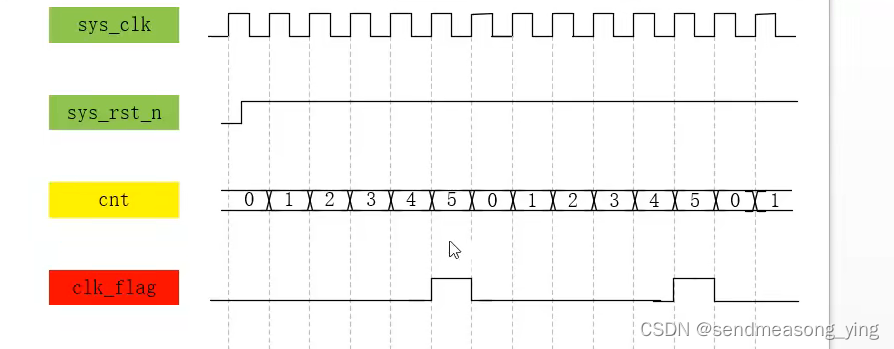

现在修改时序图,因为FPGA的时钟信号都要连接到全局时钟网络,全局时钟网络的作用是尽可能使时钟信号到达每个寄存器的时间尽可能相同,减少时序问题的产生。而以上编写分频的时钟信号并没有连接到全局时钟网络,但是外部晶振通过管脚连接到FPGA的专用时钟引脚上,自然就连接到了全局时钟网络上。所以在系统时钟下工作的信号比产生的分频信号更容易在高速系统中保持稳定。

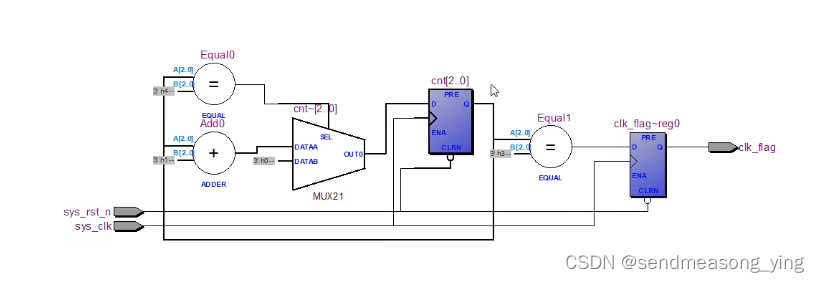

可以用一个脉冲标志信号改善这个问题。

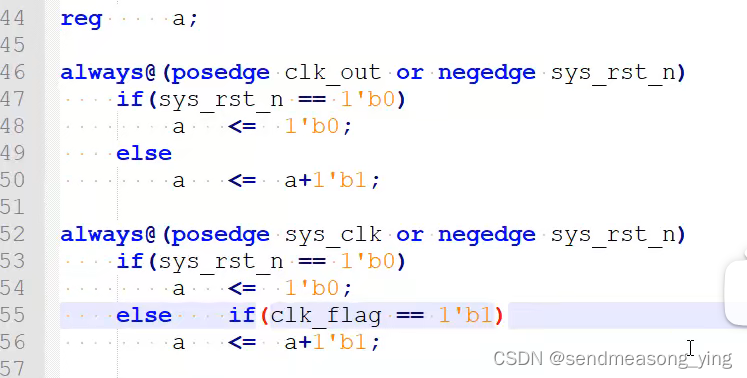

这样理解为什么要用第二种设置脉冲标志信号的方法,因为其他信号使用分频信号时仍然可以使用系统时钟。

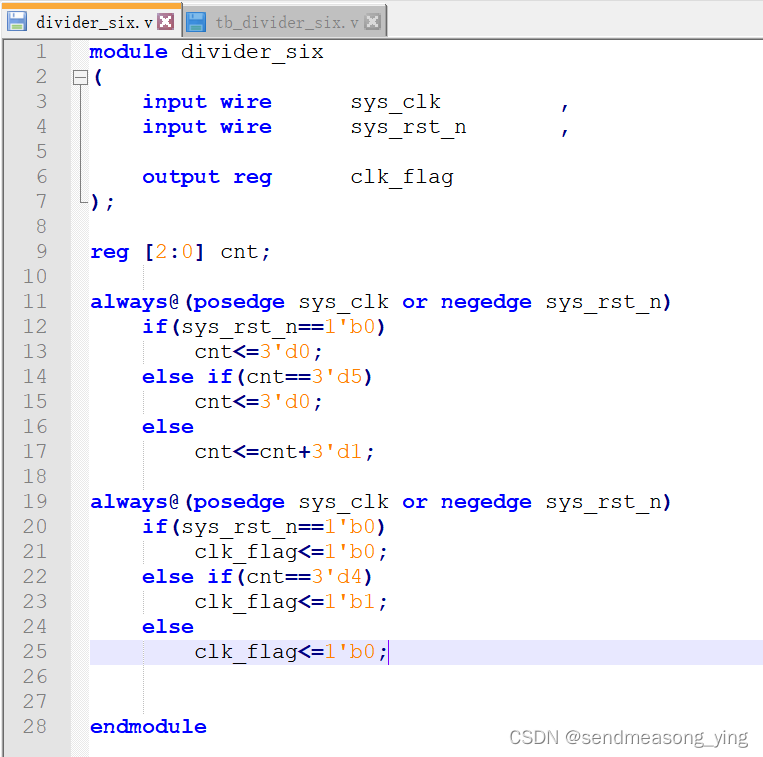

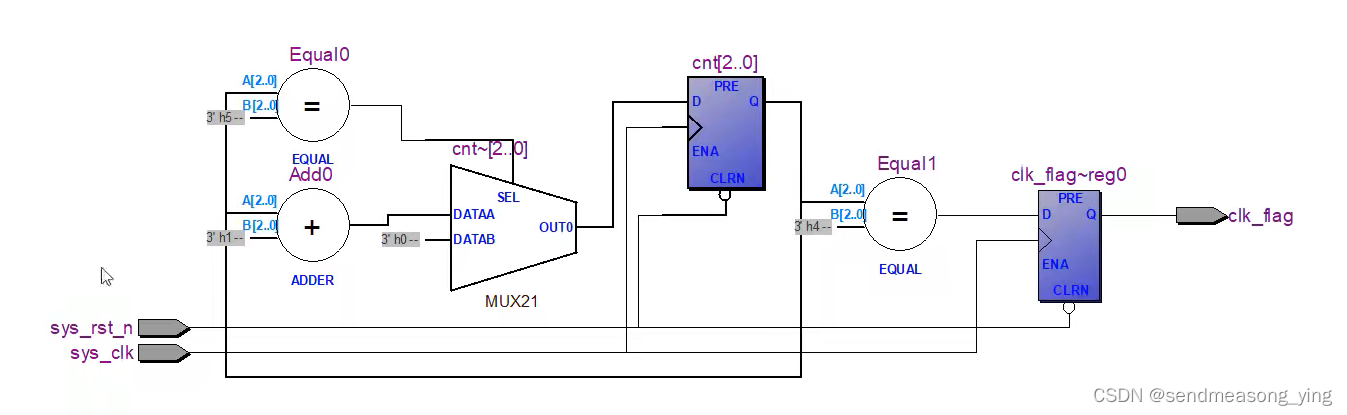

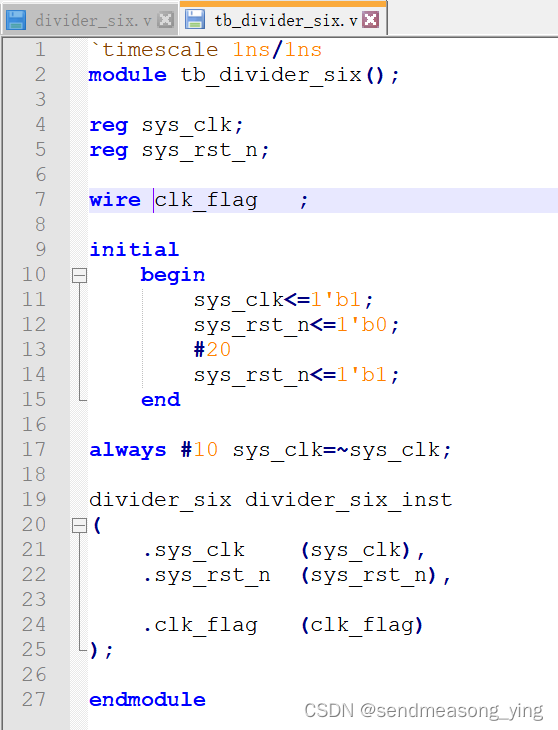

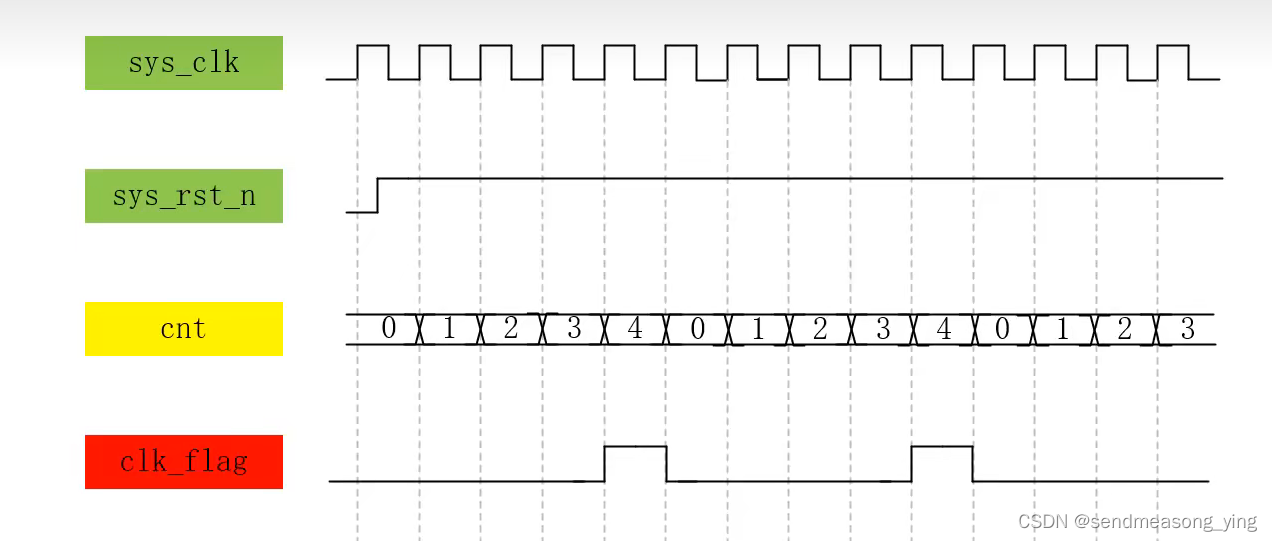

1.2 改进偶分频,使用脉冲标志信号

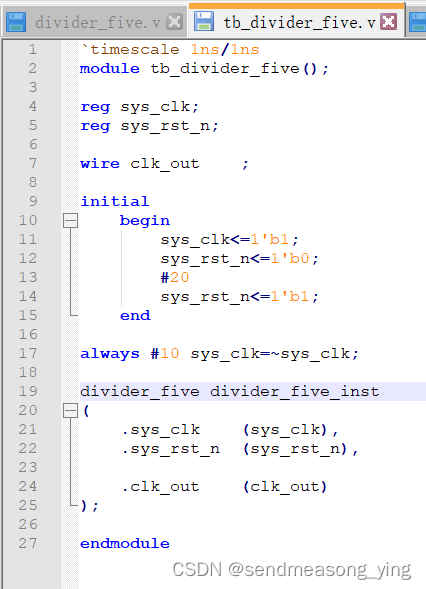

第二种写法:

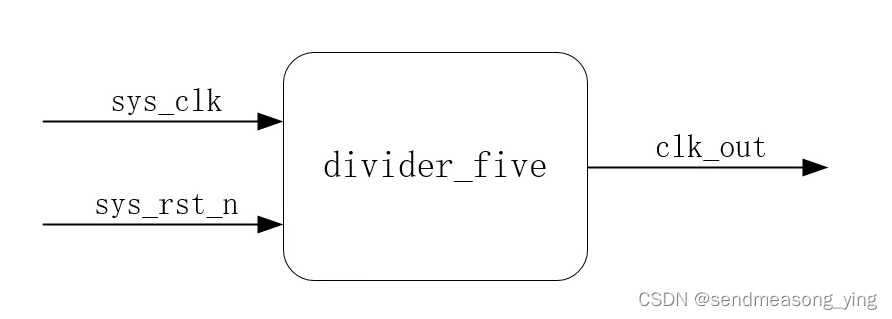

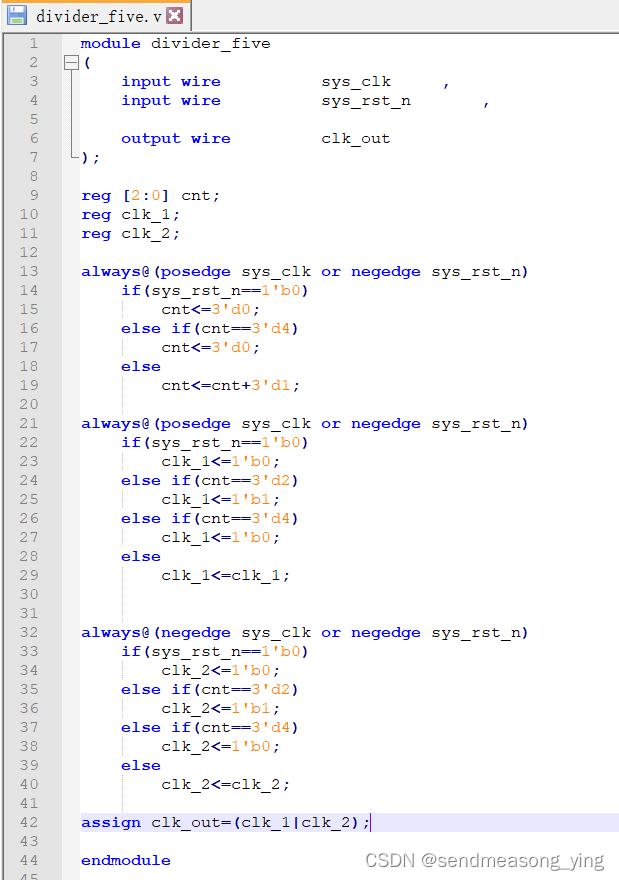

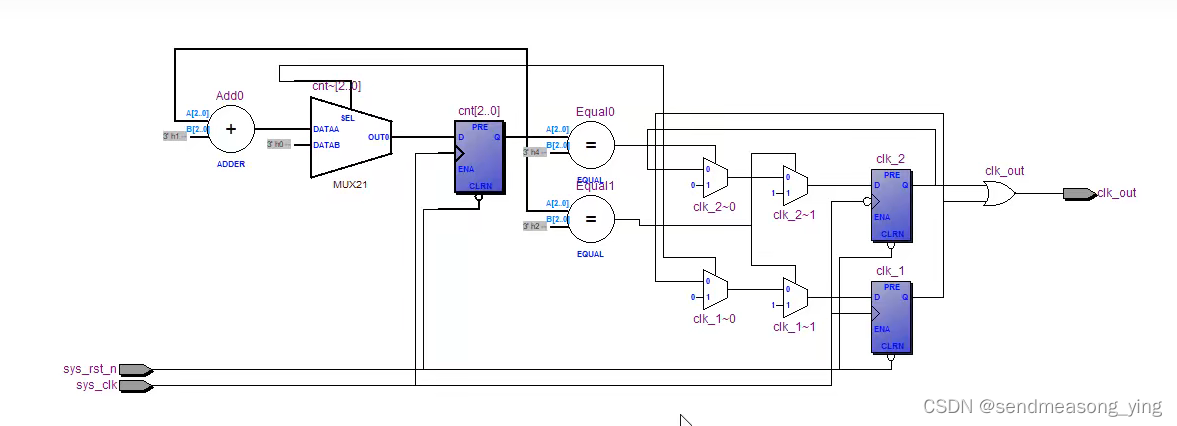

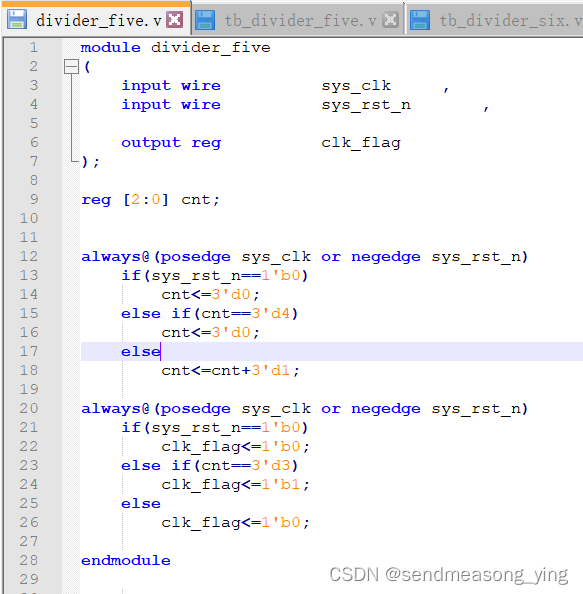

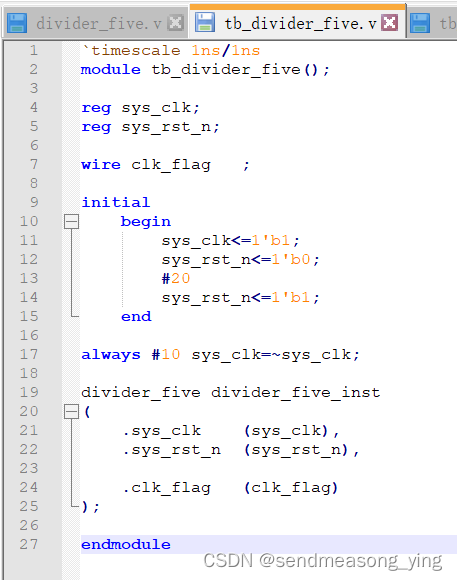

2.奇分频

2.1方法1

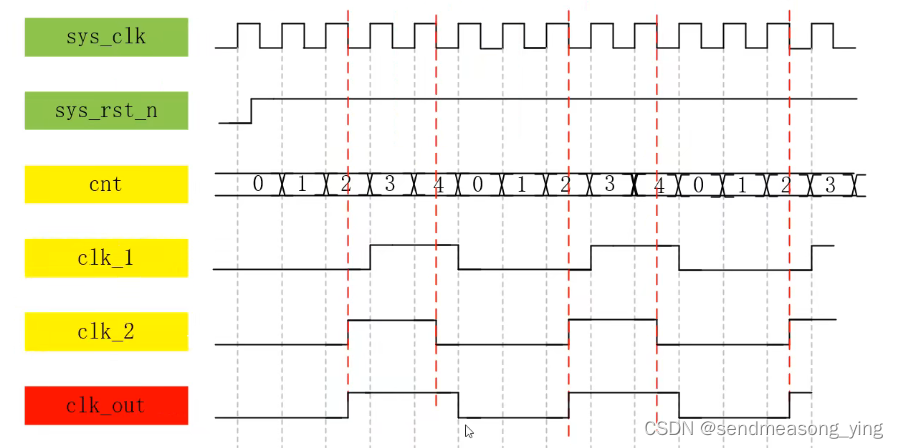

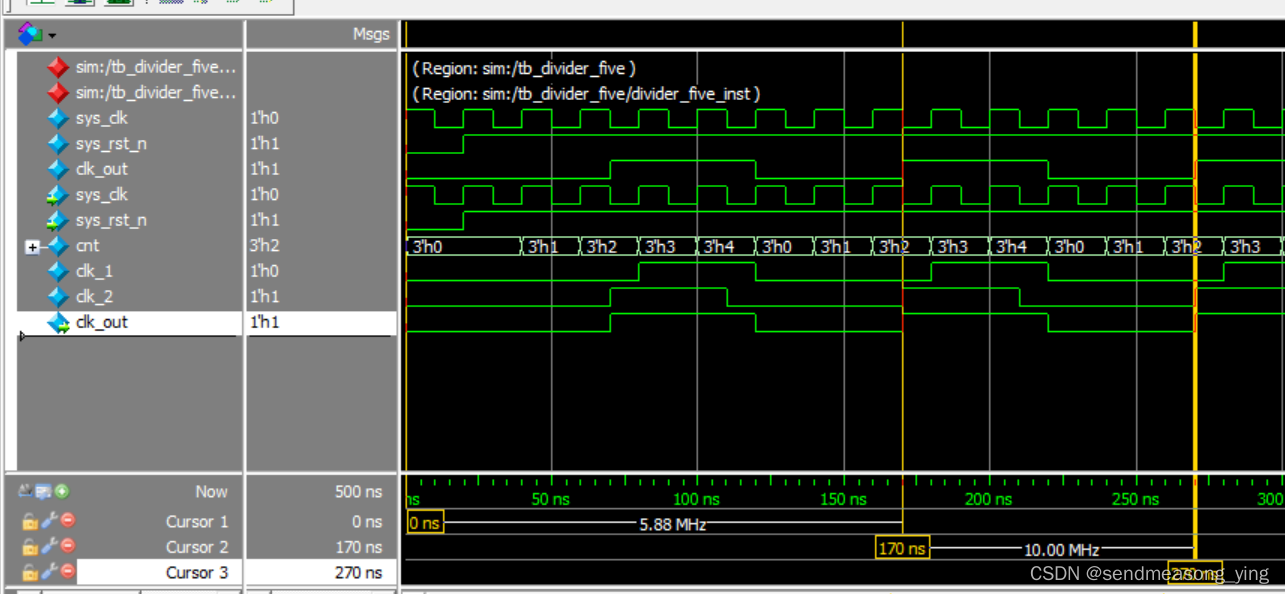

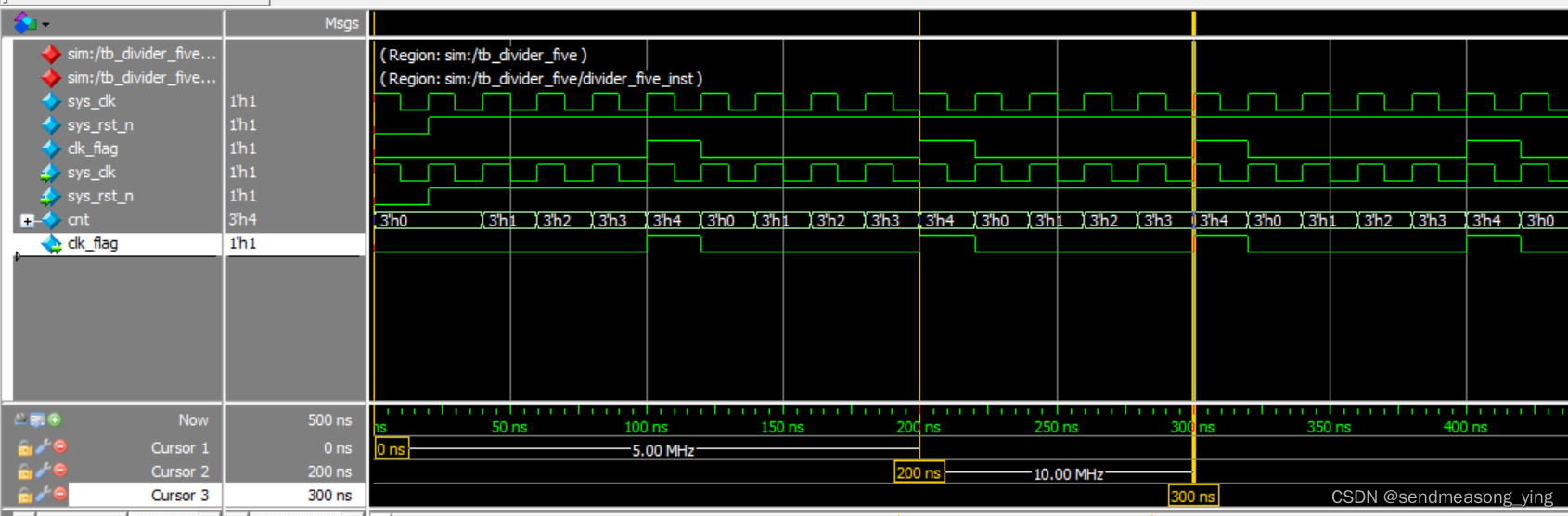

ctrl+a对波形全选,ctrl+g对波形分组

可以看出周期为10MHZ,是50MHZ的5分频

2.2 方法2

442

442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?