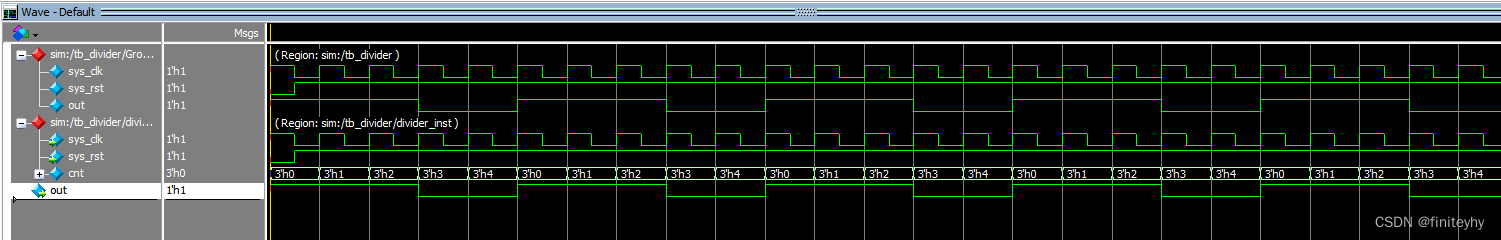

仅使用分频方式

module divider

(

input wire sys_clk,

input wire sys_rst,

output reg out

);

reg [2:0] cnt;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

cnt <= 3'd0;

else if (cnt == 3'd4)

cnt <= 3'd0;

else

cnt <= cnt + 3'd1;

always@(posedge sys_clk or negedge sys_rst)

if(sys_rst == 1'b0)

out <= 1'b1;

else if(cnt == 3'd2)

out <= 1'b0;

else if(cnt == 3'd4)

out <= 1'b1;

else

out <= out;

endmodule`timescale 1ns/1ns

module tb_divider();

reg sys_clk;

reg sys_rst;

wire out;

initial

begin

sys_clk <= 1'b1;

sys_rst <= 1'b0;

#10

sys_rst <= 1'b1;

end

always #10 sys_clk <= ~sys_clk;

divider divider_inst

(

. sys_clk(sys_clk) ,

. sys_rst(sys_rst) ,

. out (out )

);

endmodule占空比为40% 五分频

采用分频方式

RTL视图

module divider_five

(

input wire sys_clk,

input wire sys_rst_n,

output wire clk_out

);

reg [2:0] cnt;

reg clk_1;

reg clk_2;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 3'd0;

else if(cnt == 3'd4)

cnt <= 3'd0;

else

cnt <= cnt + 1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_1 <= 1'b0;

else if (cnt == 3'd2)

clk_1 <= 1'b1;

else if(cnt == 3'd4)

clk_1 <= 1'b0;

else

clk_1 <= clk_1;

always@(negedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_2 <= 1'b0;

else if (cnt == 3'd2)

clk_2 <= 1'b1;

else if(cnt == 3'd4)

clk_2 <= 1'b0;

else

clk_2 <= clk_2;

assign clk_out = (clk_1 | clk_2) ;

endmodule `timescale 1ns/1ns

module tb_divider_five();

reg sys_clk;

reg sys_rst_n;

wire clk_out;

initial

begin

sys_clk <=1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

divider_five divider_five_inst

(

. sys_clk (sys_clk),

. sys_rst_n(sys_rst_n),

. clk_out (clk_out)

);

endmodule

采用降频方式

module divider_five

(

input wire sys_clk,

input wire sys_rst_n,

output reg clk_flag

);

reg [2:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt <= 3'd0;

else if(cnt == 3'd4)

cnt <= 3'd0;

else

cnt <= cnt + 3'd1;

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

clk_flag <= 1'b0;

else if(cnt==3'd3)

clk_flag <= 1'b;

else

clk_flag <=1'b0;

assign clk_out = (clk_1 | clk_2) ;

endmodule `timescale 1ns/1ns

module tb_divider_five();

reg sys_clk;

reg sys_rst_n;

wire clk_flag;

initial

begin

sys_clk <=1'b1;

sys_rst_n <= 1'b0;

#20

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk;

divider_five divider_five_inst

(

. sys_clk (sys_clk),

. sys_rst_n(sys_rst_n),

. clk_flag (clk_flag)

);

endmodule

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?