2.1 设计输⼊

1. 模块名称:latch 和 D_flip_flop

2. 输⼊输出:CLK、 D、 Q

2.2 引脚约束

1. 输⼊端 ⾃定义

2. 输出端 ⾃定义

2.3 设计要求

1. 分别实现latch 和 D_flip_flop电路,并增加置数(SET)和清零(CLRn)功能

2. 使⽤RTL View分析电路的区别

2.4 电路仿真1. 使⽤ModelSim仿真

(1)D触发器设计:

1.设计代码:

module D_flip_flop(CLK,D,Q,CLRn,SET);

input CLK,D,CLRn,SET;

output reg Q;

always @ (posedge CLK or negedge CLRn or negedge SET)

begin

if(~CLRn)

Q<=1'b0;

else if(~SET)

Q<=1'b1;

else

Q<=D;

end

endmodule

.使用专用工具Modelsim仿真:

1.两个文件:D_flip_flop.v 和 D_flip_flop_tb.v (前者是源文件,后者是测试仿真文件testbench)

D_flip_flop_tb.v代码如下:

`timescale 1ns/1ns

module D_flip_flop_tb1;

reg clk,d,clrn,setn;

wire q;

D_flip_flop U1(.CLK(clk),

.D(d),

.Q(q),

.CLRn(clrn),

.SET(setn));

always #10 clk=~clk;

always #40 d = ~d;

initial begin

clk=0;

d=0;

clrn=0;

setn=0;

#30 setn=1;

#20 clrn=1;

end

endmodule

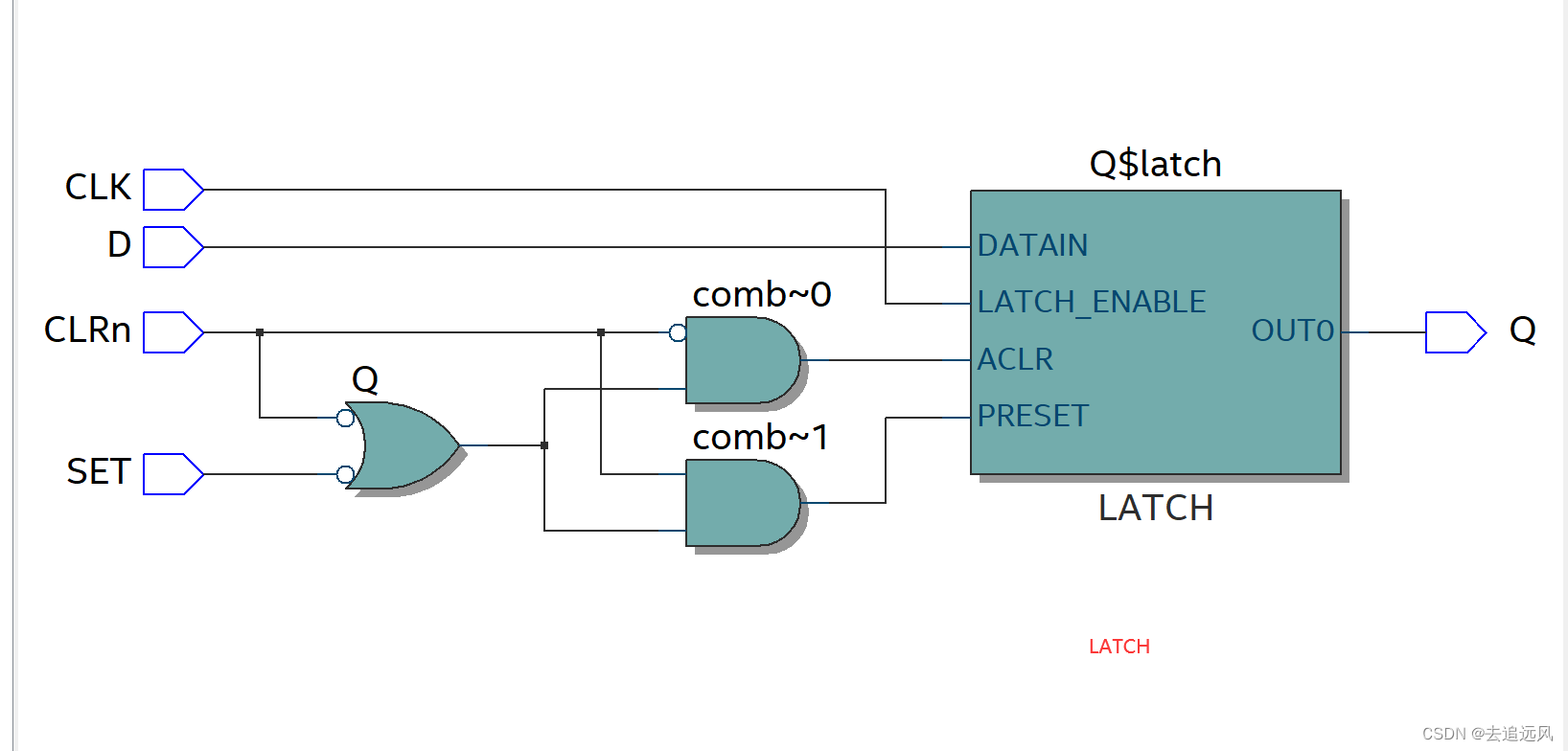

(2)锁存器Latch

1.设计代码:

module shiyan9_Latch(CLK,D,Q,CLRn,SET);

input CLK,D,CLRn,SET;

output reg Q;

always @ (CLK or CLRn or SET or D)

begin

if(~CLRn)

Q<=1'b0;

else if(~SET)

Q<=1'b1;

else if(CLK)

Q<=D;

end

endmodule

D触发器和锁存器是有很大区别的:

1.D触发器是对信号边沿敏感(pos或者neg) 【RTL中用到了寄存器reg,信号时钟CLK有三角标志】

2. 锁存器Latch是对高低电平敏感 【RTL中 LATCH的使能端接的是 CLK,为高低电平0或1】

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?