赋值语法

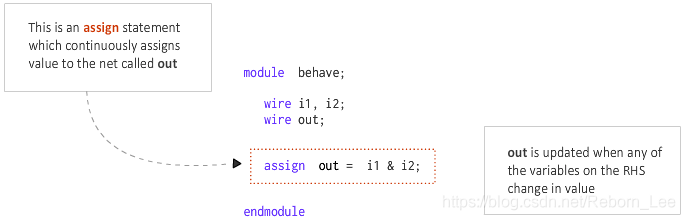

赋值语法以关键字assign开头,后面是信号名,可以是单个信号,也可以是不同信号网的连接。驱动强度和延迟是可选的,主要用于数据流建模,而不是综合到实际硬件中。右侧的表达式或信号被分配给左侧的网或网的表达式。

语法结构如下:

assign <net_expression> = [drive_strength] [delay] <expression of different signals or constant value>

延迟值对于指定门的延迟很有用,并用于模拟实际硬件中的时序行为,因为该值决定了何时应该用评估值分配网。

使用 assign 语句时, 需要遵循一些规则:

- LHS(左值) 应该始终是wire类型的标量或向量网络, 或者标量或矢量网络的串联, 而绝对不能是reg类型的标量或矢量寄存器。

- RHS 可以包含标量或向量寄存器以及函数调用。

- 只要 RHS 上的任何操作数的值发生变化, LHS 就会使用新值进行更新。

- assign 语句也称为连续赋值, 并且始终处于活动状态

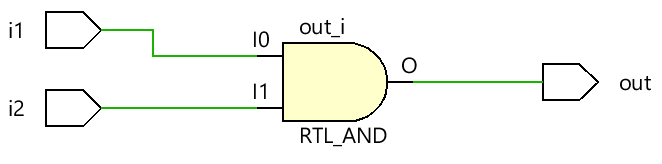

综合后的RTL图:

reg类型变量赋值

reg类型的变量不能使用assign进行连续赋值,这是因为reg类型的变量可以存储数据,并且不需要连续驱动。我们只能在initial以及always块内对reg类型变量进行赋值。

隐性连续赋值

当使用assign给wire类型的网络赋值时,称为显示连续赋值,如果在定义的时候就对其连续赋值,称为隐形连续赋值,隐形连续赋值在Verilog中是被允许的。

wire [1:0] a;

assign a = x & y; // Explicit assignment

wire [1:0] a = x & y; // Implicit assignment

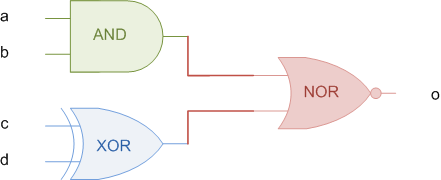

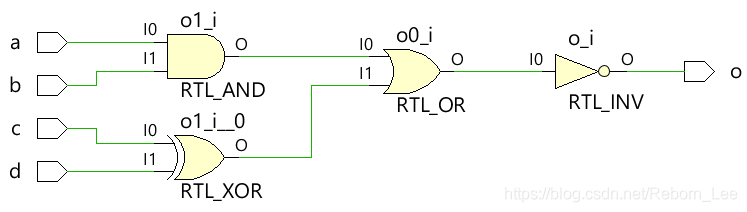

组合逻辑设计

assign语句常用于组合逻辑设计,如下的电路图:

module combo ( input a, b, c, d,

output o);

assign o = ~((a & b) | (c ^ d));

endmodule

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?