设计实现模十计数器并通过开发板的数码管显示计数

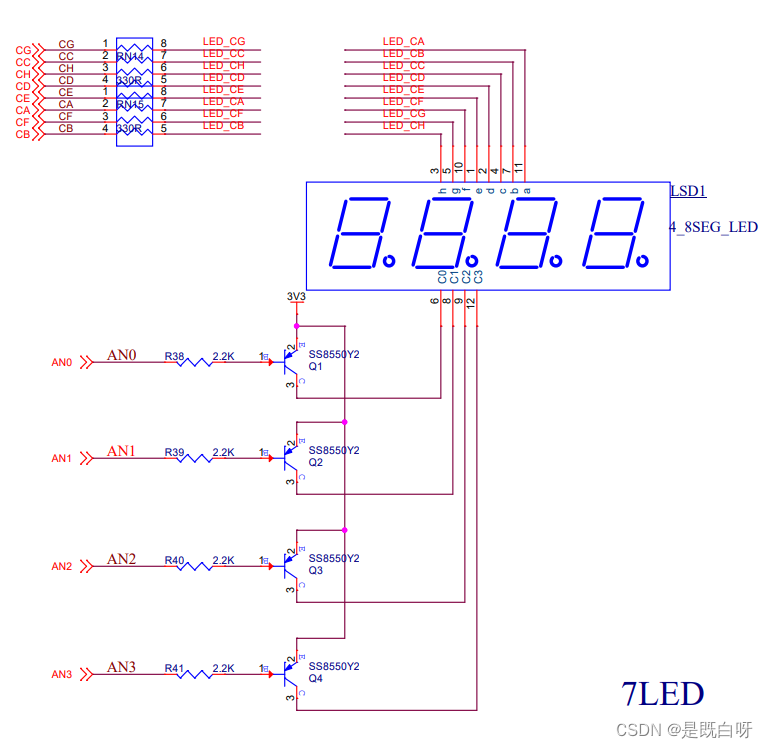

一.开发板数码管

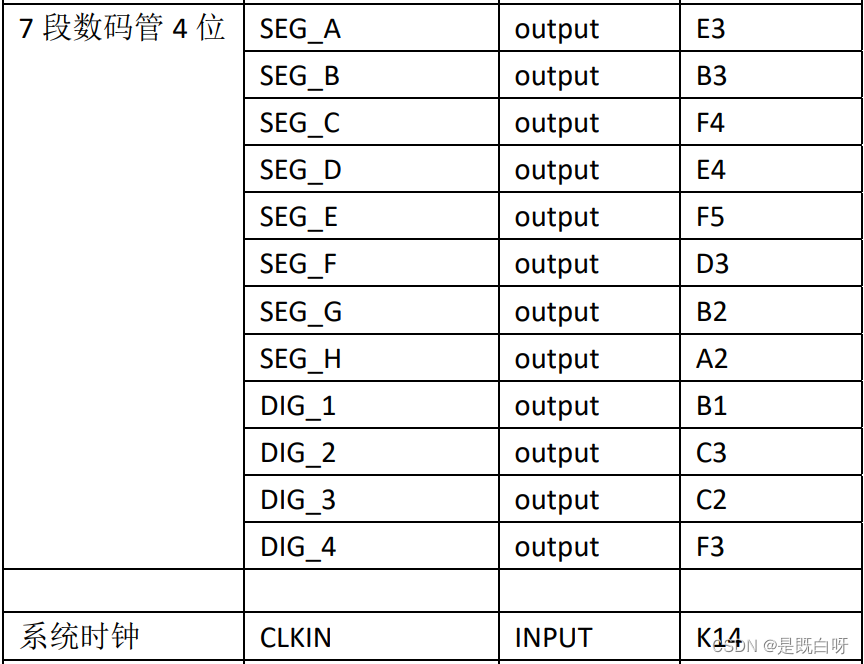

管脚配置:

开发板 FPGA 芯片左上方有 4 个七段共阳动态带点数码管,段码低电平有效,位码也是低电平有效。

二.Verilog代码实现

module counter10(clk_24M,seg,dig );

input clk_24M;

output [7:0]seg;

output [3:0]dig;

reg [7:0]seg;

reg [3:0]dig;

reg [7:0]Result;

reg [24:0]cnt;

reg clk_1;

initial dig=4'b1110;//位码低电平有效 选中第四位数码管

always@(posedge clk_24M)//进行时钟分频 产生1Hz的时钟clk_1

begin

if(cnt==25'd12_000_000-1)

begin

cnt<=25'd0;

clk_1<=~clk_1;

end

else

begin

cnt<=cnt+1;

clk_1<=clk_1;

end

end

always@(posedge clk_1)

begin

if(Result[3:0]==4'd9)

begin

Result[3:0]<=0;

end

else

Result[3:0]<=Result[3:0]+1'b1;

end

always@(*)

begin

case(Result[3:0])

4'd0: seg=8'b1100_0000;//0

4'd1: seg=8'b1111_1001;//1

4'd2: seg=8'b1010_0100;//2

4'd3: seg=8'b1011_0000;//3

4'd4: seg=8'b1001_1001;//4

4'd5: seg=8'b1001_0010;//5

4'd6: seg=8'b1000_0010;//6

4'd7: seg=8'b1111_1000;//7

4'd8: seg=8'b1000_0000;//8

4'd9: seg=8'b1001_0000;//9

default: seg=8'b1100_0000;

endcase

end

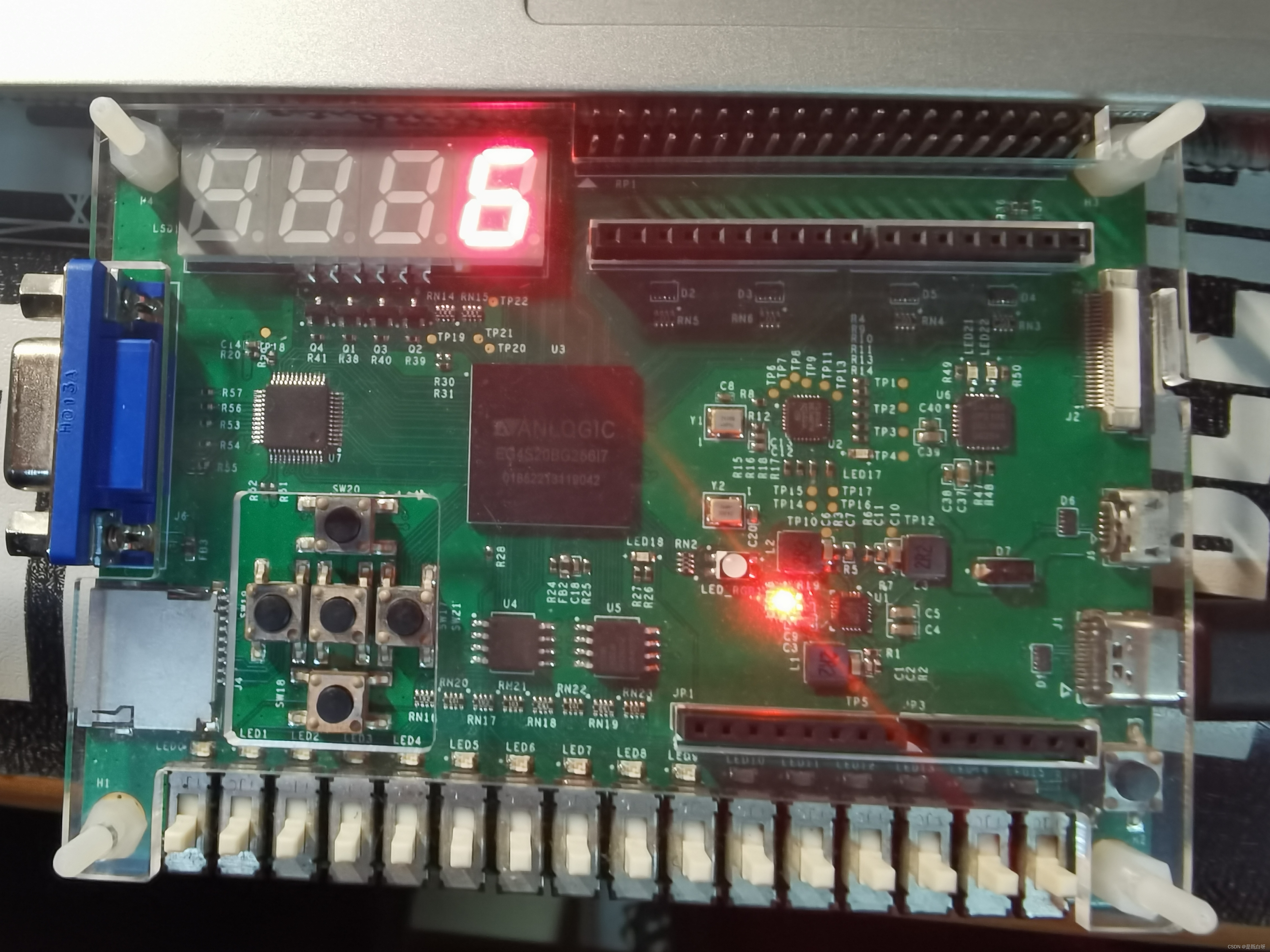

endmodule三.运行烧录结果

1330

1330

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?