题目:

设计实现一个可容纳四组选手参赛的抢答器系统,每组设一个抢答按钮。答题开始后,由主持人按下“复位”键(开始键)后进入抢答环节,当某个小组抢答成功时,抢答器系统发出半秒的低频音(DO),显示该组别序号并点亮该组“选手指示灯”直至系统复位。此时进入答题计时环节,若超过 30 秒仍未答出,抢答器系统发出 1 秒的高频音(SI)示警。由裁判员按下“复位”键,开始新一轮答题。

一. 模块设计

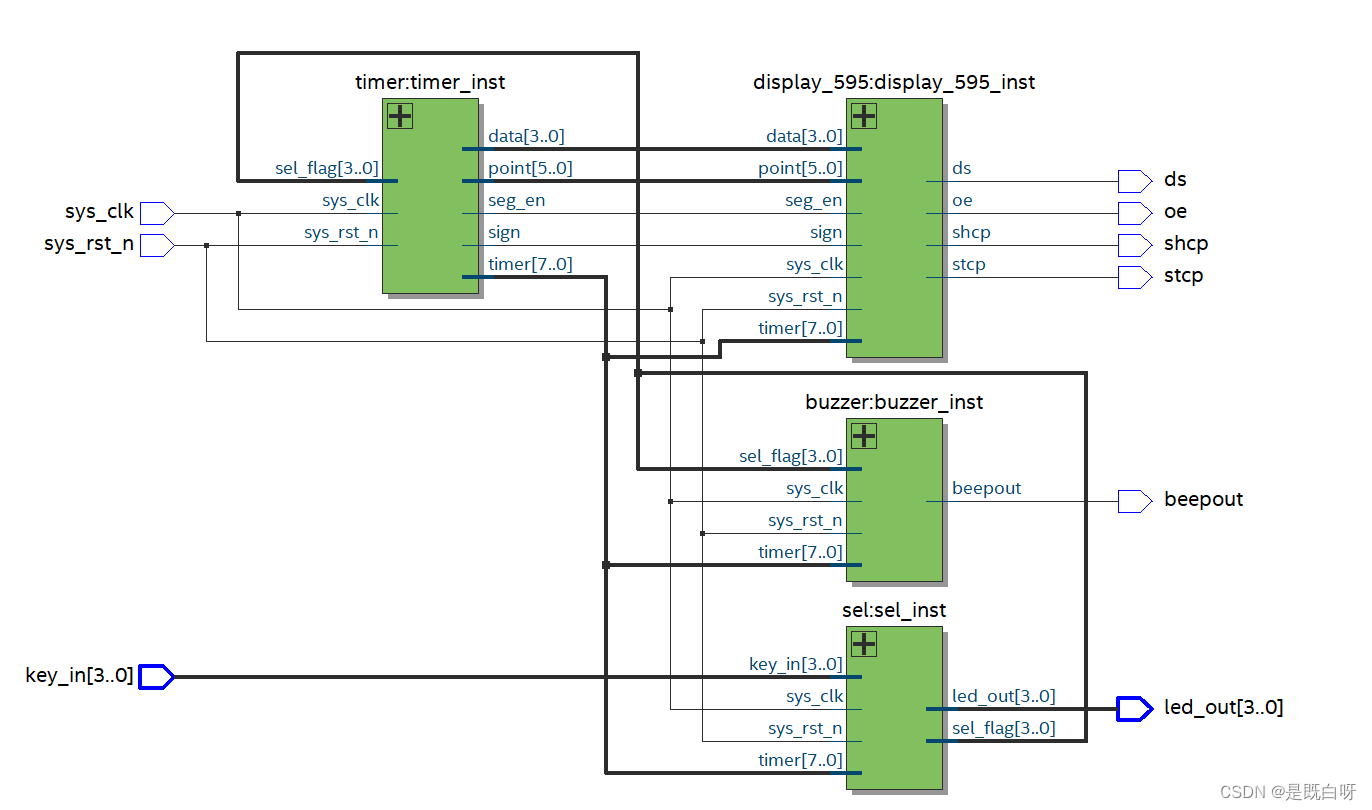

本实验设计实现一个抢答器系统,主要由答题计时模块timer,数码管显示模块display_595,蜂鸣器发声模块buzzer,抢答模块sel,按键消抖模块key_filter和顶层模块responder。

其中display_595模块中包含对display模块以及hc595_ctrl模块的例化。

整体模块框图输入输出信号如下图所示:

输入信号:系统时钟sys_clk, 复位信号sys_rst_n,四路抢答器按键信号key_in[3:0],蜂鸣器驱动信号beepout,数码管显示驱动信号stcp,shcp,ds,oe,以及选手指示灯信号 led_out[3:0]。

二. FPGA硬件电路原理图

1. 六位八段数码管

其具体使用方法见文章:Altera EP4CE10 征途Pro开发板数码管显示原理(以实现模60计数器为例)-CSDN博客

2. 无源蜂鸣器buzzer

相对于有源蜂鸣器,无源蜂鸣器的成本更低,声音频率可控。而有源蜂鸣器因其内部自带振荡源,只要加上适当的直流电源即可发声,程序控制较为方便。无源蜂鸣器与有源蜂鸣器不同,因其内部不带震荡源,所以其无法向有缘蜂鸣器那样直接用直流信号驱动,这里需要使用PWM方波才能驱动其发声。

其具体使用方法见文章:无源蜂鸣器的驱动实验-CSDN博客

3. 按键key

开发板上使用的机械按键也是按键的一种,特点是:接触电阻小 ,手感好,按键按下或弹起时有“滴答”清脆声;但由于其构造和原理,在按键闭合及断开的瞬间均伴随有一连串的抖动。

具体按键消抖方法的设计请参阅文章:按键消抖模块设计实现-CSDN博客

三. Verilog程序设计

1. 答题计时模块timer

当有人抢答时,计时器进入三十秒的倒计时,从30计到00。sel_flag表示抢答信号。

模块内包含一个分频器,产生一秒的标准脉冲clk1。

核心代码如下:

always@( posedge clk1 or negedge sys_rst_n )

if( sys_rst_n == 1'b0 )

begin

timer[7:4] <= 4'd3;

timer[3:0] <= 4'd0;

end

else if( sel_flag != 4'b1111 )

begin

if( timer[7:4] == 4'd0 && timer[3:0] == 4'd0 )

timer[7:0] <= timer[7:0] ;

else if( timer[3:0] == 4'd0 )

begin

timer[7:4] <= timer[7:4] - 1'b1 ;

timer[3:0] <= 4'd9;

end

else

timer[3:0] <= timer[3:0] - 1'b1 ;

end

else

timer[7:0] <= timer[7:0];

always @(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

begin

en <= 1'b1 ;

data <= 4'd0;

end

else if( en )

begin

case(sel_flag)

4'b1110:

begin

data <= 4'd1;

en <= 1'b0;

end

4'b1101:

begin

data <= 4'd2;

en <= 1'b0;

end

4'b1011:

begin

data <= 4'd3;

en <= 1'b0;

end

4'b0111:

begin

data <= 4'd4;

en <= 1'b0;

end

default: data <= 4'd11;

endcase

end2. 蜂鸣器发声模块buzzer

当有人抢答时,发出半秒的低频音;答题时间超时时,发出一秒的高频音。

核心代码如下:

module buzzer

(

input wire sys_clk ,

input wire sys_rst_n ,

input wire [7:0] timer ,

input wire [3:0] sel_flag ,

output reg beepout

);

parameter DO = 18'd190840 ;

para

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4098

4098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?