题目:

设计一个模块,通过任务完成3个8位2进制输入数据的冒泡排序。要求:时钟触发任务的执行,每个时钟周期完成一次数据交换的操作。

Verilog代码:

module sort(

input sys_clk,

input sys_rst,

input [7:0] a,

input [7:0] b,

input [7:0] c,

output reg [7:0] max,

output reg [7:0] mid,

output reg [7:0] min

);

localparam S0 = 5'b00001,

S1 = 5'b00010,

S2 = 5'b00100,

S3 = 5'b01000,

S4 = 5'b10000;

reg [4:0] state;

reg [7:0] a_temp = 0;

reg [7:0] b_temp = 0;

reg [7:0] c_temp = 0;

always @ (posedge sys_clk or posedge sys_rst)begin

if(sys_rst == 1'b1)begin

max <= 8'b0;

mid <= 8'b0;

min <= 8'b0;

state <= S0;

end

else case(state)

S0 :begin

a_temp <= a;

b_temp <= b;

c_temp <= c;

state <= S1;

end

S1 :begin

sort2(a_temp,b_temp);

state <= S2;

end

S2 :begin

sort2(c_temp,b_temp);

state <= S3;

end

S3 :begin

sort2(a_temp,c_temp);

state <= S4;

end

S4 :begin

max <= b_temp;

mid <= c_temp;

min <= a_temp;

state <= S0;

end

default :

state <= S0;

endcase

end

task sort2;

inout [7:0] x,y;

reg [7:0] temp;

if(x>y)begin

temp = x;

x = y;

y = temp;

end

endtask

endmodule

test bench:

`timescale 1ns/1ps

module tb;

reg clk,rst;

reg [7:0] a,b,c;

wire[7:0] max,mid,min;

initial begin

clk = 0;

rst = 1;

a = 0;

b = 0;

c = 0;

#40

rst = 0;

a = 14;

b = 12;

c = 37;

#60

a = 2;

b = 15;

c = 3;

end

always #5 clk = ~clk;

sort u_sort(

.sys_clk ( clk ),

.sys_rst ( rst ),

.a ( a ),

.b ( b ),

.c ( c ),

.max ( max ),

.mid ( mid ),

.min ( min )

);

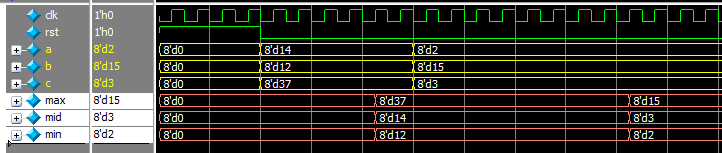

endmodule仿真结果:

后记

若有其他描述方式,欢迎讨论。

后续会继续更新verilog有意思的或可移植的模块。

512

512

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?