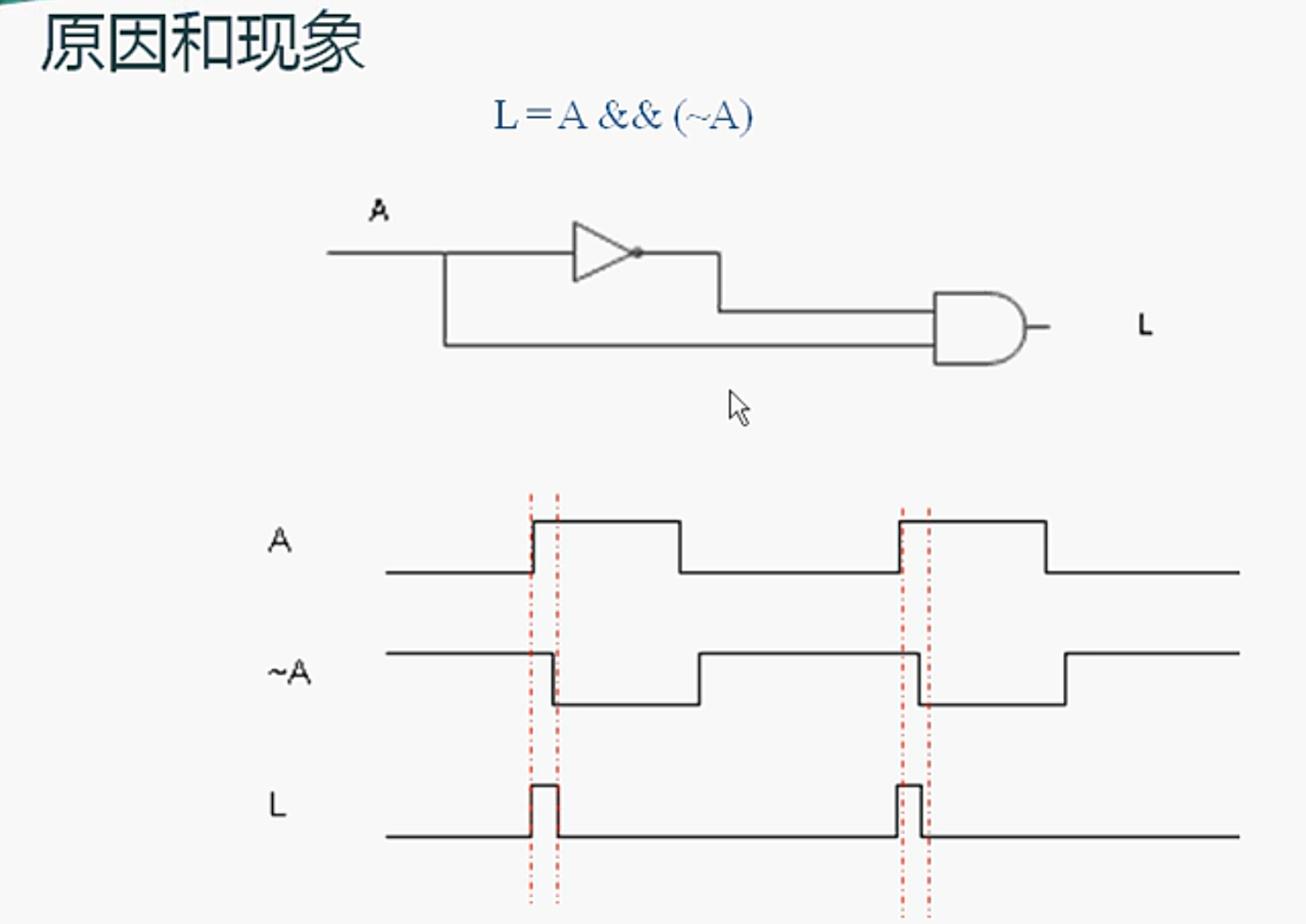

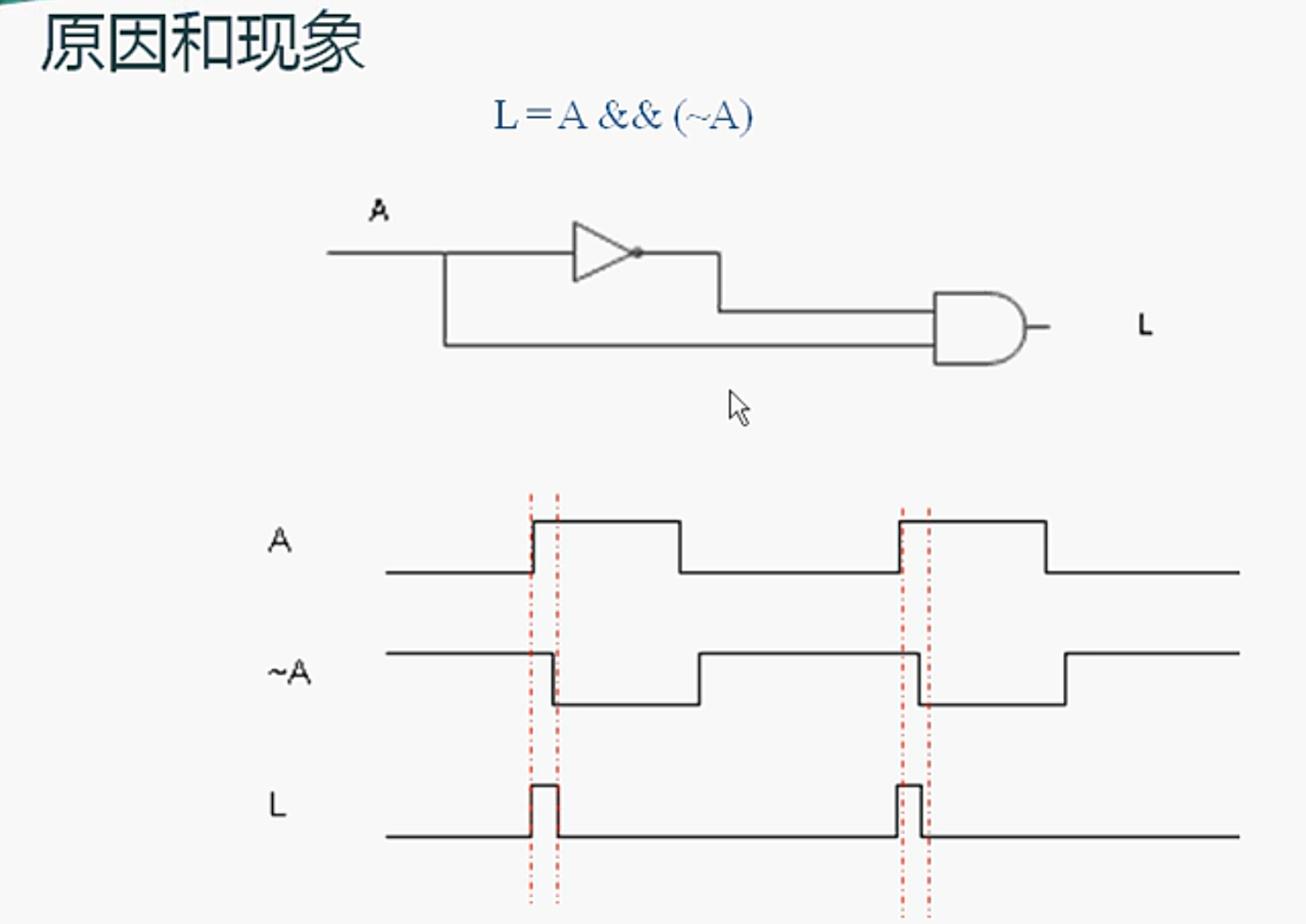

电路和器件中是存在延时的,~A中反相器的延迟,与A信号相与,产生毛刺。

不要试图去消除竞争冒险,组合逻辑中必定是有毛刺的。

解决方式:

- D触发器对竞争冒险不敏感;

- 组合逻辑不连接时钟、复位;

- 模块的输出通过寄存器延迟处理后输出。

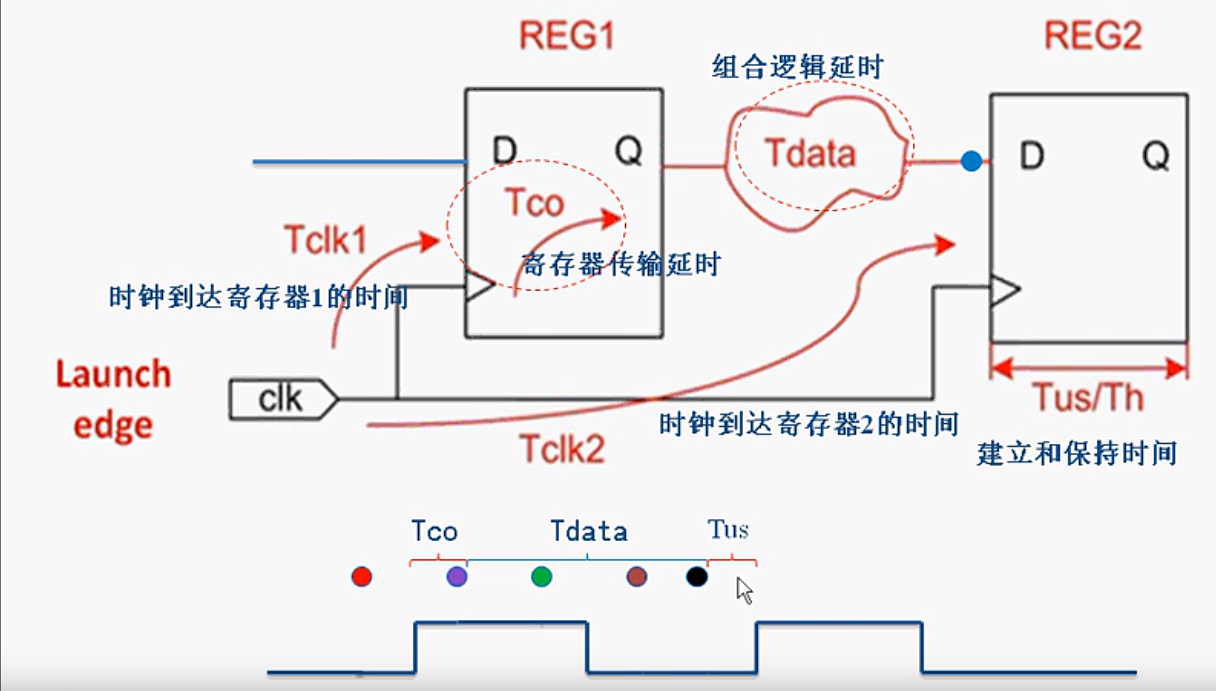

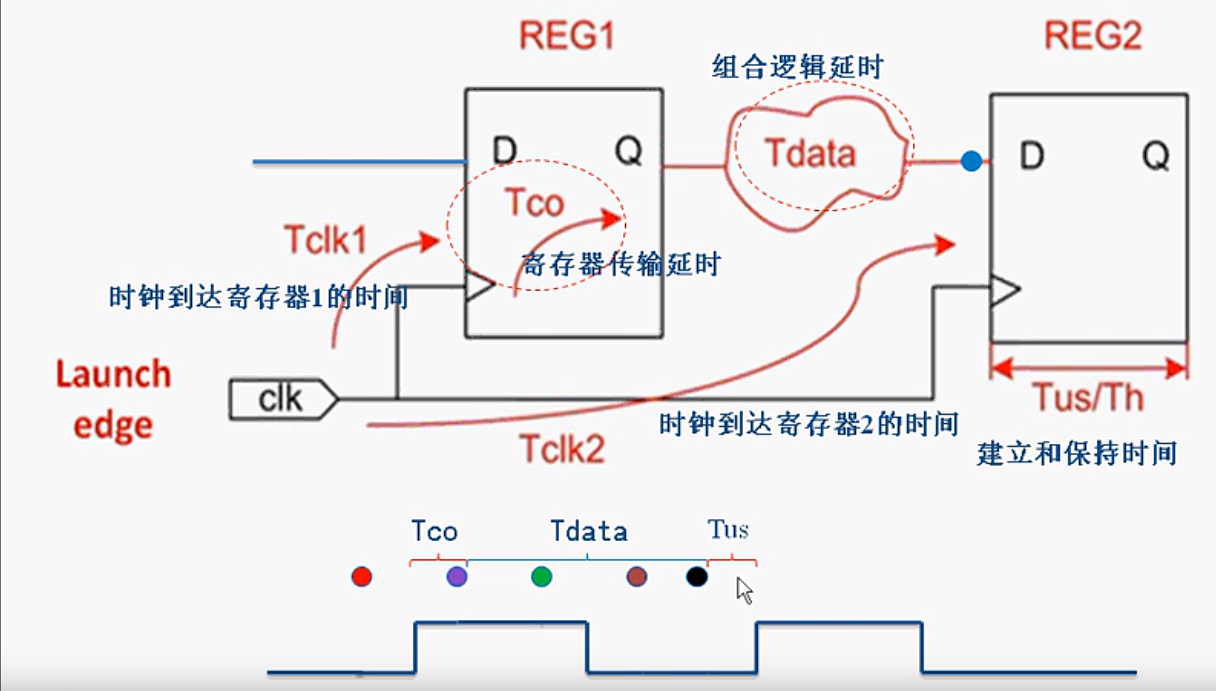

时钟周期的确定:

Tco + Tdata + Tus = Tmin

寄存器传输延时 + 组合逻辑延时 + 建立和保持时间 = 最小时钟周期

提高时钟频率的做法:只能修改Tdata,即优化硬件实现过程

文章讨论了电路和器件中的延时问题,特别是反相器引起的毛刺现象。竞争冒险在组合逻辑中是不可避免的,但可以通过使用D触发器或在输出端添加寄存器延迟来处理。确定时钟周期需考虑Tco、Tdata和Tus,而提高时钟频率主要依赖于优化硬件实现过程。

文章讨论了电路和器件中的延时问题,特别是反相器引起的毛刺现象。竞争冒险在组合逻辑中是不可避免的,但可以通过使用D触发器或在输出端添加寄存器延迟来处理。确定时钟周期需考虑Tco、Tdata和Tus,而提高时钟频率主要依赖于优化硬件实现过程。

电路和器件中是存在延时的,~A中反相器的延迟,与A信号相与,产生毛刺。

不要试图去消除竞争冒险,组合逻辑中必定是有毛刺的。

解决方式:

时钟周期的确定:

Tco + Tdata + Tus = Tmin

寄存器传输延时 + 组合逻辑延时 + 建立和保持时间 = 最小时钟周期

提高时钟频率的做法:只能修改Tdata,即优化硬件实现过程

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?