竞争与冒险以及解决方法

①竞争

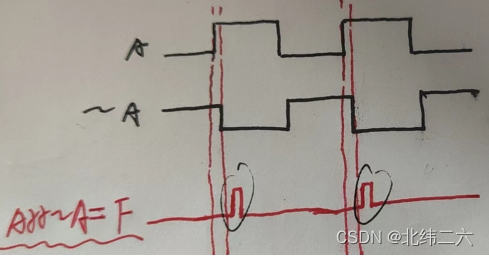

在门电路中,两个输入信号同时向相反方向的逻辑状态称之为竞争。具体如下图所示:

上图所示中,红线所绘制的部分,由于A信号与自身取反的信号~A信号实际上由于门电路等细微的延迟会出现两个信号的变化不是同步的,这种情况就叫竞争。这只是举一个简单的例子,只要两个信号经过不同的门电路,延时不同,都会出现竞争的关系。

②冒险

由竞争而引起的电路输出信号中出现了非预期信号称为冒险,表现为输出端出现了原设计中没有的窄脉冲,即毛刺。如下图所示:

上图所示,A&&~A会出现毛刺,该毛刺就是由组合逻辑所产生的的竞争引起的出现了,非预期的噪声。

解决方法:

1.最常用额方法是使用时序逻辑对组合逻辑输出的信号进行采样;类比与状态机中的state_n,state_c;其中state_c机位state_n采样得到的,同时第三段状态机可以使用state_c。

2.修改逻辑表达式,采用格雷码也可以,可以有效防止数据错乱,顶多也就是上一次的数据,数据不会出现大问题。

3.芯片输出外部并联电容消除窄脉冲。

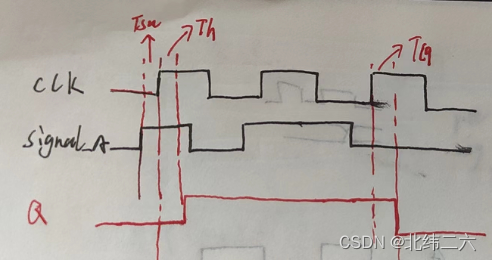

③建立时间与保持时间

建立时间(Tsu):时钟信号上升沿到来之前信号需要保持的时间。

保持时间(Th):时钟上升沿到来后,信号需要继续保持的时间。

寄存器输出延时时间(Tcq):上升沿采集到信号之后到寄存器输出引脚输出信号所耗费的时间。

组合逻辑延时输出延时时间(Tcomb):信号经过组合逻辑门电路输出所耗费的延时时间。

时钟偏移时间(Tskew):时钟从上一级到达下一级,因为时钟走过的路径延时时间。

④电路的最高运行频率

1.电路最高能跑快频率如何计算:

首先看上图的Q输出,如果要能正好满足下一级时钟的采样的话,那么该信号走过的链路求和为:

Tcq + Tcomb+Tsu-Tskew = 最高时钟周期

2.保持时间的概念:

Tcq+Tcomb >= Thd + Tskew

想象一下很容易可以解释如果不满足该条件的话,输出的信号,也就不满足下一个时钟对该信号采集时的保持时间了。

3.建立时间概念:

Tcq + Tsu +Tcomb <= Tclk + Tskew

A信号的建立时间和保持时间还有组合逻辑时间是一定要小于右侧的,否则下一个时钟采集该信号的组合逻辑输出值的时候就无法满足建立时间了。

总结:

1.建立时间决定了组合逻辑中的最大延时,保持时间决定了组合逻辑中的最小延时。

2.为了满足建立时间:增大时钟clk,增大skew,减小Tcq,减小Tcomb,总之为了数据可以早点出来被采集。

3.为了满足保持时间:增大Tcq,增大Tcomb,减小Tskew,总之为了数据可以晚点出来被采集。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?