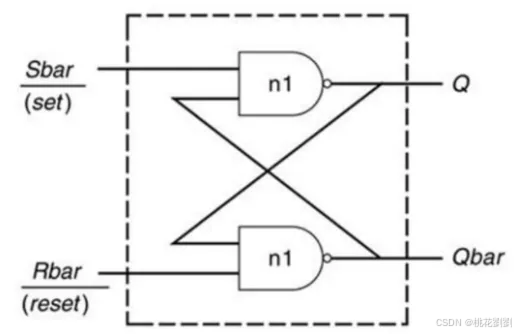

1 锁存器(Latch)

电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值。仅当锁存器处于使能状态时,输出才会随着数据输入发生变化。

当电平信号无效时,输出信号随输入信号变化,就像通过了缓冲器;当电平有效时,输出信号被锁存。激励信号的任何变化,都将直接引起锁存器输出状态的改变,很有可能会因为瞬态特性不稳定而产生振荡现象。

2 触发器(Flip-Flop)

边沿敏感的存储单元,数据存储的动作(状态转换)由某一信号的上升沿或者下降沿进行同步的(限制存储单元状态转换在一个很短的时间内)。

2.1 D触发器

module d_flip_flop(

input wire clk, // 时钟信号

input wire d, // 输入数据

output reg q // 输出数据

);

always @(posedge clk) begin

q <= d;

end

endmodule</

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4763

4763

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?