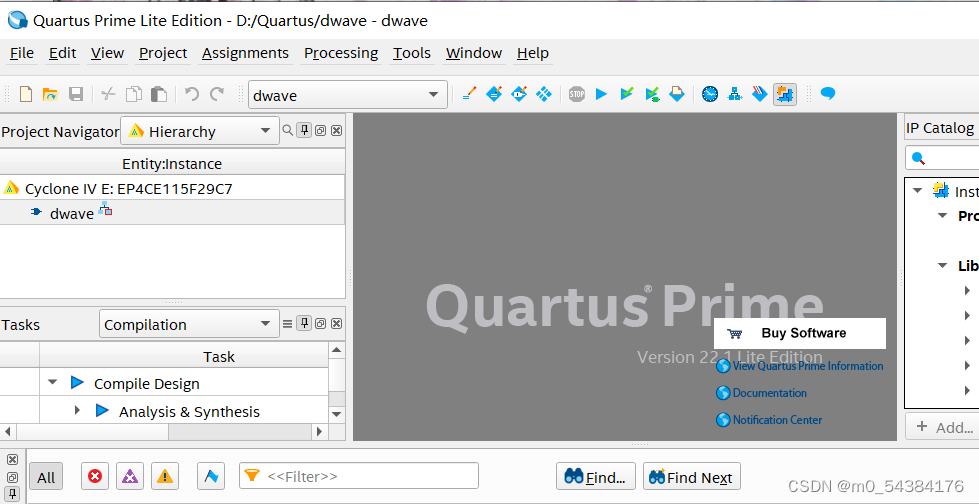

创建D触发器原理图并仿真

1.创建工程

File->New Project Wizard:

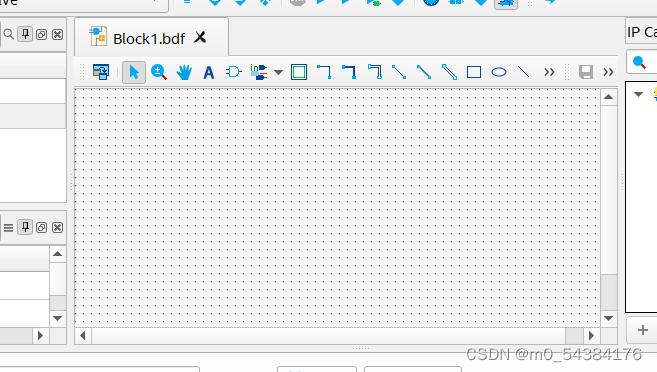

2.新建原理图文件

打开QuartusII,选菜单“File”一“New”,在弹出的“New-”对话框中选择“ Design Files” 的原理图文件编辑输入项“Block block diagram/schematic File"按"OK"后将打开原理图编辑窗。

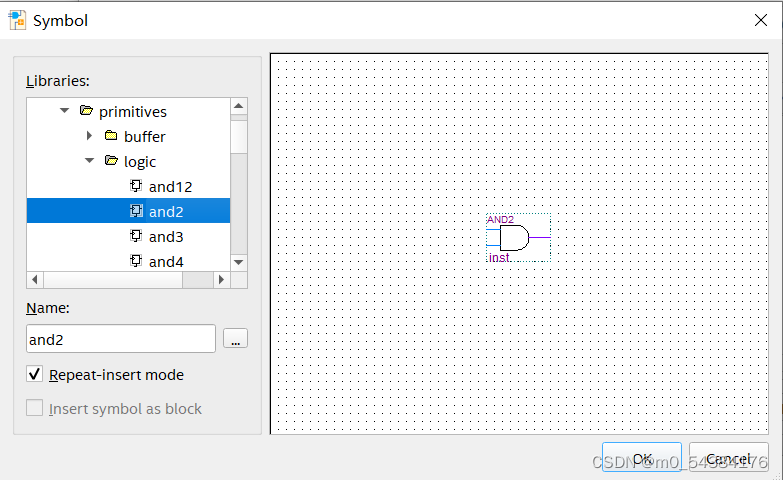

点击按纽“ Symbol Tool”或直接双击原理图空白处,从“ Symbol”窗中选择

需要的符号,或者直接在“name”文本框中键入元件名

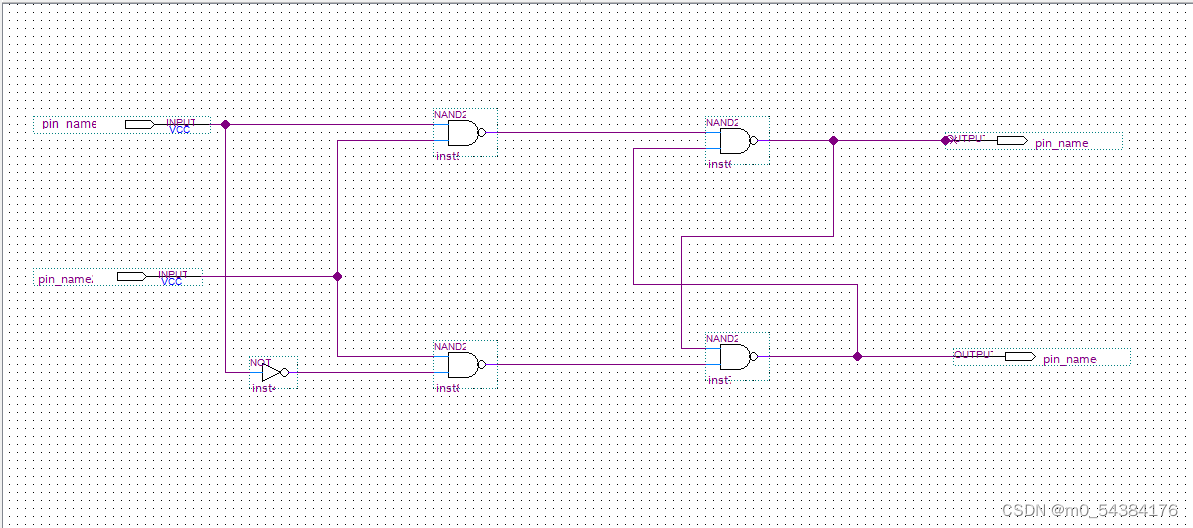

4 个 nand2 与非门,1 个 not 非门,2个输入管脚和2个输出管脚,并连线,最终如下图:

保存

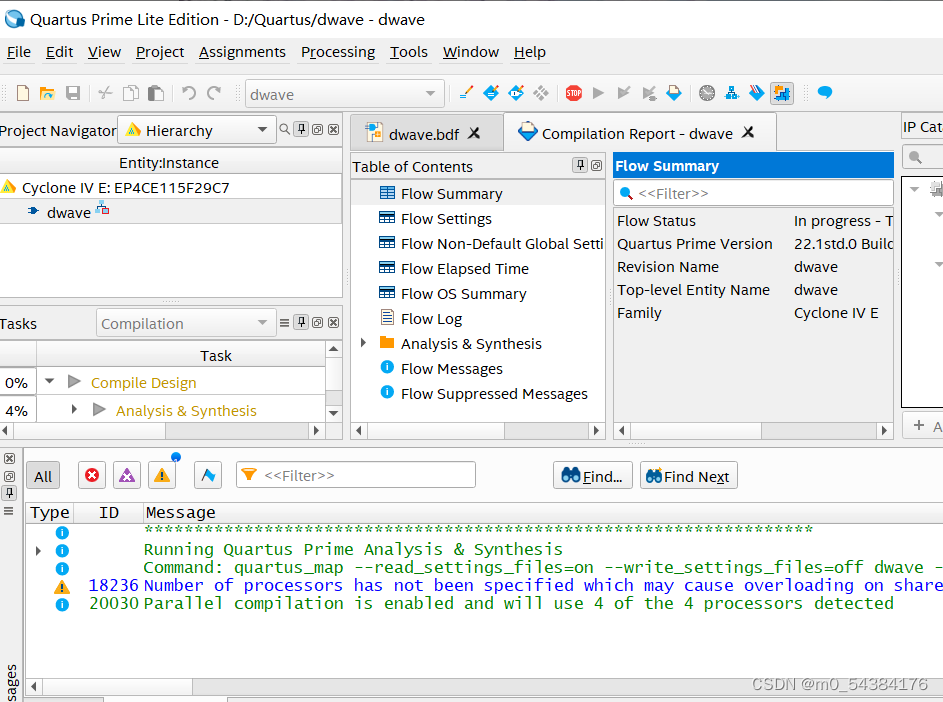

3.编译

进行编译,若无错误则可进行下一步,若有错进行原理图修改。

查看硬件电路图:点击【Tools】→【Netlist Viewers】→【RTL Viewer】。

4.仿真波形图

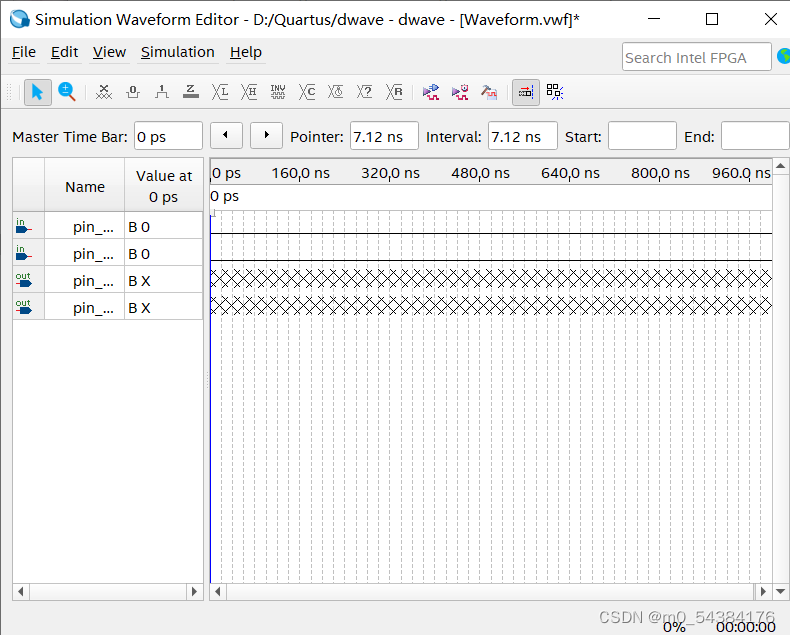

新建波形文件。如上面新建图形文件的方法,从“file”中选择“new”,然后从出现的对话框中选择“university program VWF”。

点击“OK”。

输入波形文件。在波形文件编辑器左端大片空白处双击,出现“insert node or bus”对话框,点击“node finder”按钮。如图。

然后在随后出现的“node finder”对话框中点击“list”按钮,则半加器中所有的输入输出引脚全部出现在对话框左边。再在该界面上点击“>>”,则把左边所有的端口都选择到右边,进入波形,如图。

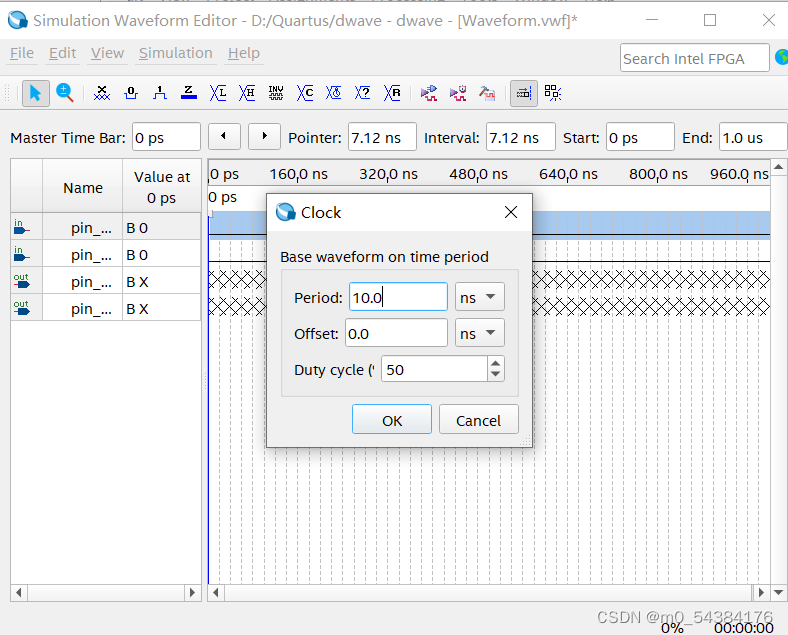

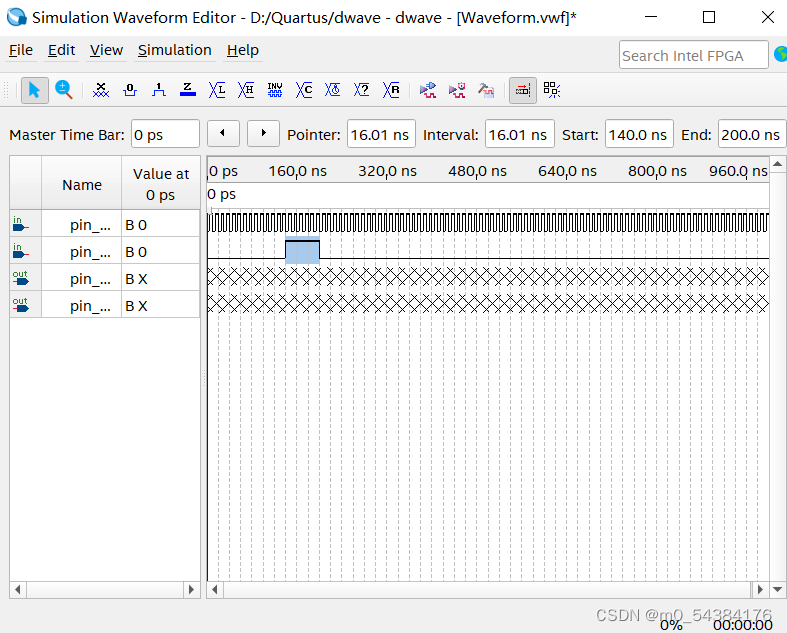

编辑输入CLK,产生时钟信号

把输入D随便设置几个低电平和高电平

保存文件:【File】→【Save】。

功能仿真

点击功能仿真编译按钮:

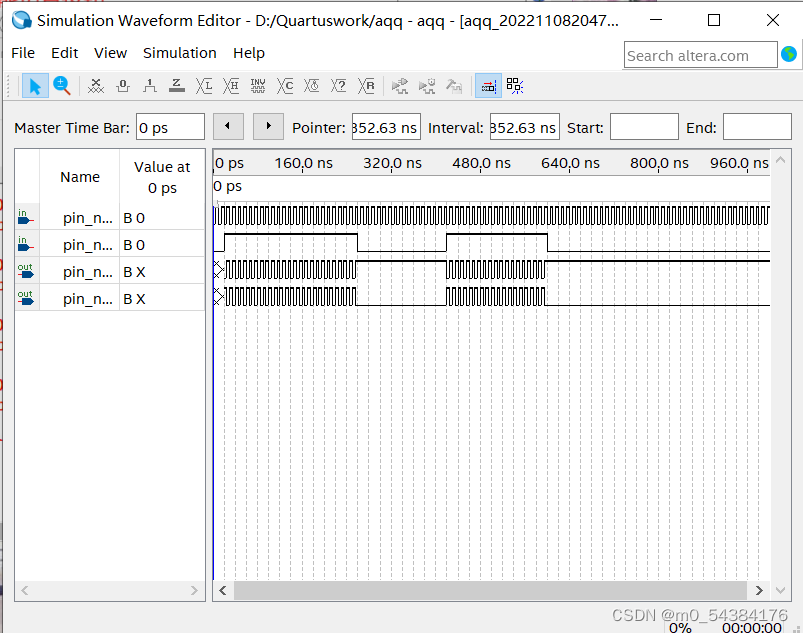

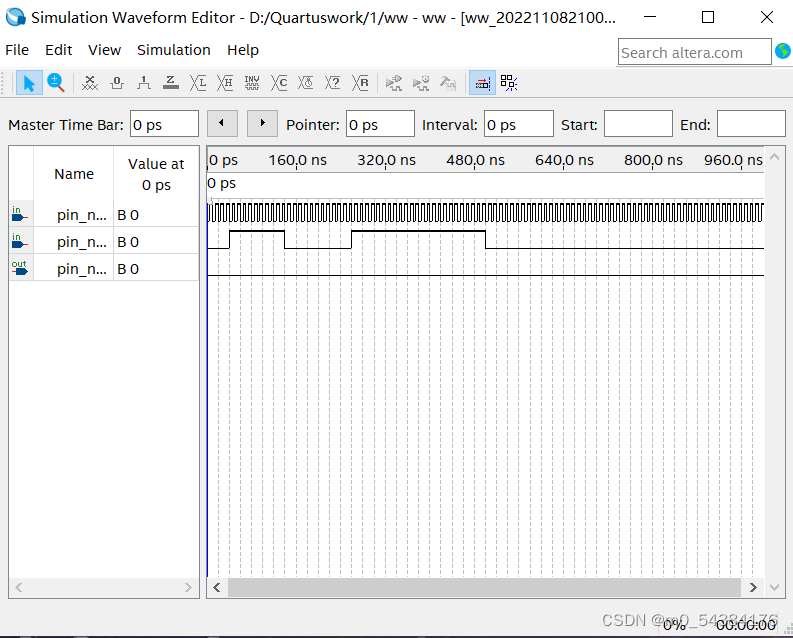

仿真结果如下(延迟了半个时钟周期):

功能仿真图:

调用D触发器并仿真

1.创建工程

与1.创建工程相同

2.新建原理图文件

方法同三、2.新建原理图文件

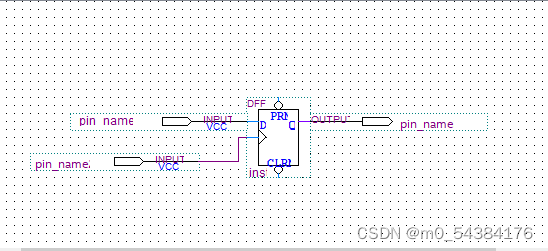

这时,不再画D触发器的内部结构了,而是直接调用D触发器,元件名:dff

再添加输入和输出管脚。最终原理图如下:

3.编译

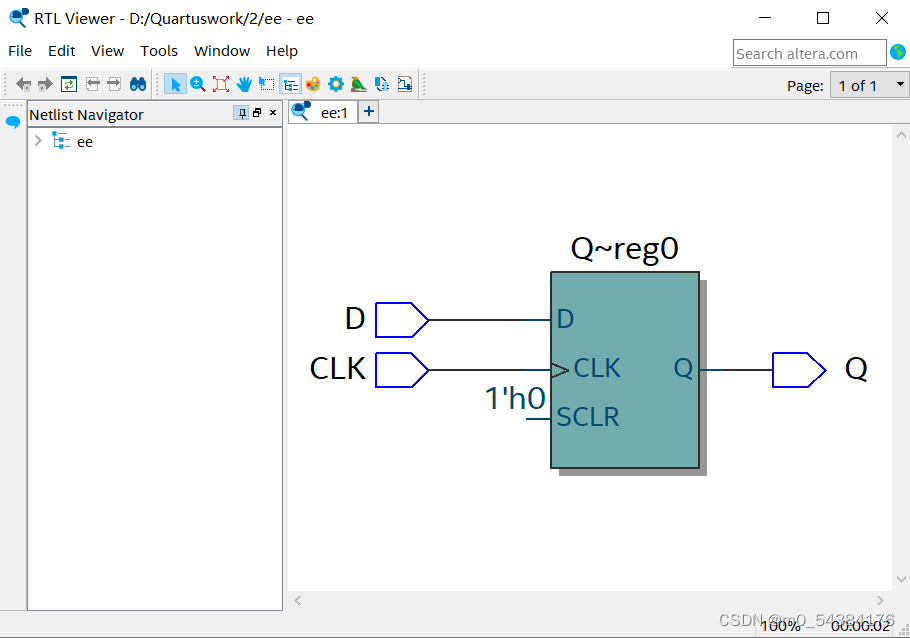

保存并编译,然后查看原理图:

4.仿真波形图

具体步骤与三、4.仿真波形图相同。

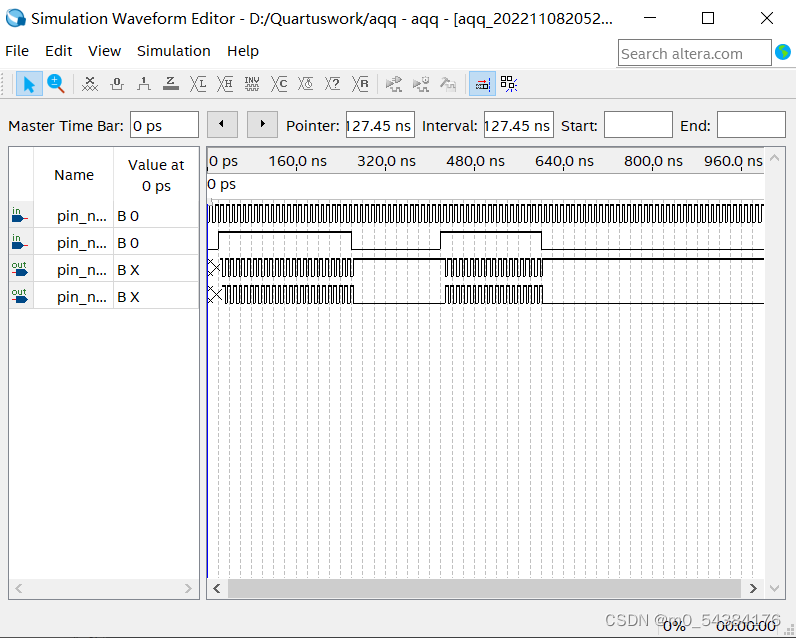

结果如下:

功能仿真波形图(延时半个时钟周期):

时序仿真波形图(延时一个时钟周期):

五、用Verilog语言实现D触发器及时序仿真

1.创建工程

与三、1.创建工程相同

2.新建Verilog HDL 文件

【File】→【New】→【Verilog HDL File】

编写代码:

//dwave是文件名

module dwave(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)//我们用正的时钟沿做它的敏感信号

begin

Q <= D;//上升沿有效的时候,把d捕获到q

end

endmodule

3.编译

保存文件并编译.

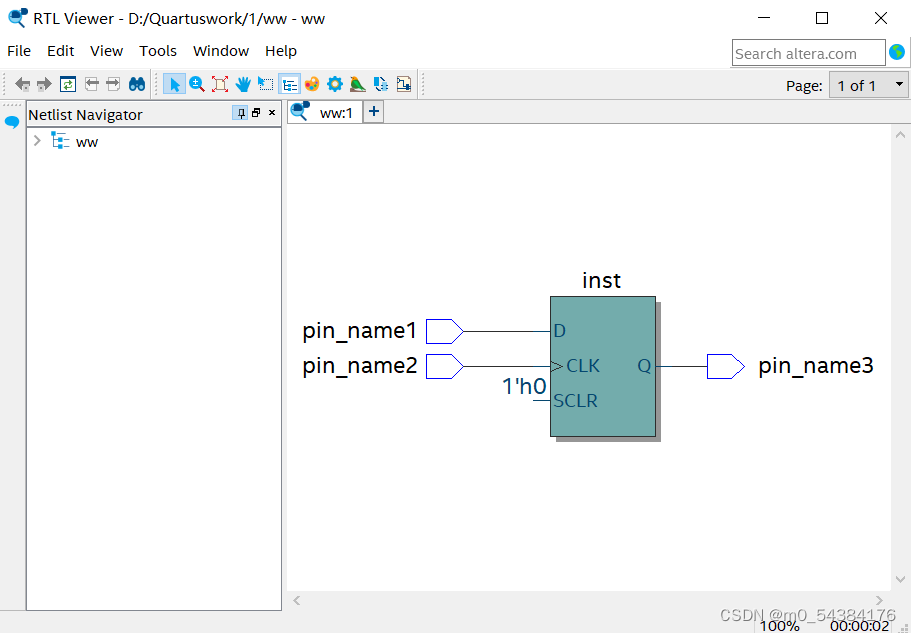

使用rtl viewer查看硬件电路图

硬件电路图

4.仿真波形图

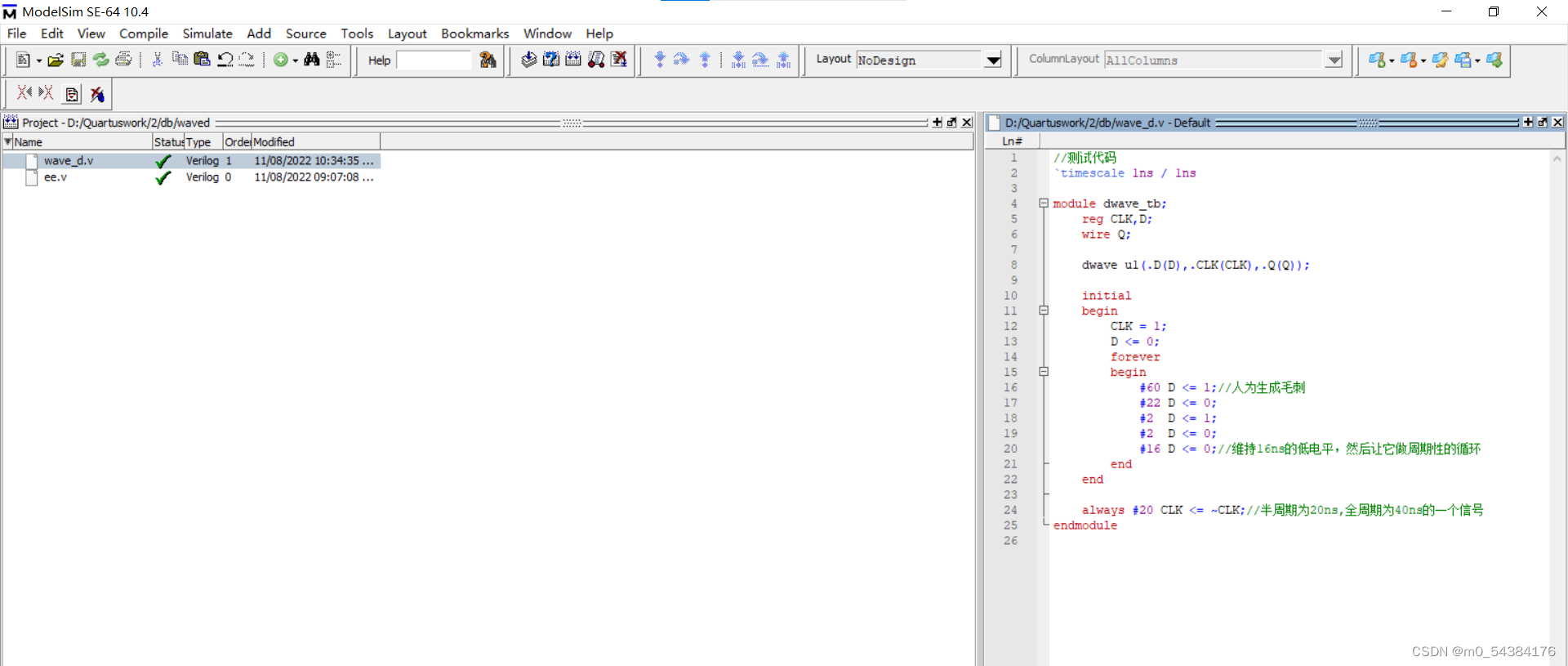

可以跟前面一样仿真,这里使用modelsim SE进行手动仿真

打开 Modelsim 软件。

具体步骤如下:

在Quartus创建的工程文件夹下新建一个 tb 文件夹;

点击【File】→【Change Directory】选择 tb 文件夹;

添加现有文件:Add Existing File

找到刚刚 Quatrus 编译生成的 .v 文件,再点击【OK】

再创建一个新的文件

然后关闭添加文件窗口界面

再双击刚刚新建的 wave_d.v 文件,添加如下代码:

//测试代码

`timescale 1ns / 1ns

module dwave_tb;

reg CLK,D;

wire Q;

dwave u1(.D(D),.CLK(CLK),.Q(Q));

initial

begin

CLK = 1;

D <= 0;

forever

begin

#60 D <= 1;//人为生成毛刺

#22 D <= 0;

#2 D <= 1;

#2 D <= 0;

#16 D <= 0;//维持16ns的低电平,然后让它做周期性的循环

end

end

always #20 CLK <= ~CLK;//半周期为20ns,全周期为40ns的一个信号

endmodule

然后保存,点击【编译】按钮,编译所有文件

点击【Simulate】→【Start Simulation…】

找到 wave_d.v 文件所在的工程(看路径),取消勾选,点击【OK】

右键点击工程名,再点击【Add Wave】

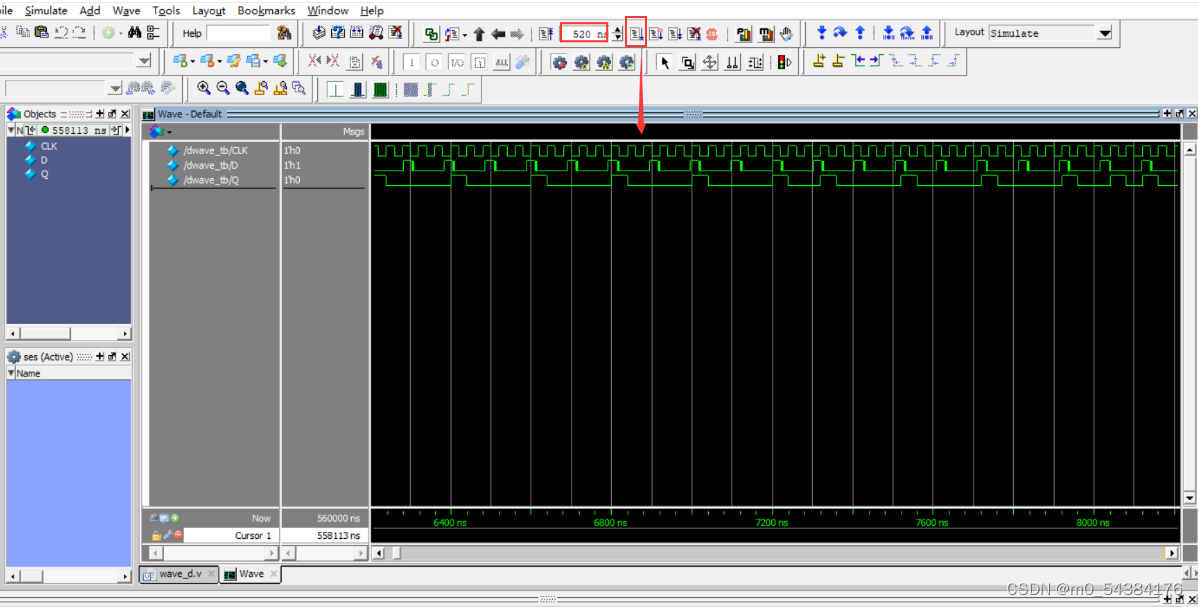

设置运行时长,再点击旁边的运行按钮,即可出现仿真效果图

总结

参考博客:https://blog.csdn.net/weixin_46129506/article/details/123443865

通过三种方式的使用,对D触发器内部结构更加了解,而Verilog语言在遇到比较复杂的电路图时会更容易。通过三种方式实现D触发器及时序仿真的过程,可以发现D触发器的基本功能是在复位信号为1的时候,CLK的上升沿会引起Q值的变化。

1599

1599

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?