基于小梅哥b站FPGA视频

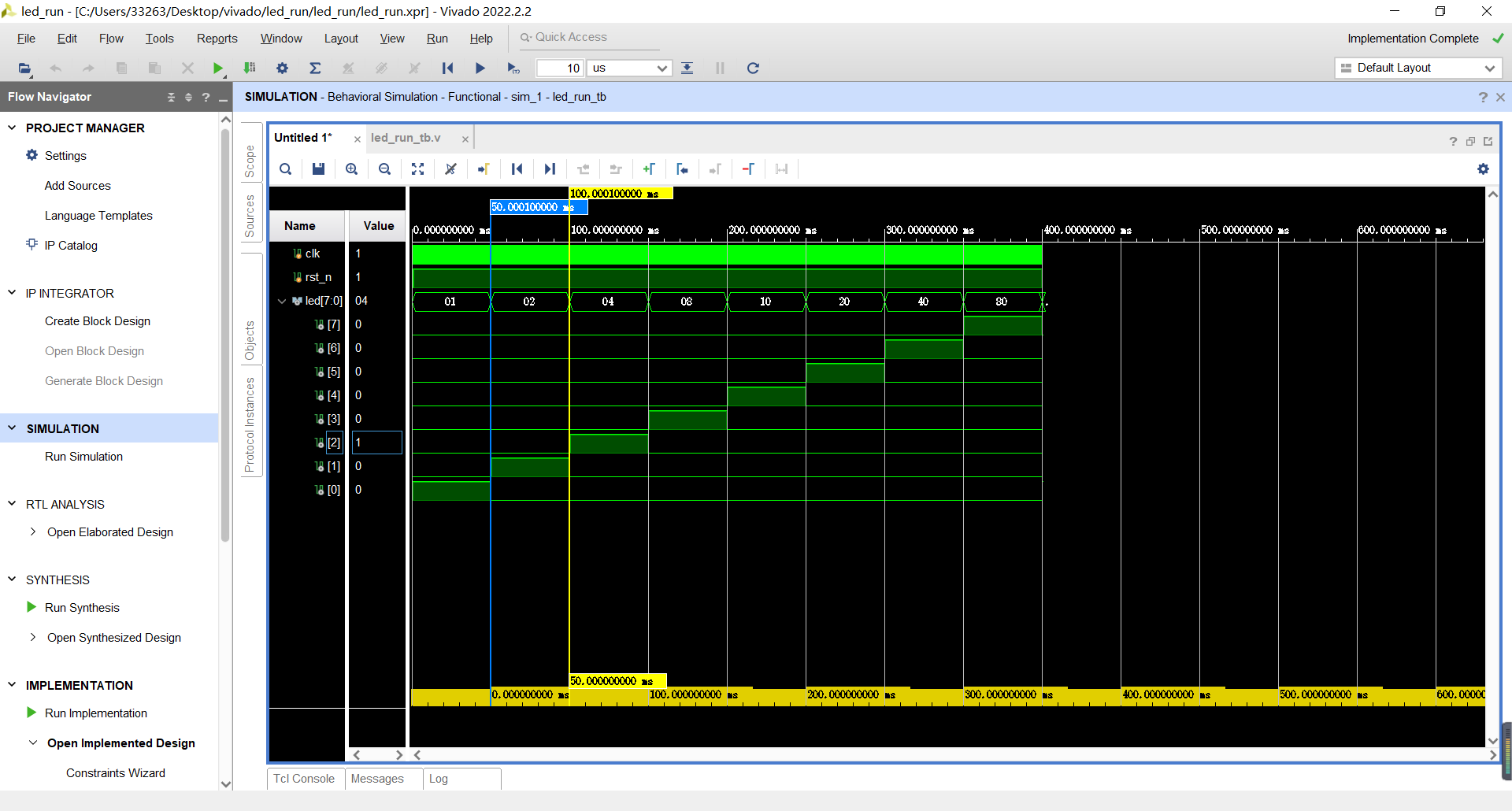

要求: 八个Led灯每隔0.05s循环闪烁

verilog设计:

module led_run(

input clk,//时钟100MHZ 1/100000000=10ns

input rst_n,

output reg[7:0]led // 每灯间隔50ms闪烁 50000000ns

);

reg [26:0]cnt;//计数到5000000 50000000/10=5000000

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 1'b0;

else if (cnt ==27'd4999999)

cnt <= 1'b0;

else

cnt <= cnt + 1'b1;

always @(posedge clk or negedge rst_n)

if(!rst_n)

led <= 8'b00000001;

else if(cnt == 27'd4999999)

begin

if(led == 8'b10000000)

led <= 8'b00000001;

else

led <= led << 1 ;

end

else

led <= led;

endmodule

测试文件:

`timescale 1ns/1ns

module led_run_tb();

reg clk;

reg rst_n;

wire [7:0]led;

led_run led_run(

.clk(clk),

.rst_n(rst_n),

.led(led)

);

initial clk = 1;

always #5 clk= ~clk;//时钟周期10ns 时钟5ns翻转一次

initial begin

rst_n = 0;

#101 rst_n = 1;

#400000000;//八个led灯 进行循环一次 400ms

$stop;

end

endmodule

该文描述了一个使用Verilog编程的FPGA设计,目标是使八个LED灯以0.05秒的周期循环闪烁。设计中包含一个计数器,当达到特定值时重置,并通过左移操作来改变LED的状态。在测试文件中,模拟了10ns时钟周期,并在400ms后停止程序。

该文描述了一个使用Verilog编程的FPGA设计,目标是使八个LED灯以0.05秒的周期循环闪烁。设计中包含一个计数器,当达到特定值时重置,并通过左移操作来改变LED的状态。在测试文件中,模拟了10ns时钟周期,并在400ms后停止程序。

2949

2949

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?