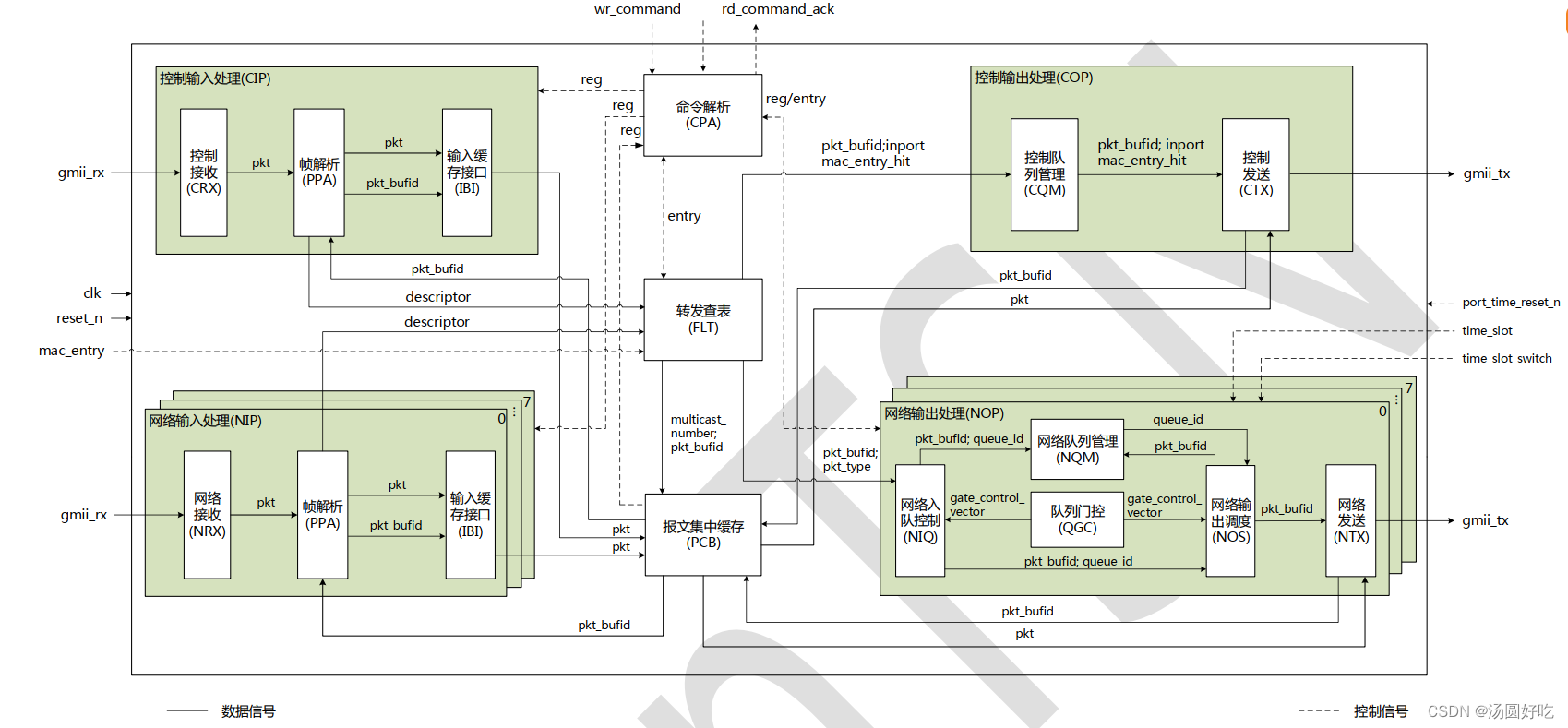

一.TSS(Timing Sensitive Switch,时间敏感交换)模块总体介绍

整个架构划分为五大部分逻辑:网络输入处理逻辑、网络输出处理逻辑、 控制输入处理、控制输出处理以及内部处理逻辑。

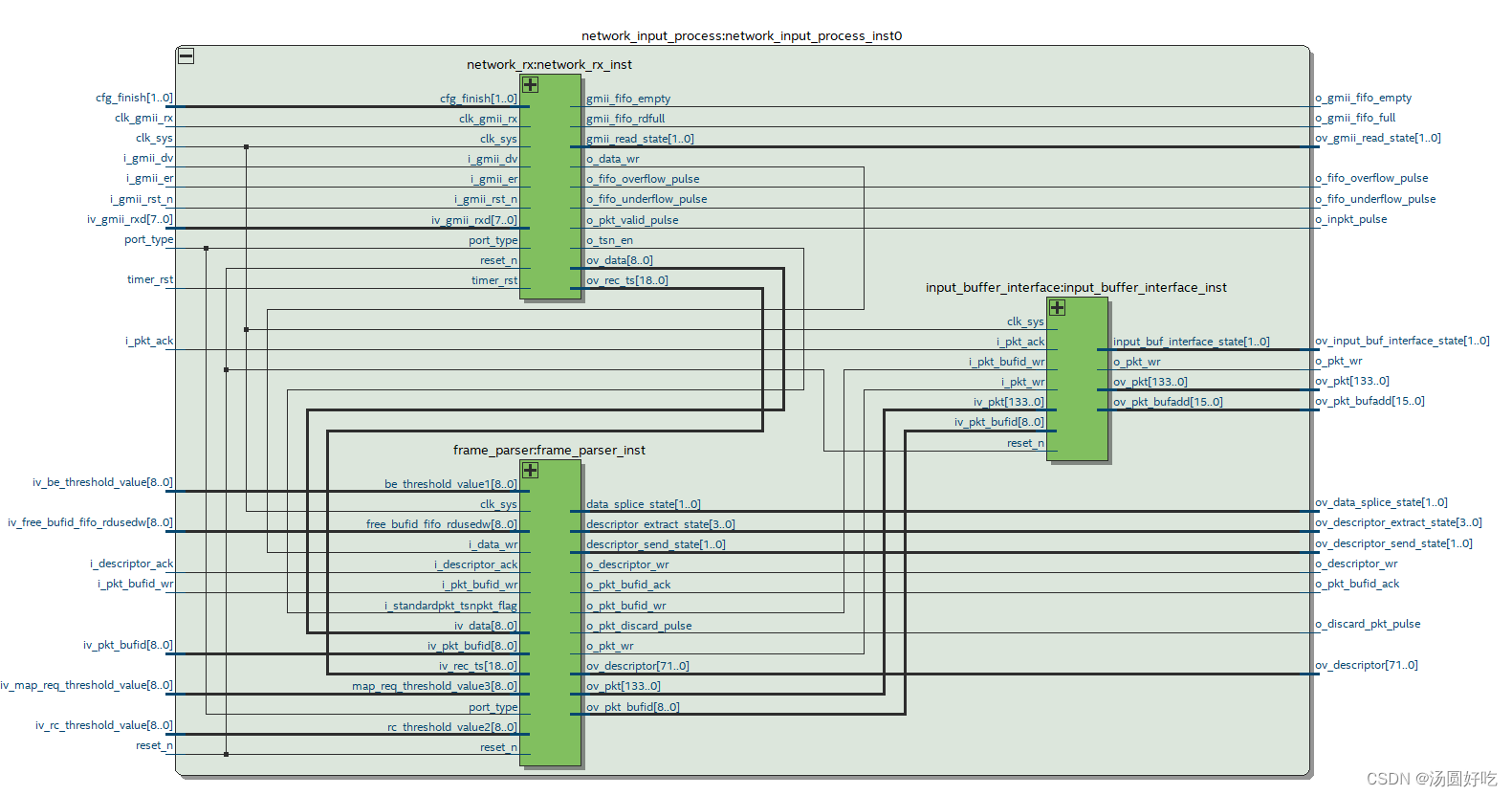

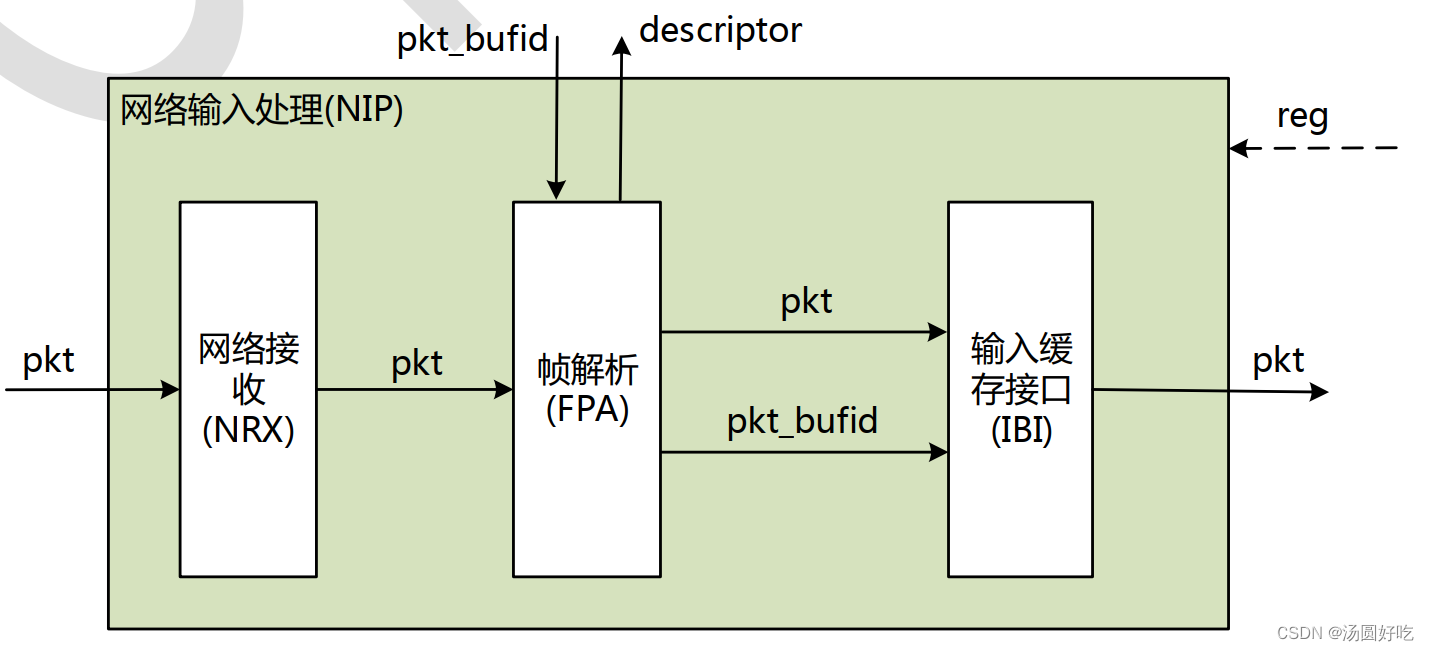

二.网络输入处理逻辑详解

网络输入处理逻辑主要包括:NRX(网络接收)模块,FPA(帧解析)模块,IBI(输入缓存接口)模块这三部分。 内部组成框图和代码RTL视图如下

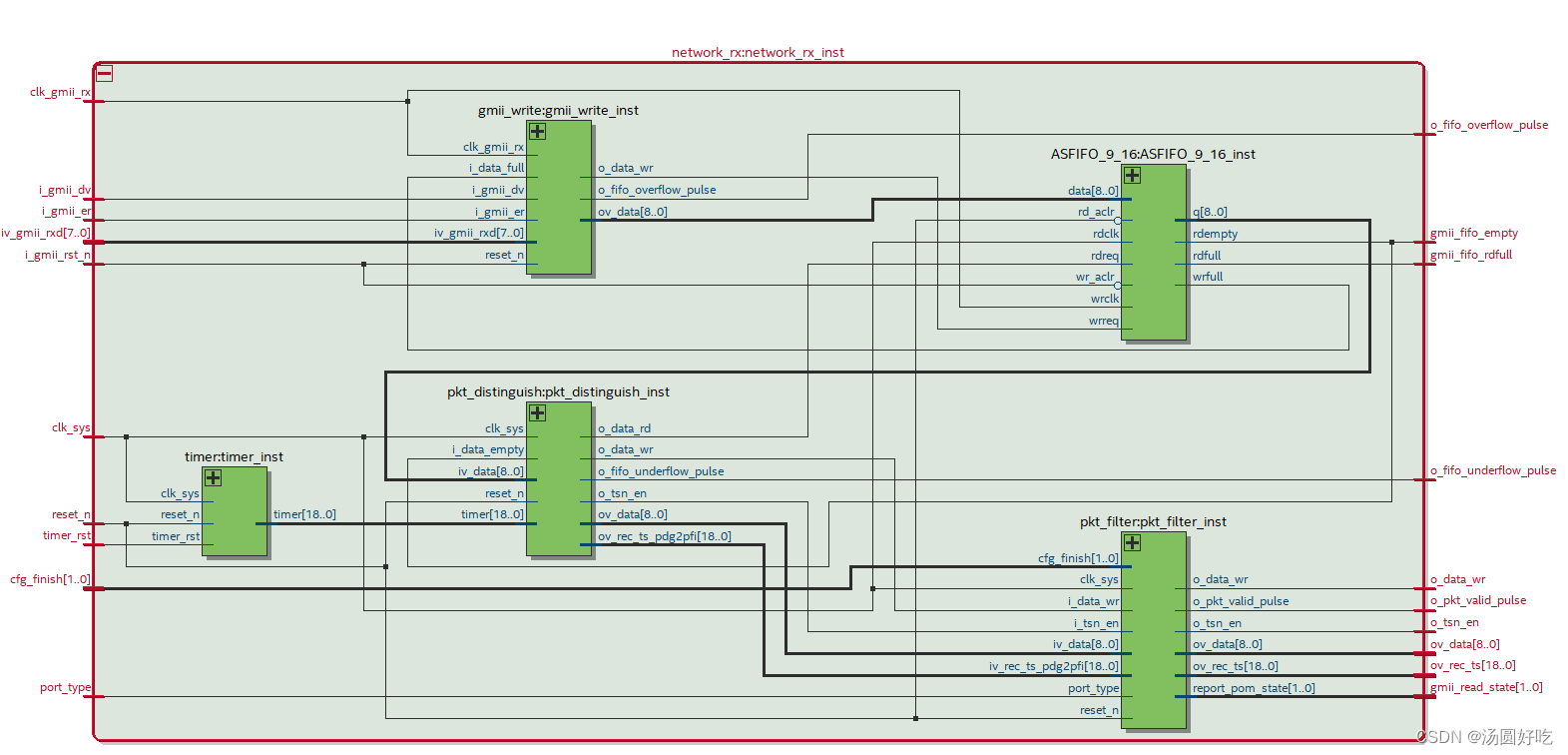

1.网络输入处理之NRX(Network RX,网络接收)模块详解

NRX(Network RX,网络接收)模块主要包括:

1.time counter:一个简单的时间19位计数器,用来切换时钟域。

2.pkt_filter:根据GMII输入数据包的类型和配置信息来过滤和处理数据包,然后输出符合要求的数据包,并在传输完成时产生有效脉冲信号。

3.pkt_distinguish:识别数据包是不是TSN报文(时钟敏感网络报文)。

4.gmii_write:根据 GMII 接收的数据和 FIFO 状态,模块可以将数据正确写入 FIFO,同时处理可能出现的FIFO上溢错误。

5.9x16 RAM五个部分。

主要功能:是接收网络接口传来的报文,将报文传输时钟域从 GMII 接口接收时钟域切换到 TSS内部时钟域;记录本模块接收时间同步报文的时间,并将其存放在TSNTag 中;识别标准以太网报文和 TSN 报文并根据 TSS 所处的阶段来决定是否传输报文:若TSS处于初始化阶段,丢弃所有报文;若 TSS 处于配置阶段,传输标准以太网报文和 TSN 报文中的配置报文;若 TSS 处于时钟同步阶段,传输标准以太网报文和 TSN 报文中的非时间敏感报文;若 TSS 处于正常工作阶段,传输标准以太网报文和 TSN 报文。

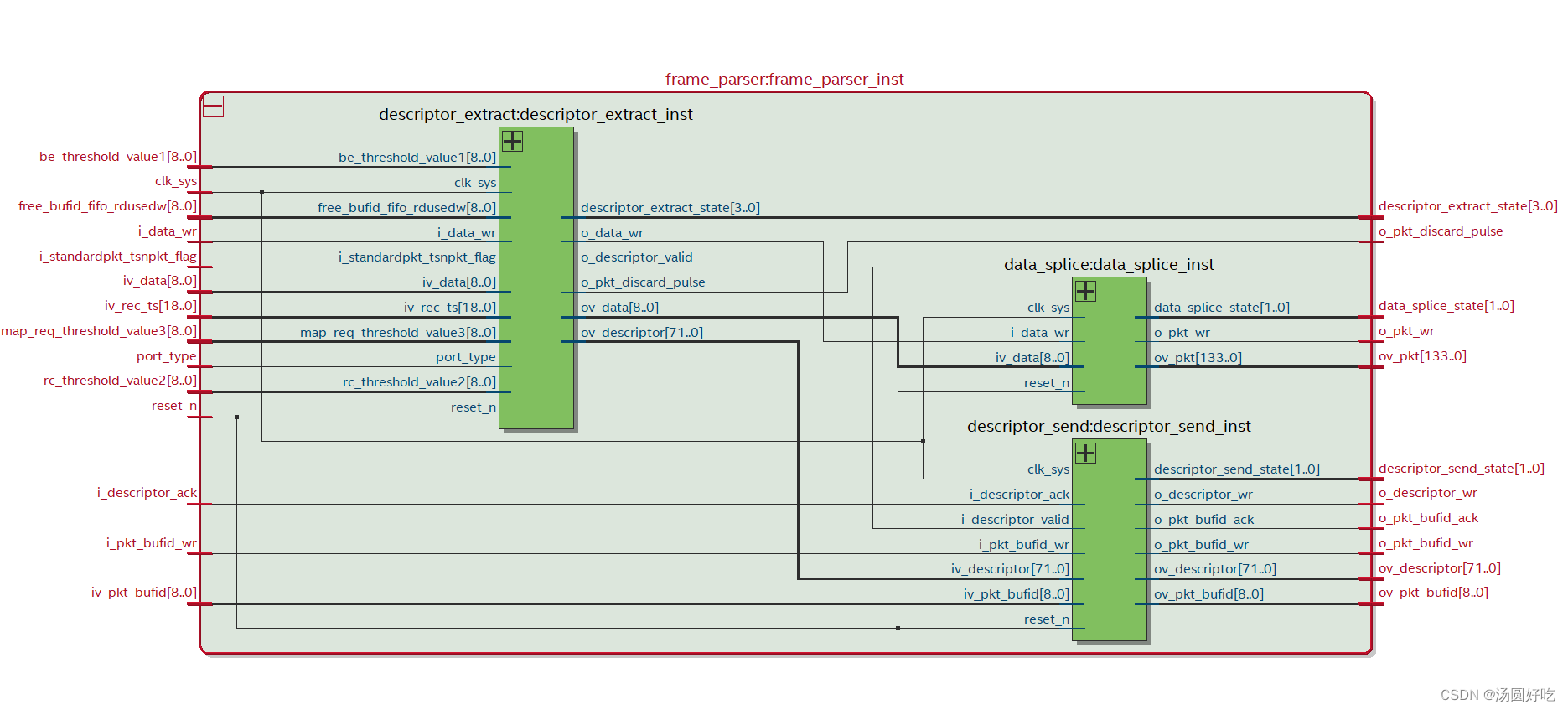

2.网络输入处理之FPA(Frame Parse,帧解析)模块详解

FPA(Frame Parse,帧解析)模块主要工作流程:

data splice模块:

1. 模块处于空闲状态(`idle_s`),等待接收新的数据包。

2. 当接收到数据且为数据包头(`iv_data[8] == 1'b1`),则开始拼接数据包。

3. 在传输状态(`tran_s`),模块逐步拼接数据包的数据部分。

4. 当接收到数据且为数据包尾(`iv_data[8] == 1'b1`),完成数据拼接,输出完整的数据包。

5. 拼接完成后,返回到空闲状态。

在拼接数据包时,数据模块使用 `byte_cnt` 来计数拼接的字节数,通过 `ov_pkt` 输出完整的数据包。当拼接完成时,`o_pkt_wr` 信号为高电平,表示数据包可写入。拼接模块在拼接头部、传输数据、拼接尾部时,根据 `byte_cnt` 和数据包的标志位(`pkt_head_flag`)来逐步完成拼接操作。

descriptor_send模块:

1. 模块处于空闲状态(`idle_s`),等待接收新的描述符和数据包缓冲区ID。

2. 当接收到描述符和数据包缓冲区ID时,模块将它们存储在内部寄存器 `ov_descriptor` 和 `ov_pkt_bufid` 中,并设置相应的写入信号 `o_descriptor_wr` 和 `o_pkt_bufid_wr` 为高电平。

3. 模块进入等待描述符应答状态(`wait_des_ack_s`),此时输出的描述符和数据包缓冲区ID依然有效,等待接收方发出应答信号 `i_descriptor_ack`。

4. 一旦接收到描述符应答信号 `i_descriptor_ack` 为高电平,表示接收方已经接收到描述符,模块将 `ov_descriptor` 和 `ov_pkt_bufid` 清零,并将相应的写入信号设置为低电平。

5. 模块返回到空闲状态,等待下一组描述符和数据包缓冲区ID。

整个过程中,描述符和数据包缓冲区ID的传递是同步的,接收方必须在适当的时间应答,以确保数据的正确传输。

descriptor_extract模块:

1. 模块处于空闲状态(`IDLE_S`),等待接收新的数据包并提取描述符信息。

2. 当接收到数据包和写入信号时,模块根据数据包头(`iv_data[8]`)判断数据包类型,并根据不同类型进行相关处理。

3. 模块根据数据包类型进行状态转换,以及相关字段的处理和存储。

4. 对于标准以太网数据包(`i_standardpkt_tsnpkt_flag` 为1),模块会判断缓冲区ID是否低于阈值或已用完,若满足条件则将数据包丢弃,否则进行描述符写入和数据包传输。

5. 对于映射类型的数据包,根据端口类型和相关阈值进行缓冲区ID的判断和处理。

6. 在标准以太网数据包和映射类型数据包的传输过程中,描述符逐步填充,并在第六个周期时完整填充,以及标志位的设置。

7. 数据包的传输完成后,模块返回空闲状态,等待下一组数据包的提取。

整个过程中,模块根据接收到的数据包类型,根据逻辑进行相应的处理和状态转换,最终提取出有效的描述符和数据包,并根据情况进行丢弃或传输。

主要功能:是接收报文集中缓存模块分配的 pkt_bufid,将报文每拍数据位宽由 9bit 转换为 134bit,并将位宽转换后的报文和 pkt_bufid 输出给输入缓存接口模块;根据接收到的报文构造报文描述符,并将其输出给转发查表模块进行查表;识别报文类型,并对 RC 流量、 BE 流量和标准以太网流量进行监管。

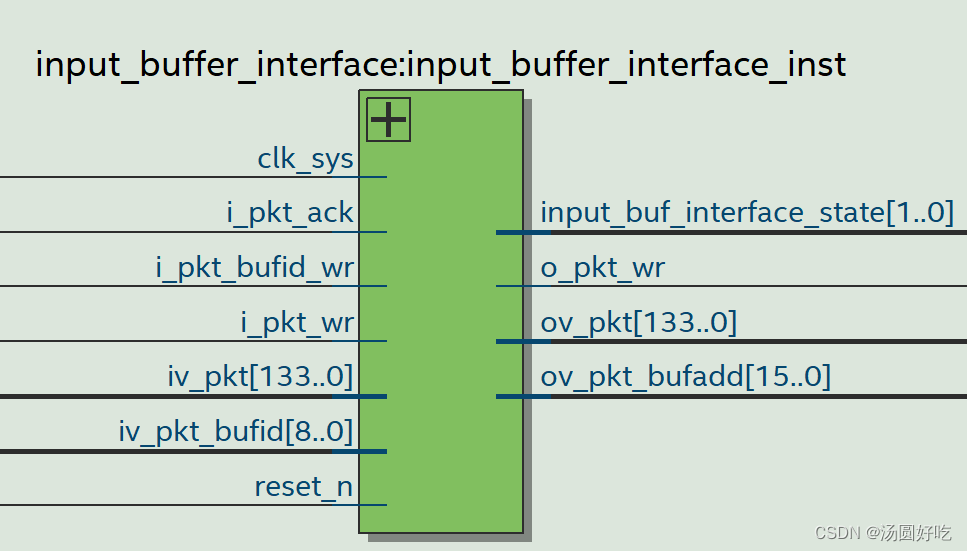

3.网络输入处理之IBI(Input Buffer Interface,输入缓存接口)模块 详解

IBI(Input Buffer Interface,输入缓存接口)模块工作流程:

1. 模块处于空闲状态(`idle_s`),等待接收新的数据包和数据包缓冲区ID,并将缓冲区ID存储起来。

2. 当接收到数据包头(`iv_pkt[133:132]`)为2'b01(表示数据包的开始部分),且有有效的缓冲区ID时,模块将数据包和缓冲区ID存储到输出端口,并置写入信号(`o_pkt_wr`)为1,表示数据包写入到后续处理逻辑。在写入数据包过程中,模块进入等待确认状态(`wait_ack_s`)。

3. 在等待确认状态下,模块会等待来自后续处理逻辑的确认信号(`i_pkt_ack`)。如果收到确认信号,表示数据包已成功传输到后续处理逻辑,模块将清空输出的数据包(`ov_pkt`)、写入信号(`o_pkt_wr`)和缓冲区地址(`ov_pkt_bufadd`),并根据情况转换回空闲状态或传输数据包状态(`tran_pkt_s`)。

4. 在传输数据包状态下,如果收到新的数据包写入信号(`i_pkt_wr`),模块将存储新的数据包,并将缓冲区地址(`ov_pkt_bufadd`)递增,表示传输到下一个缓冲区。在数据包传输过程中,模块会根据数据包头的信息判断数据包是否结束,并根据情况转换回空闲状态或继续传输数据包。

整个过程中,模块根据接收到的数据包头信息,根据逻辑进行相应的处理和状态转换,最终将数据包存储到缓冲区,并根据传输过程的情况更新状态,以实现数据包的接收和传

主要功能:将报文数据发送给报文集中缓存模块进行缓存。本模块接收帧解析模块传来的 134bit 数据,并使用两个寄存器进行缓存,其中任何一个寄存器有数据则往报文集中缓存模块发出写请求,在接收到报文集中缓存模块传来的响应后,才完成一拍数据的写入;并将帧解析模块传来的数据写入另一个寄存器中。

代码来自开源Open TSN3.2

1931

1931

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?