一、设计背景

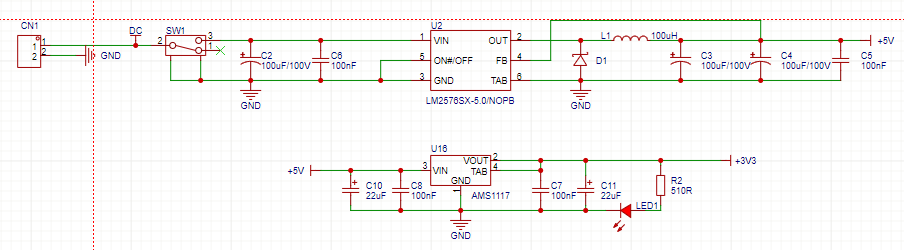

设计一个基于GD32F303C8T6微控制器的平衡车硬件评估板,设备锂电池供电,通过DC-DC芯片LM2576将直流输入转换为5V电压,经过LDO AMS1117转换3.3V。板载陀螺仪、电机驱动IC(TB6612)、蓝牙、红外、编码器等外围设备。

二、设计要求

2.1 原理图设计

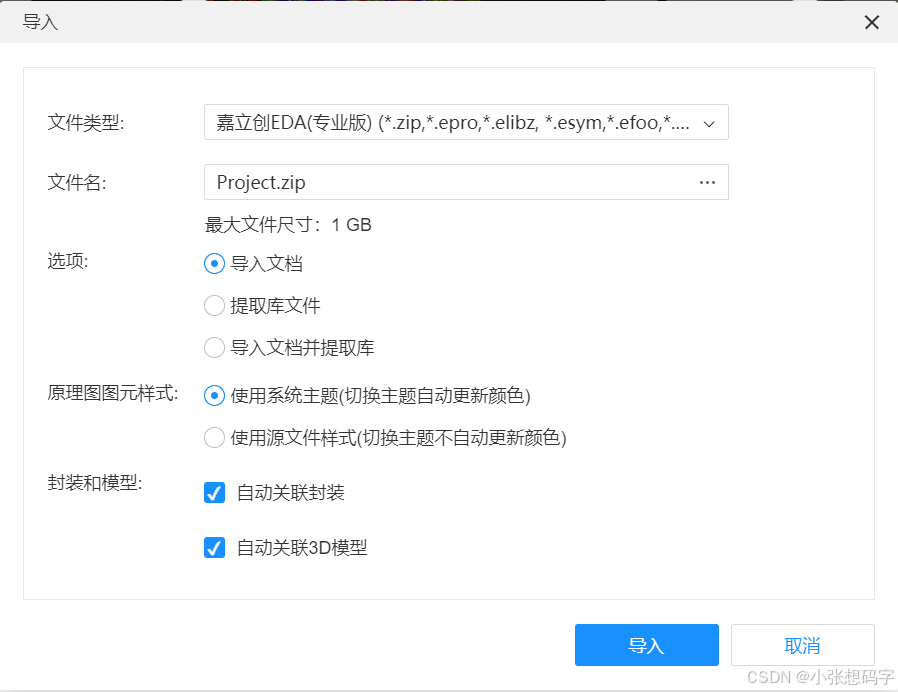

通过嘉立创EDA(专业版)导入试题附件中提供的工程文件(Project.zip)。

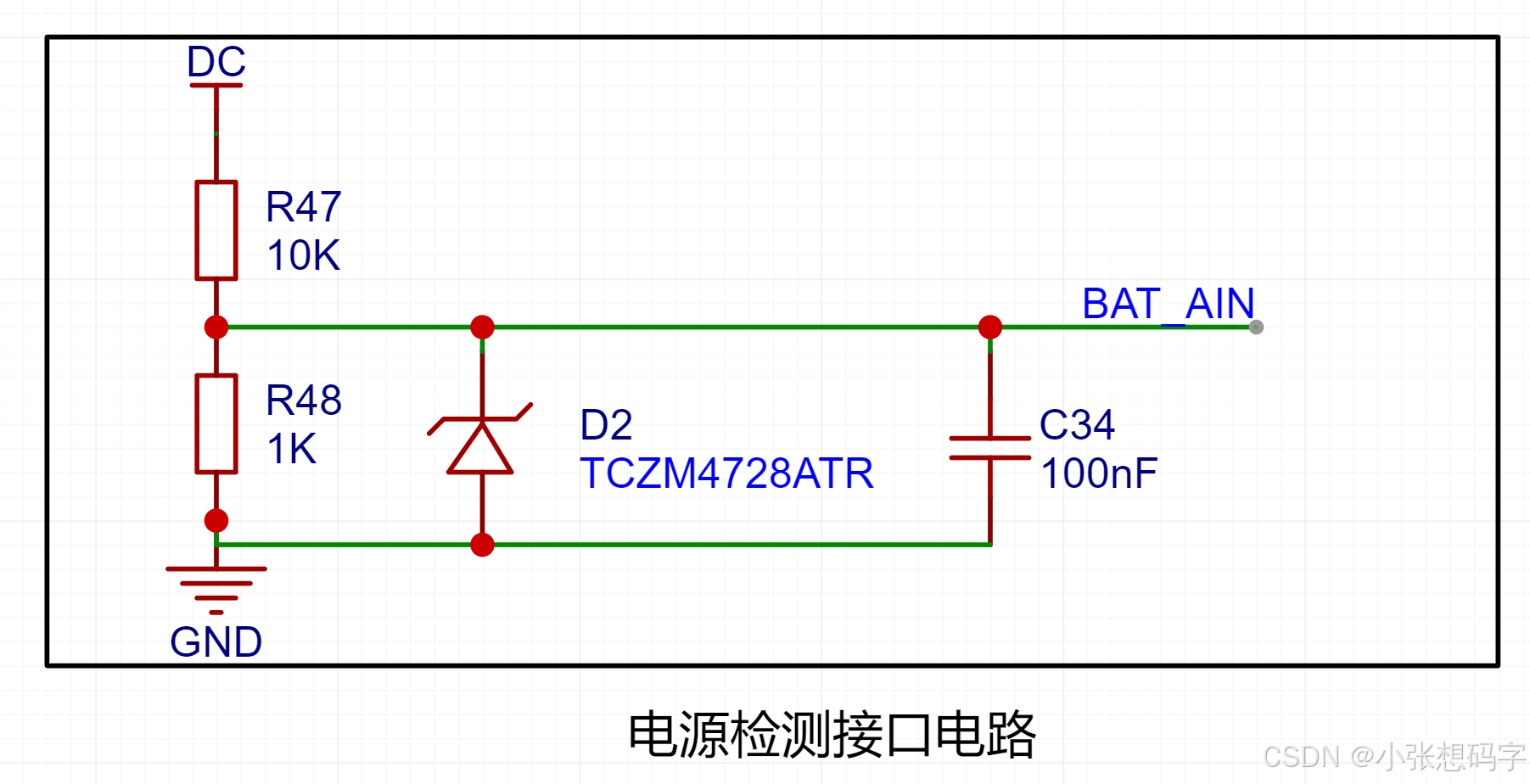

打开原理图,通过给定的元器件,在给定矩形区域内,使用给定的元器件(电阻、电容、稳压二极管(3.3V)等)完成输入电源电压的检测功能。

备注:原理图中元器件位号、名称、网络标识符名称及给定的网络连接关系不可以修改。

完成结果:

该电路是一个简单的电源检测接口电路,主要用于检测电源电压是否在正常范围内,并将检测结果传递给后续电路进行处理。通过读取BAT_AIN的电压值,判断电源电压是否正常。

R47和R48构成一个分压电路,用于将输入的直流电压(DC)降低到一个适合后续电路处理的电压范围。

因为输入的直流电较高,直接接入后续电路中会损伤敏感元件,分压后将高电压按照比例降低到安全范围。

电容C34用于滤波,提高稳定电压信号。

二极管D2主要用于防止电源反接时损坏电路。

-

如果电源正负极接反,二极管D2会截止,阻止反向电流流过后续电路,从而保护电路不受损坏。

-

当电源正接时,二极管导通,允许电流正常流过分压电路。

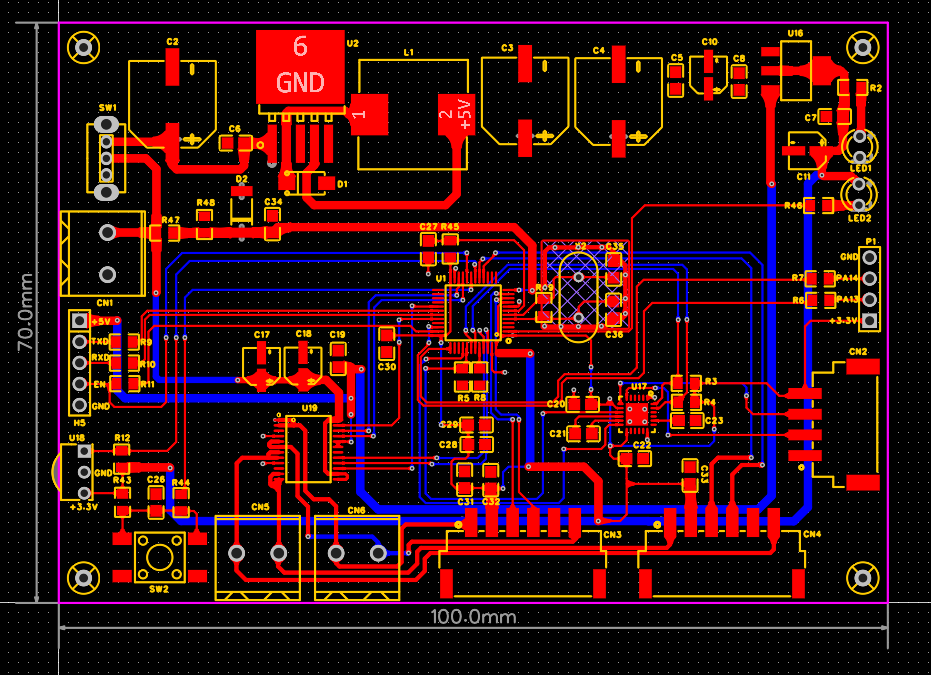

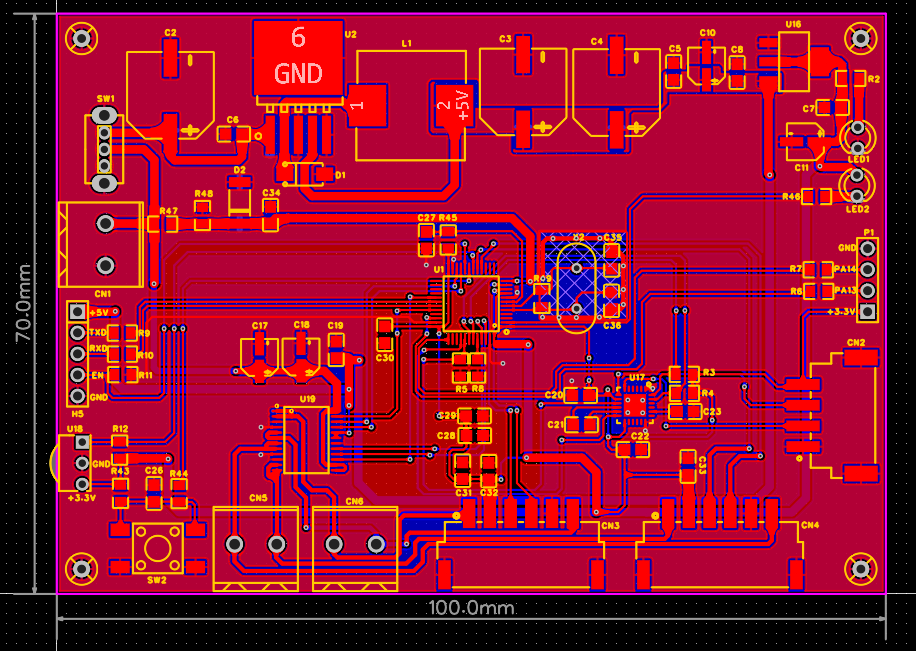

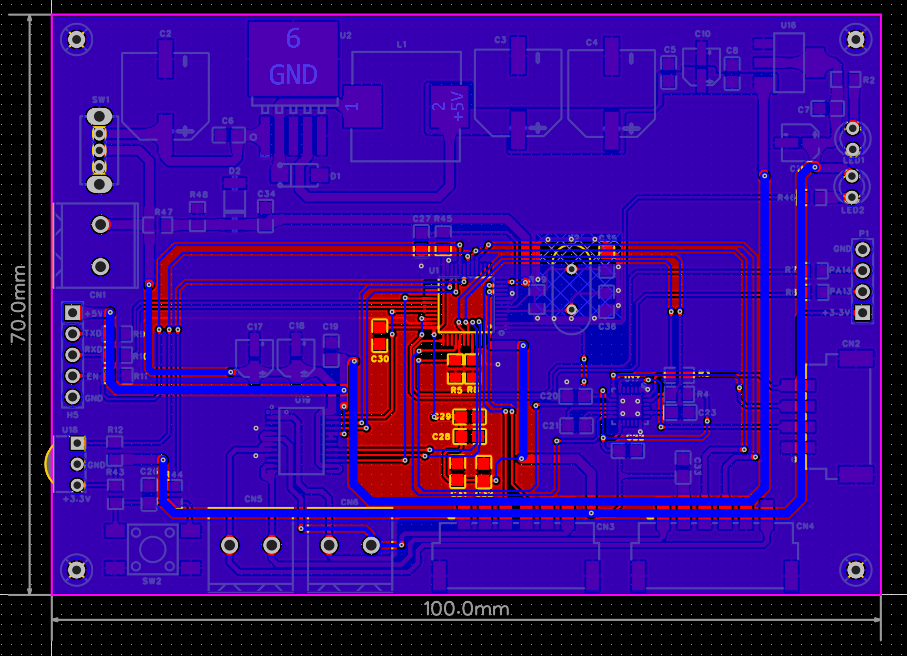

2.2 印制线路板设计

1、导入封装库

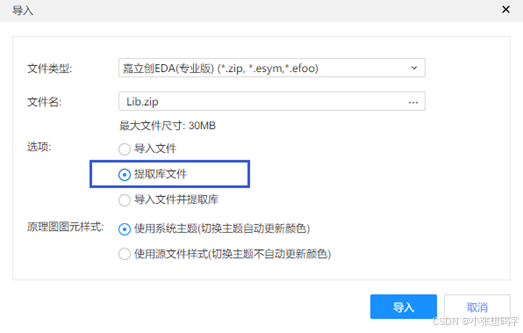

通过嘉立创EDA(专业版)导入Lib.zip,并提取库文件。

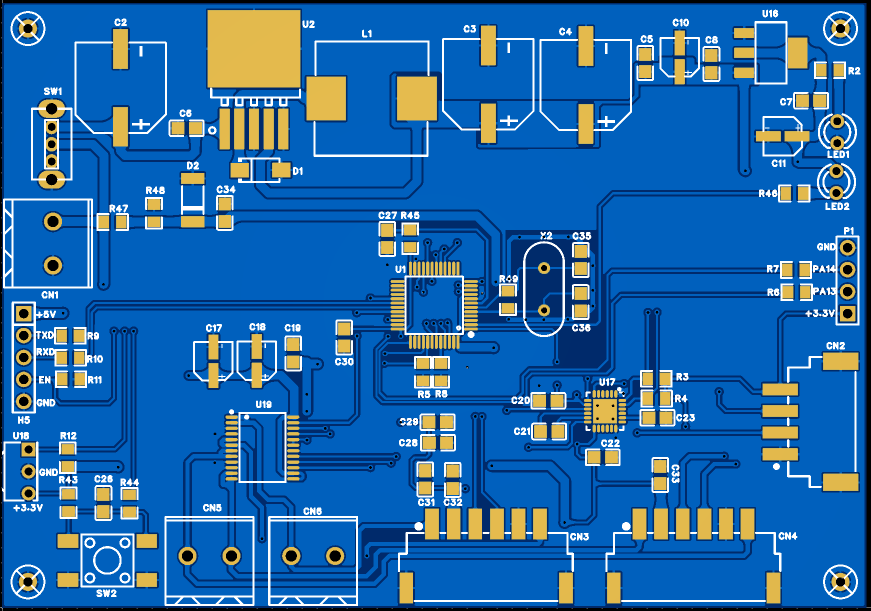

2、元器件封装表

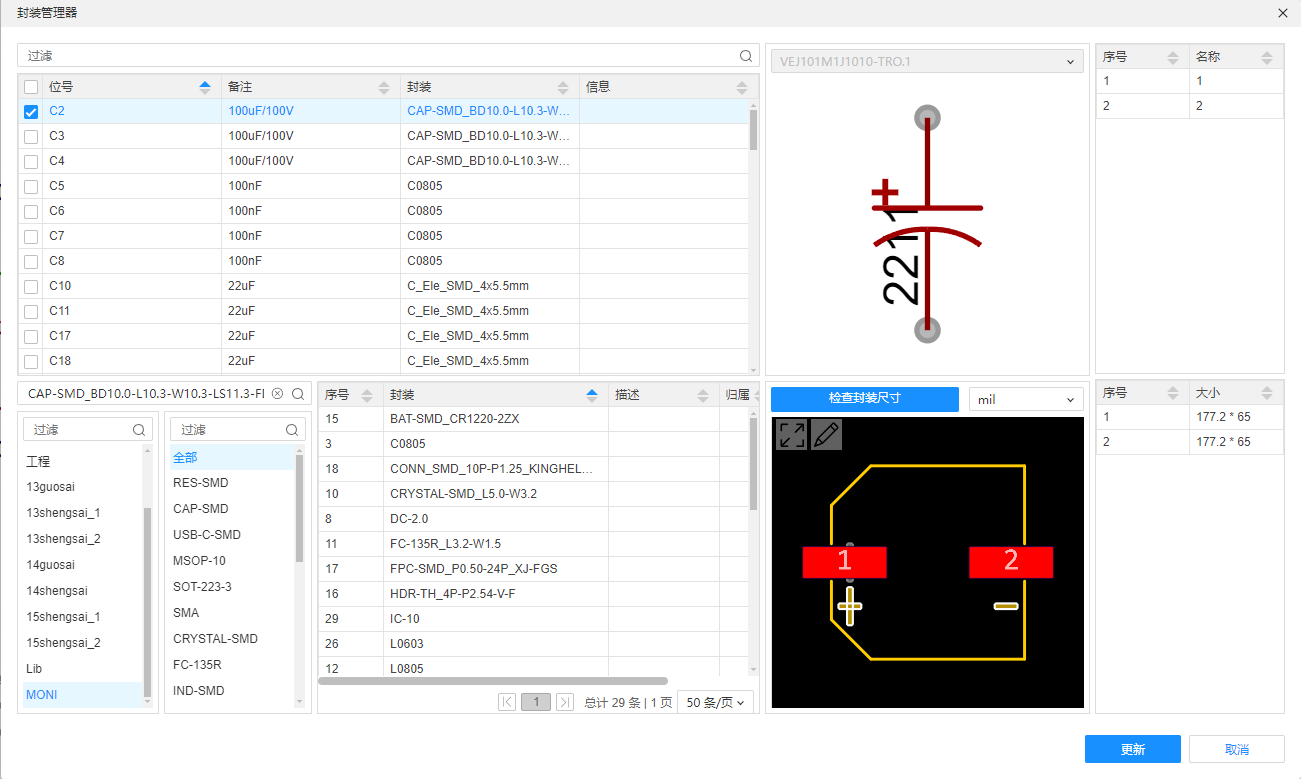

| 序号 | 位号 | 封装 |

| 1 | C2,C3,C4 | CAP-SMD_BD10.0-L10.3-W10.3-LS11.3-FD |

| 2 | C5,C6,C7,C8,C19,C20,C21,C22,C26,C27,C28,C29,C30,C31,C32,C33,C34 | C0805 |

| 3 | C10,C11,C17,C18 | C_Ele_SMD_4x5.5mm |

| 4 | C23 | C0805 |

| 5 | C35,C36 | C0805 |

| 6 | CN1,CN5,CN6 | CONN-TH_2P-P5.08-WJ500V-5.08-2P |

| 7 | CN2 | CONN-SMD_4P-P2.50-WT |

| 8 | CN3,CN4 | CONN-SMD_6P-P2.50_XUNPU_WAFER-XH2.54-6PWB |

| 9 | D1 | SMA_L4.3-W2.6-LS5.0-RD |

| 10 | D2 | LL-41_L5.0-W2.5-R-RD |

| 11 | H5 | HDR-TH_5P-P2.54-V-M |

| 12 | L1 | IND-SMD_L13.0-W12.8 |

| 13 | LED1,LED2 | LED_TH-3mm |

| 14 | P1 | HDR-TH_4P-P2.54-V-M-1 |

| 15 | R2,R46 | R0805 |

| 16 | R3,R4,R5,R12,R43 | R0805 |

| 17 | R6,R7,R44 | R0805 |

| 18 | R8,R11,R45,R47 | R0805 |

| 19 | R9,R10 | R0805 |

| 20 | R48 | R0805 |

| 21 | R49 | R0805 |

| 22 | SW1 | 拨动开关 |

| 23 | SW2 | SW-SMD_4P-L6.0-W6.0-P4.50-LS9.0-2 |

| 24 | TP1,TP2,TP3,TP4 | M2螺丝 |

| 25 | U1 | LQFP-48_L7.0-W7.0-P0.50-LS9.0-BL |

| 26 | U2 | PG-TO-263-5_L10.2-W8.7-P1.70-LS14.4-BR |

| 27 | U16 | SOT_223 |

| 28 | U17 | QFN-24_L4.0-W4.0-P0.50-BL-EP2.7 |

| 29 | U18 | OPTO-TH_VS1838B |

| 30 | U19 | SSOP-24_L8.3-W5.6-P0.65-LS7.6-BL |

| 31 | X2 | XTAL-HC-49S |

工具→封装管理器→选择对应的元件库进行器件封装更新

快捷键:Alt+F

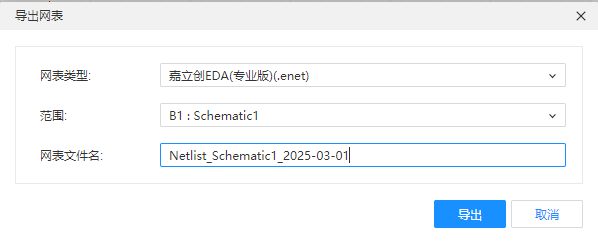

注:如果想要导出原理图的网表文件(.enet),需要先导入封装库,完成器件封装后才可以完成,按照题目要求进行命名保存在文件夹中。

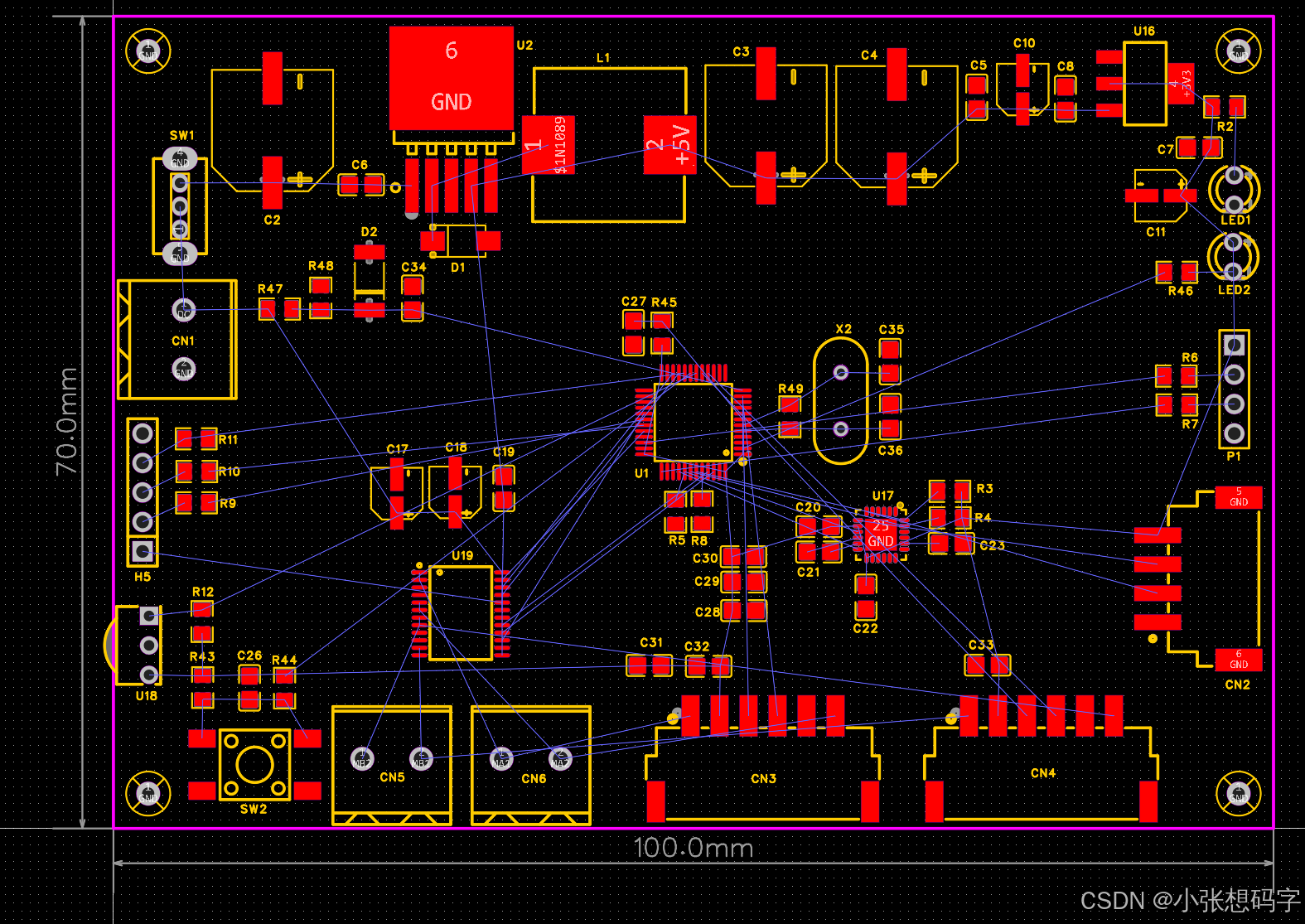

3、 元器件布局

在给定的边框层区域内,完成PCB的布局设计,不可以修改边框尺寸、形状、画布原点。

- 电机接口(CN5):坐标位置(X=24mm, Y=6mm),旋转角度0°。

- 电机接口(CN6):坐标位置(X=36mm, Y=6mm),旋转角度0°。

- 编码器接口(CN3):坐标位置(X=56mm, Y=6mm),旋转角度0°。

- 编码器接口(CN4):坐标位置(X=80mm, Y=6mm),旋转角度0°。

- 安装孔TP1-TP4坐标位置:

TP1: 坐标位置(X=97mm, Y=3mm)

TP2: 坐标位置(X=3mm, Y=3mm)

TP3: 坐标位置(X=3mm, Y=67mm)

TP4: 坐标位置(X=97mm, Y=67mm)

通用要求:合理安排布局,元器件之间应相互平行或者垂直排列,以求整齐、美观,不允许元件重叠;元件排列要紧凑,元件在整个版面上应分布均匀、疏密一致。所有元器件均放置在顶层。

布局方法:

对于电源电路,需要按照原理图顺序进行合理位置摆放,电源布局可以按照边缘单独成一排或成一列。

对于MCU芯片,按照原理图将电阻和电容放在四周,针对于电源电容(3V3-GND)排布在MCU周围,方便布线。

对于分布式芯片,当不涉及外围接口,包括按键,LED,插口,开关以及排针时,涉及的电阻电容均位于其芯片周围,方便过线。

4、 布线设计

在给定的边框层区域内,完成PCB的布线设计,不可以修改边框尺寸、形状、画布原点和给定的安装孔位置。

PCB设计要求:

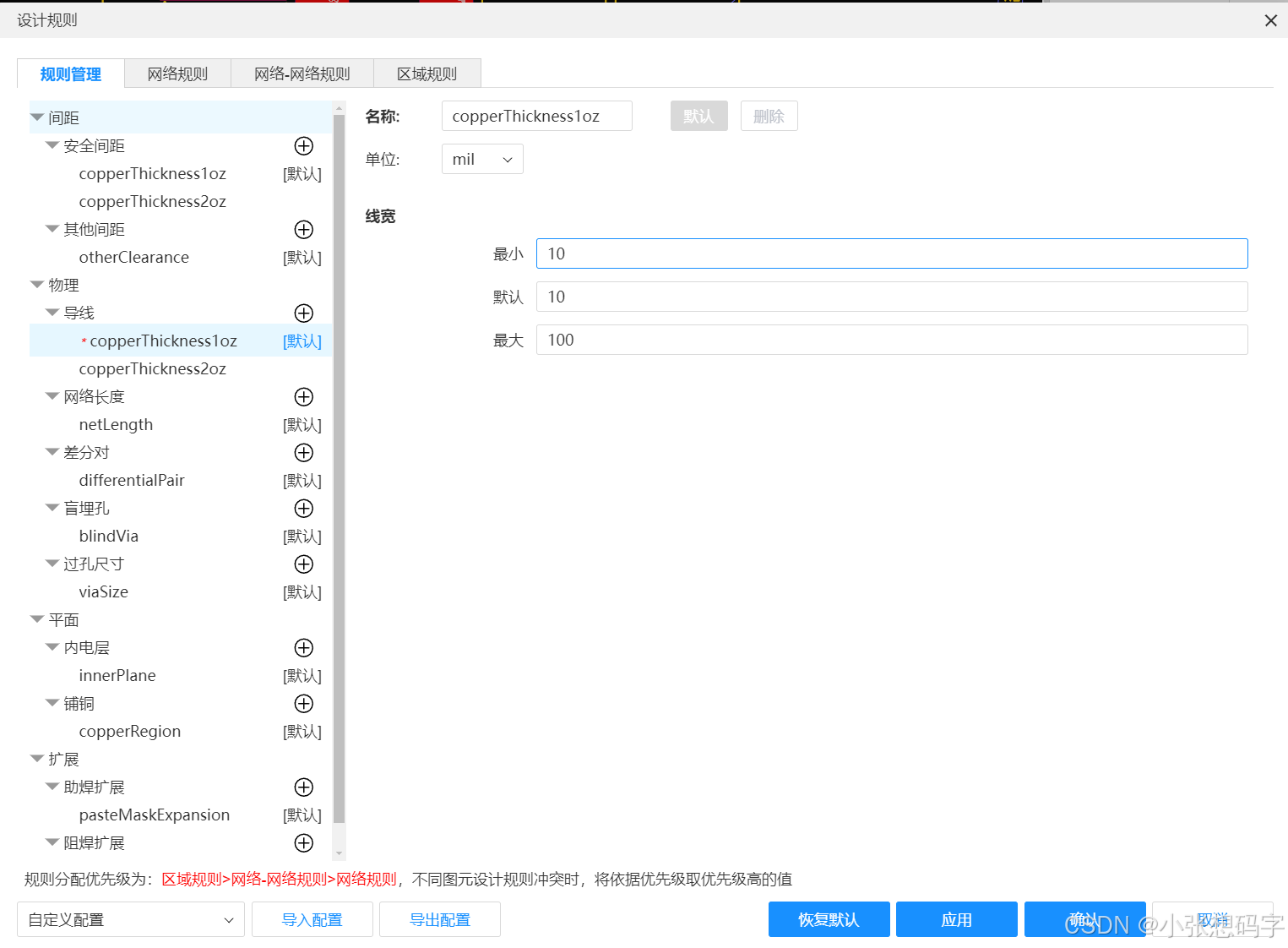

最小线宽: 10mil

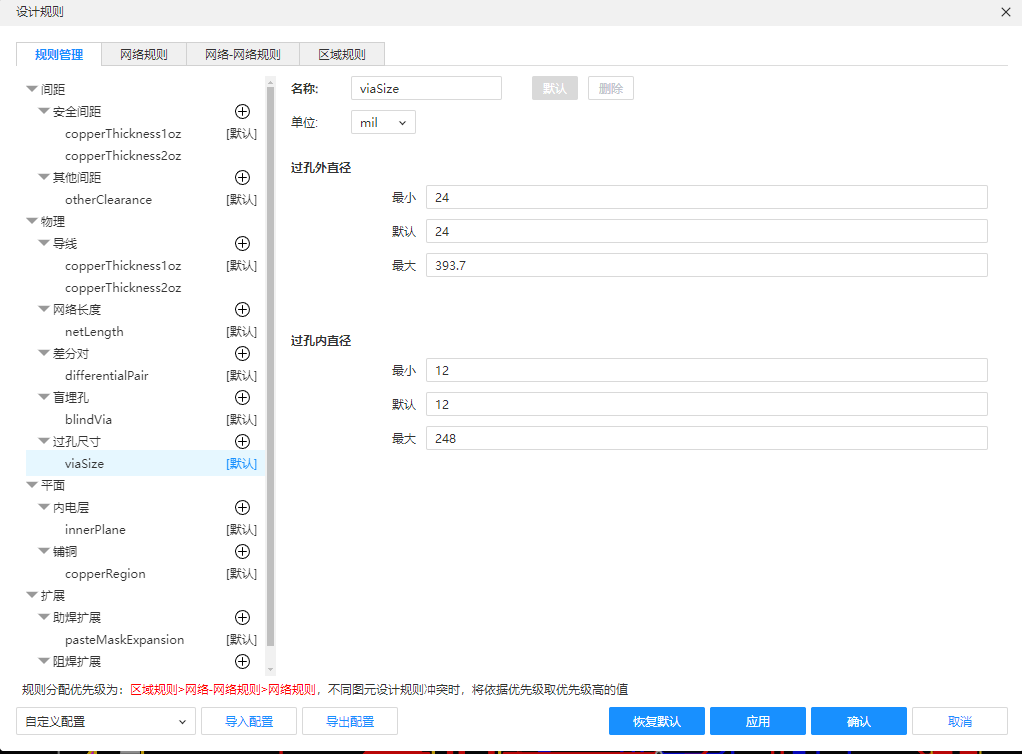

过孔尺寸:过孔外直径最小24mil,过孔内直径最小12mil

丝印字体:字体为默认,线宽6mil,高度45mil

布线层数:2

字符层:顶层丝印层,要求字符摆放整齐。

覆铜层:顶层、底层,GND网络。

网络布通率:100%

DRC检查可通过,无错误信息。

过程:设计→设计规则→间距--安全间距,导线,差分对,过孔尺寸。

布线及后续流程(自用):1、关闭VDD,3V3,+5V,GND等飞线

2、使用默认线宽进行布线,在布线时,应尽量避免直角走线,以减少信号的反射和串扰,提高信号质量。

对于SDA和SCL信号线,通常不需要进行差分对布线,但需要进行等长控制,(为保证I2C总线的通信质量,如果布线长度差异过大,会导致信号传输时间不同步,从而影响数据传输的准确性)布线长度差异的容许范围其长度差异一般应控制在一定范围内,通常建议在100mil以内。

3、开始布置电源飞线,需进行加粗处理(一般使用25mil-40mil),若电源部分处在顶层同一块区域内,并无导线阻隔,就可以铺铜进行连接。

4、GND飞线处理,打过孔

5、晶振进行包地处理,包含电容

6、添加泪滴

7、丝印调整

8、铺铜(矩形)

三、文件提交要求

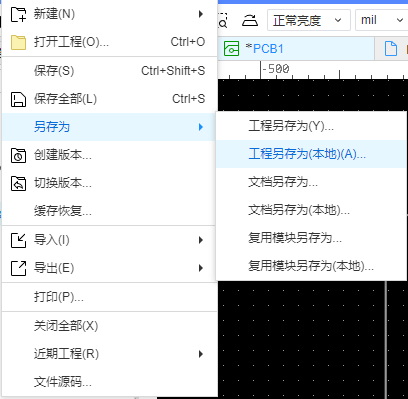

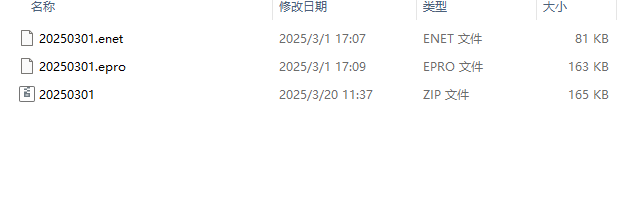

完成设计后,将工程文件另存到本地,文件类型为epro,以准考证号命名。未按照试题要求命名和提交文件的选手将被酌情扣分或记零分。提交不属于试题要求文件的选手将被酌情扣分或记零分。

导出文件主要有网表文件和工程文件:

十四届蓝桥杯EDA模拟赛题已完成。 本文内容全部为学习记录,仅作为学习使用。

参考内容有:

1、https://www.bilibili.com/video/BV1w94y1M7pb/?share_source=copy_web&vd_source=241e2d6ae91aa888844b659f63c7b41c

3137

3137

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?