一、FPGA 实验 项目创建、编译和下载

学生实验

• 仿照本实验,请完成以下任务

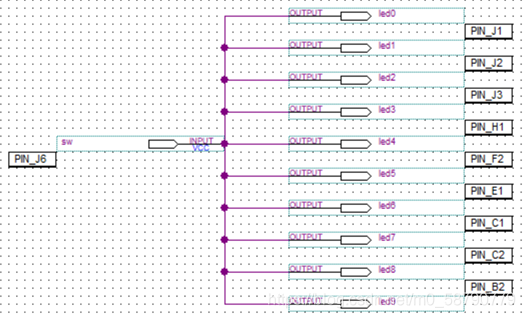

– 用1个拨码开关控制所有的LED灯亮灭

二、FPGA 实验 译码器组合逻辑

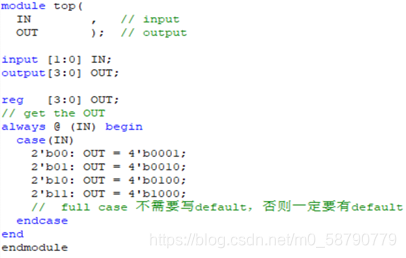

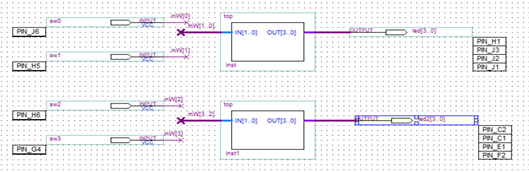

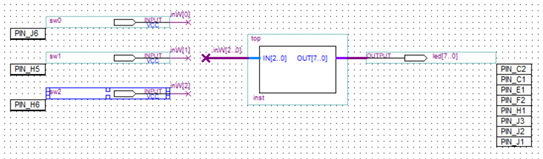

• 1、放置2个2-4译码器模块,则总共有2组SW, 每组2个,2组LED,每组4个,每组SW分别控 制其对应的LED组。

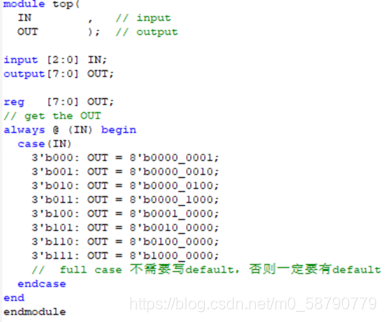

• 2、参照代码,设计一个3-8译码器,完成类似 的拨码开关实验。注意代码中的信号宽度设定。

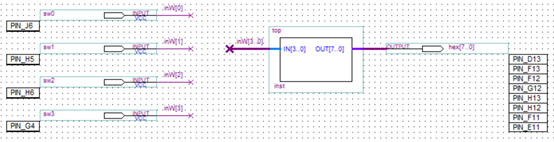

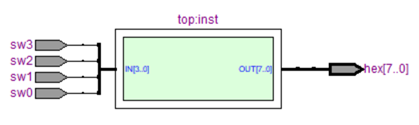

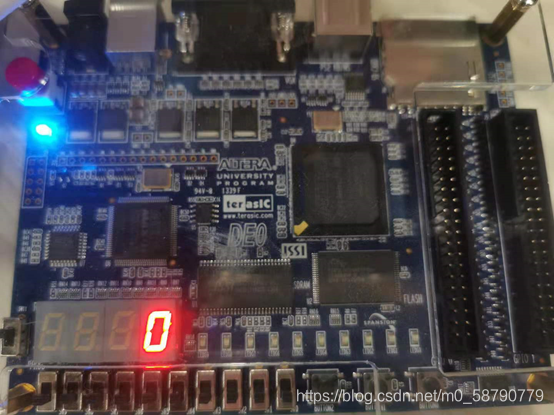

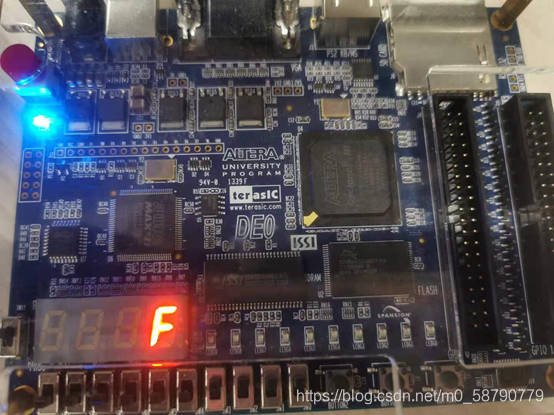

• 3、自行查阅手册中的7段译码器管脚对应关系, 用4个拨码开关控制一个7段译码器的数字,从 0-9-A-F,共16个数字和字母

module top(

IN , // input

OUT ); // output

input [3:0] IN;

output[7:0] OUT;

reg [7:0] OUT;

// get the OUT

always @ (IN) begin

case(IN)

4'b0000: OUT = 8'b11000000;

4'b0001: OUT = 8'b11111001;

4'b0010: OUT = 8'b10100100;

4'b0011: OUT = 8'b10110000;

4'b0100: OUT = 8'b10011001;

4'b0101: OUT = 8'b10010010;

4'b0110: OUT = 8'b10000010;

4'b0111: OUT = 8'b11111000;

4'b1000: OUT = 8'b10000000;

4'b1001: OUT = 8'b10010000;

4'b1010: OUT = 8'b10001000;

4'b1011: OUT = 8'b10000011;

4'b1100: OUT = 8'b11000110;

4'b1101: OUT = 8'b10100001;

4'b1110: OUT = 8'b10000110;

4'b1111: OUT = 8'b10001110;

// full case 不需要写default,否则一定要有default

endcase

end

endmodule

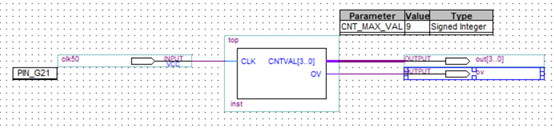

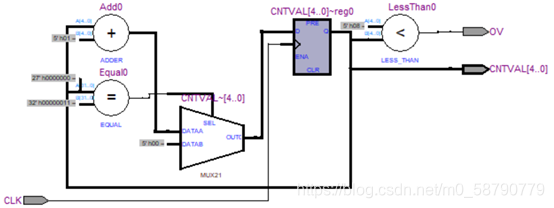

RTL:

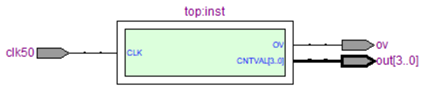

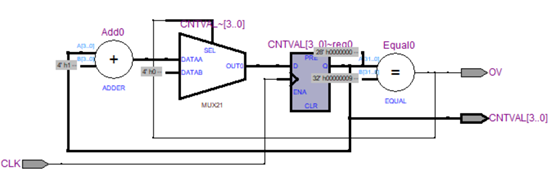

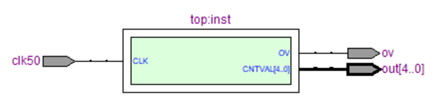

三、FPGA 实验 计数器、波形仿真、SignalTap

module top(

CLK , // 时钟,上升沿有效

CNTVAL,

OV );// 计数溢出信号,计数值为最大值时该信号为1

input CLK;

output [3:0] CNTVAL;

output OV;

reg [3:0] CNTVAL, cnt_next;

reg OV;

// 电路编译参数,最大计数值

parameter CNT_MAX_VAL = 9;

always @ (posedge CLK ) begin

if(CNTVAL==9)

CNTVAL<=0;

else

CNTVAL <= CNTVAL + 1;

end

// 组合逻辑,生成OV

always @ (CNTVAL) begin

if(CNTVAL == CNT_MAX_VAL)

OV = 1;

else

OV = 0;

end

endmodule

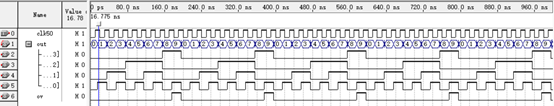

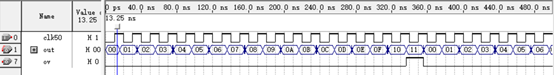

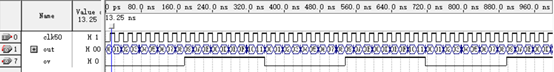

观察毛刺,为什么会有毛刺?

由于延迟的存在,就会产生竞争和冒险,造成毛刺。

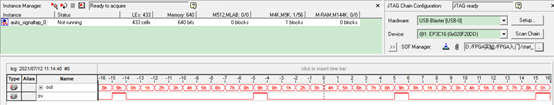

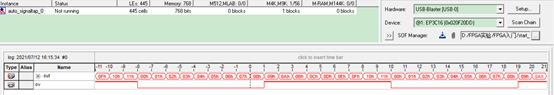

• 用SignalTap验证

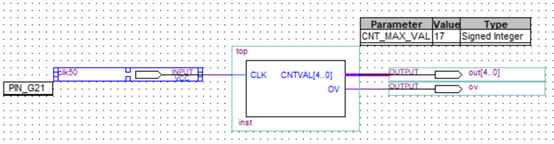

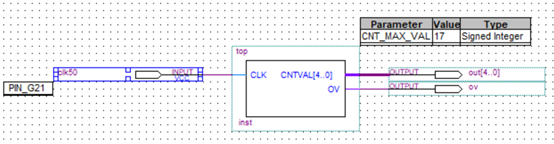

•1、参照代码,设计一个0-17的计数器,当 计数值为17的时候,OV输出1,其他输出0, 注意设定合理的信号位宽。

module top(

CLK , // 时钟,上升沿有效

CNTVAL,

OV );// 计数溢出信号,计数值为最大值时该信号为1

input CLK;

output [4:0] CNTVAL;

output OV;

reg [4:0] CNTVAL, cnt_next;

reg OV;

// 电路编译参数,最大计数值

parameter CNT_MAX_VAL = 17;

always @ (posedge CLK ) begin

if(CNTVAL==17)

CNTVAL<=0;

else

CNTVAL <= CNTVAL + 1;

end

// 组合逻辑,生成OV

always @ (CNTVAL) begin

if(CNTVAL == CNT_MAX_VAL)

OV = 1;

else

OV = 0;

end

endmodule

![]()

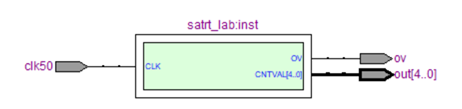

• 2、针对以上计数器,修改输出逻辑,当计 数值为0-8时,OV输出0,9-17时OV输出1

module satrt_lab(

CLK , // 时钟,上升沿有效

CNTVAL,

OV );// 计数溢出信号,计数值为最大值时该信号为1

input CLK;

output [4:0] CNTVAL;

output OV;

reg [4:0] CNTVAL, cnt_next;

reg OV;

// 电路编译参数,最大计数值

parameter CNT_MAX_VAL = 17;

always @ (posedge CLK ) begin

if(CNTVAL==17)

CNTVAL<=0;

else

CNTVAL <= CNTVAL + 1;

end

// 组合逻辑,生成OV

always @ (CNTVAL) begin

if(CNTVAL > 8)

OV = 1;

else

OV = 0;

end

endmodule

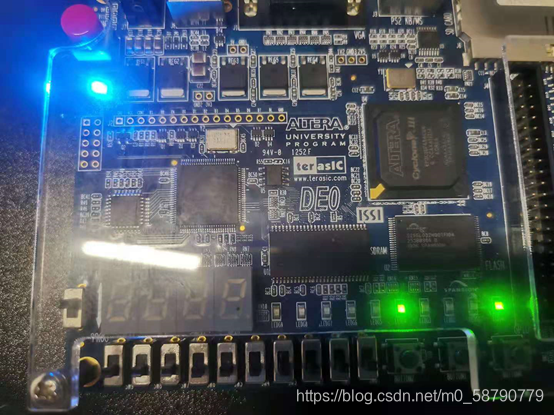

本实验教程涵盖了FPGA的基础应用,包括拨码开关控制LED、译码器、计数器、SignalTap验证、时间基准电路、移位寄存器及DDS信号生成。学生将学习如何设计并实现这些电路,通过实验理解数字逻辑和FPGA的工作原理,例如计数溢出、毛刺现象、使能信号控制、多周期计数和移位操作。

本实验教程涵盖了FPGA的基础应用,包括拨码开关控制LED、译码器、计数器、SignalTap验证、时间基准电路、移位寄存器及DDS信号生成。学生将学习如何设计并实现这些电路,通过实验理解数字逻辑和FPGA的工作原理,例如计数溢出、毛刺现象、使能信号控制、多周期计数和移位操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

855

855

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?