简介

在学习FPGA的过程中,我并没系统的学习过跨时钟域的问题,之前接触这一块也是在网上查找FPGA常见面试题做过总结,但对于其中原理并不是很了解,正好在学习这本书时,关于这一块知识讲解的非常通透,在这里做个笔记,大家一起学习!

在刚开始接触FPGA时,在一个设计中只有一个简单网线可以驱动全部触发器的时钟输入。虽然这样可以极大地简化时序分析,去除大量与多时钟区域相关的问题,但由于FPGA区域之外各种系统的约束,只利用一个时钟常常是不可能的。

1、跨越时钟区域

在处理多时钟区域时首先需要强调的问题是在区域之间传递信号的问题。有许多原因时钟跨越可能是一个主要问题:

1、故障不总是可再现的。如果有两个异步时钟区域。故障通常与时钟沿之间的相对时序有关系。时钟通常又是来自与器件的实际功能没有任何相关的外部源。

2、问题可能从工艺到工艺变化。常常发现对建立和保持约束较小的高速工艺统计上比低速工艺更少出问题(虽然由于其他的影响并不总是这种状况)。同时,一些因素-----像同步器件的实现、输出缓冲的方式------也将对故障概率产生重大的影响。

3、一般地,EDA工具也都不检测和标注这些问题。静态时序分析工具是基于单个时钟区域分析时序,并且如果以一种特殊的方式来专门做这方面的工作,也只是执行时钟间的分析。

4、通常情况下,如果不能判断出来,跨时钟区域的故障是很难检测和判断的。在任何实现开始之前,正确定义和处理全部时钟之间的接口是非常重要的。

来看示例:

如上图所示,较慢时钟周期恰恰是较快时钟周期的两倍。快速时钟的上升沿与慢速时钟的上升沿之间的时间是一个常数,并且等于dC,在这种情况下,它一直要比逻辑延迟加上由快时钟驱动的触发器的建立时间要大。在这种情形下,当时钟启动时,只要没有时钟偏移和时序冲突发生,器件就会按照预期正常工作。再来看下面一种情形:

在这种情形下,如果dC不满足由快时钟驱动的触发器的建立时间,就会造成时序冲突,这种情况可能发生在任何频率关系的任何两个时钟区域中。然而,如果两个频率不是很好的匹配,在这种规则模型中就不会发生冲突。

1.1、准稳态

在建立时间和保持时间所定义的有效时钟沿的窗口内,数据输入到触发器进行转换时,时序冲突就会发生。如果建立和保持时间有冲突,一个触发器的节点(内部节点或外部可见的节点)就会暂停在一个对逻辑0和逻辑1都无效的电平上。这种状态叫做准稳态。下面是一张示意图:

虚线之间的时间段是Din在Clock2有效沿到来时的建立/保持窗口,可是如图所示,Din在这段时间内发生了变化,这就导致输出将出现在一个对于任何逻辑值都无效的电压值上。在FPGA中,准稳态可以引起致命的故障。

解决方案一:相位控制

考虑到不同周期的有任意相位关系的两个时钟区域。如果其中至少一个时钟是在FPGA内部通过PLL(锁相环)或DLL(延迟锁相环)可控制的,另一个时钟与在PLL或DLL解决方案中那个时钟周期有倍数关系,那么相位匹配就可以用来消除时序冲突。就像上面的图6.4一样,在两个时钟区域之间数据传输有效的时间总量dC总是在它最大可能的数值,在这种情况下,只要在慢寄存器的触发电路到快寄存器的触发电路之间的传播延迟小于最快时钟的周期,不会发生建立冲突。但是在一些情况下,比如两个时钟区域的周期毫无关系,或者来自片外特定的时序要求被强加于FPGA上,就没办法通过相位控制的方式。

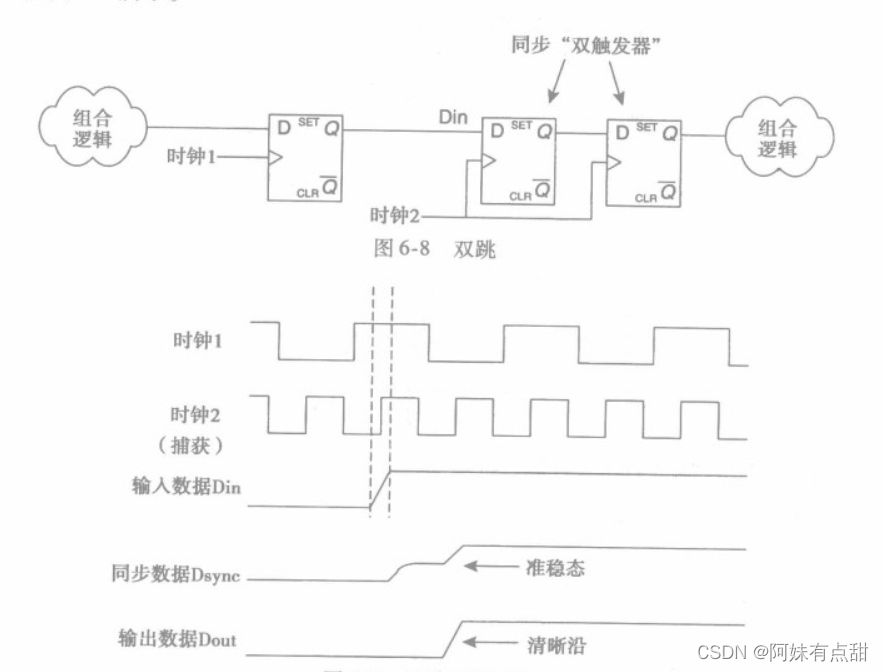

解决方案二:双跳技术

假定两个时钟区域时完全异步的(不可能用相位控制),一个减小准稳态发生几率的简单的方法是使用双跳技术。如图所示:

在这里Dsync是第一个触发器,而Dout是第二个触发器的输出。从本质上来讲,Dout用来防止其他电路发现这个亚稳态信号,并且一旦同步信号有机会稳定下来,就把它传输下去。由于在两个触发器间没有增加逻辑,就可以最大化提供信号稳定的时间总量。这种方法当数据位是总线数据的一部分(一些位可能比其他位晚一个时钟传输),或者数据到达时是单个时钟精度下降的关键处时是无用的。但是,当利用的控制信号可以经得住±1个时钟的偏差或更多时,这是有用的。

解决方案三:FIFO结构

在时钟区域之间传递信号更灵活的方式是使用先进先出(FIFO)结构。当在异步时钟区域之间传递多位信号时可以利用FIFO,FIFO最通常的应用包括在标准总线接口之间传递数据和读写突发存储器。用一个异步FIFO,数据可以在任意时间间隔在发送端运送,接收端把数据推出队列,需要一定的控制来防止溢出。考虑到溢出情形的发生,比较接收端的时钟域,发送器件的时钟域不必以一个更快的频率运行。比起接收端处理数据的时钟周期来说,更慢的时钟域意味着更少的时钟周期来通过数据给FIFO。

在许多情况下,突发传输的尺寸和到达数据的分布都不好定义,在这种情形下,握手控制对数据流进入FIFO是必须的。控制的标志包括满标志来通知发送端在FIFO中没有更多的空间了,空标志通知接收端没有更多的数据抓取。似乎一般的满和空标志是要实现的困难特性,原因是输入控制的表示常常是由输出级产生,类似的输出控制的产生是由输入级产生的。例如,驱动输入数据的逻辑必须是知道FIFO是否是满的,这只可以由输出级已经读出的数据量来决定,同样的,在输出级读数据的逻辑必须知道是否有任何新数据有效,这是由来自输入级的写指针来决定的。

FIFO的目的是处理异步时钟区域之间管理数据的传输,但是在FIFO本身的实现中关于握手标志会碰到相同的问题,为了从一个区域传递必须的信号到另一个区域,必须追溯到前一节讨论的双跳等技术,下图是一个简化的异步FIFO图:

在上图中,写地址和读地址二者在为空和满产生传递到另一个区域时必须重新同步。出现的问题是在多位地址重新同步期间,一些位可能之后其他位一个时钟周期,取决于各个引线各自的传播特性。换言之,由于两个时钟区域的异步特性一些位可能在捕获时钟的一个沿上被捕获,其他的可能在下一沿上被捕获,取决于数据到达第一个触发器是否在时钟沿之前有足够的时间。这个问题可以将二进制地址转换成格雷码来解决。格雷码是一个专门的计数器,相邻地址只有一位的差别,如果每次地址的变化只触发一位,就消除了上面的问题。这一点已经被广泛应用在FIFO内部。

分割同步模块

根据好的设计实,应该分割顶层设计使得同步模块包含在任何功能模块外部的各个模块中,这将有助于达到在逐个模块基础上理想的时钟区域的情况(整个设计一个时钟),如图所示:

2、门控时钟

2.1、时钟模块

如果有大量的时钟在ASIC中被选通,推荐把选通操作考虑成专门为产生时钟的单个模块。如图所示:

保持所有的门控时钟都在专用的时钟模块内,并从功能模块中分离出来。

2.2、选通移除

有许多巧妙的方法移除FPGA样机中的选通通道,举个例子:

`define FPGA

//`define ASIC

module clocks_block (

`ifdef ASIC

assign clock_domain_1 = system_clock_1 & clock_enable_1;

`else

assign clock_domain_1 = system_clock_1;

`endif

);

endmodule

现在许多综合工具也都会用适当的约束来做这件事。

478

478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?