NVBoard

介绍

NVBoard(NJU Virtual Board)是基于SDL开发的虚拟FPGA开发板,可以在Verilator仿真环境中模拟FPGA,支持LED,七段数码管,开关,键盘和VGA。

项目文件说明

.

├── board # 引脚说明文件

│ └── ...

├── example # 示例项目

│ └── ...

├── include

│ ├── at_scancode.h

│ ├── component.h

│ ├── configs.h

│ ├── constrs.h

│ ├── keyboard.h

│ ├── macro.h

│ ├── nvboard.h

│ ├── render.h

│ └── vga.h

├── pic # NVBoard图片资源

│ └── ...

├── scripts

│ ├── auto_pin_bind.py # 生成引脚绑定代码的脚本

│ └── nvboard.mk # NVBoard构建规则

└── src # NVBoard源码

│ ├── component.cpp

│ ├── event.cpp

│ ├── nvboard.cpp

│ ├── render.cpp

│ └── vga.cpp

├── LICENSE

└── README.md

安装教程

- 将项目拷贝到本地,

git clone https://github.com/NJU-ProjectN/nvboard.git - 通过

apt-get install libsdl2-dev libsdl2-image-dev安装SDL2和SDL2-image;对于macOS,可以通过brew install sdl2 sdl2_image安装 - 把本项目的目录设置成环境变量

NVBOARD_HOME

示例

example目录下包含一个示例项目,在该目录下通过 make run 命令可运行该项目。

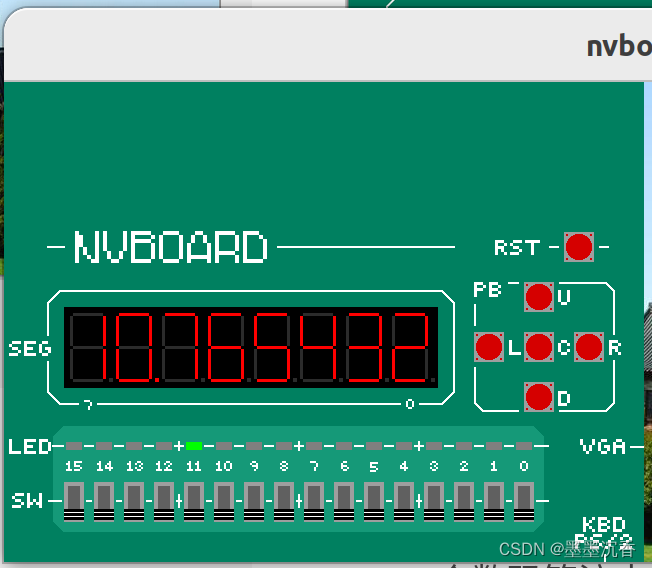

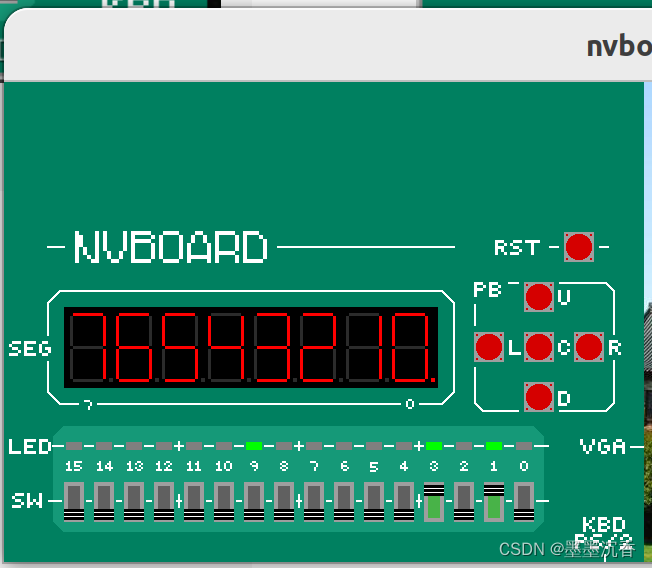

该示例的演示效果如下:

该示例的演示效果如下:

-

左边8个LED为流水灯效果(8-15)

-

拨动右边的8个拨码开关, 可控制对应LED的亮灭

-

8个数码管流水显示数字0-7

-

按钮暂无展示效果

-

窗口右侧为VGA输出, 将会展示一张图片

-

敲击键盘, 终端将会输出按键的扫描码

接入verilator步骤

API说明

NVBoard提供了以下几组API

void nvboard_init(): 初始化NVBoardvoid nvboard_quit(): 退出NVBoardvoid nvboard_bind_pin(void *signal, bool is_rt, bool is_output, int len, ...): 将HDL的信号signal连接到NVBoard里的引脚上,具体地is_rt为true时,表示该信号为实时信号,每个周期都要更新才能正确工作,如键盘和VGA相关信号;

is_rt为false时,表示该信号为普通信号,可以在NVBoard更新画面时才更新,从而提升NVBoard的性能,如拨码开关和LED灯等,无需每个周期都更新is_output为true时,表示该信号方向为输出方向(从RTL代码到NVBoard);否则为输入方向(从NVBoard到RTL代码)len为信号的长度,大于1时为向量信号- 可变参数列表

...为引脚编号列表,编号为整数;绑定向量信号时,引脚编号列表从MSB到LSB排列

void nvboard_update(): 更新NVBoard中各组件的状态,每当电路状态发生改变时都需要调用该函数

引脚绑定

手动调用nvboard_bind_pin()来绑定所有引脚较为繁琐。

为了方便进行信号的绑定,NVBoard项目提供了一套从自定义约束文件生成绑定代码的流程。具体地

- 编写一个自定义格式的约束文件,其格式为

top=top_name

# Line comment inside nxdc

signal pin

signal (pin1, pin2, ..., pink)

在约束文件的第一行,需要指定顶层模块名(上文中为top_name)。

约束文件支持两种信号绑定方式,signal pin表示将顶层模块的signal端口信号绑定到引脚pin上,

signal (pin1, pin2, ..., pink)表示将顶层模块的signal信号的每一位从高到低依次绑定到pin1, pin2, ..., pink上。

约束文件支持空行与行注释。

- 通过命令

python $(NVBOARD_HOME)/scripts/auto_pin_bind.py nxdc约束文件路径 auto_bind.cpp输出路径来生成C++文件。

调用该文件中的nvboard_bind_all_pins(dut)函数即可完成所有信号的绑定。

注意,该脚本的错误处理并不完善,若自定义约束文件中存在错误,则可能无法生成正确的报错信息与C++文件。

如果发现脚本中的错误也可以尝试修复一下然后丢pr

可以在board目录下的引脚说明文件中查看引脚信息。

其中,复位引脚RST不使用,因为NVBoard在cpp文件中包含一些内部状态,仅复位RTL设计部分会使其与NVBoard状态不一致。

一个实现全系统复位效果的简单方法是退出NVBoard并重新运行。RTL设计的复位工作由verilator的wrapper完成,具体见example/csrc/main.cpp。

#include <nvboard.h>

#include <Vtop.h>

static TOP_NAME dut;

void nvboard_bind_all_pins(Vtop* top);

static void single_cycle() {

dut.clk = 0; dut.eval();

dut.clk = 1; dut.eval();

}

static void reset(int n) {

dut.rst = 1;

while (n -- > 0) single_cycle();

dut.rst = 0;

}

int main() {

nvboard_bind_all_pins(&dut);

nvboard_init();

reset(10);

while(1) {

nvboard_update();

single_cycle();

}

}

RTL(Register Transfer Level,寄存器传输级)指:不关注寄存器和组合逻辑的细节(如使用了多少逻辑门,逻辑门之间的连接拓扑结构等),通过描述寄存器到寄存器之间的逻辑功能描述电路的HDL层次。RTL级是比门级更高的抽象层次,使用RTL级语言描述硬件电路一般比门级描述简单高效得多。

调用API

在C仿真代码中调用NVBoard提供的API

#include <nvboard.h>

// ...

nvboard_bind_all_pins(&dut);

nvboard_init();

while (1) {

// ...

nvboard_update();

}

nvboard_quit();

具体地

- 在进入verilator仿真的循环前,先对引脚进行绑定,然后对NVBoard进行初始化

- 在verilator仿真的循环中更新NVBoard各组件的状态

- 退出verilator仿真的循环后,销毁NVBoard的相关资源

编译链接

在Makefile中

- 将生成的上述引脚绑定的C++文件加入源文件列表

- 将NVBoard的构建脚本(nvboard.mk)包含进来

include $(NVBOARD_HOME)/scripts/nvboard.mk

- 通过

make nvboard-archive生成NVBoard的库文件 - 在生成verilator仿真可执行文件(即

$(NVBOARD_ARCHIVE))将这个库文件加入链接过程,并添加链接选项-lSDL2 -lSDL2_image

可以参考示例项目中的Makefile文件,即example/Makefile

下面是对于Makefile中每行代码含义的解释,参考自南京大学数字电路与计算机组成实验的Verilator仿真(二)

TOPNAME = top

NXDC_FILES = constr/top.nxdc #约束文件路径

INC_PATH ?= #?=的意义是,INC_PATH如果被未被定义,则为?=后的值,如果被定义过,则保持原来的值

VERILATOR = verilator

#在代码段结束后看这一句的详细注解

VERILATOR_CFLAGS += -MMD --build --cc -O3 \

--x-assgin fast --x-initial fast --noassert --trace

BUILD_DIR = ./build

OBJ_DIR = $(BUILD_DIR)/obj_dir

#OBJ_DIR = ./build/obj_dir

BIN = $(BUILD_DIR)/$(TOPNAME)

#BIN = ./build/top

default: $(BIN) #终极目标为default,依赖./build/top

$(shell mkdir -p $(BUILD_DIR)) #建立./build目录

SRC_AUTO_BIND = $(abspath $(BUILD_DIR)/auto_bind.cpp) #abspath:返回文件的绝对路径

#SRC_AUTO_BIND = ~/vtest/ex2/part4/build/auto_bind.cpp 此为约束文件

$(SRC_AUTO_BIND): $(NXDC_FILES) # 目标文件(约束文件SRC_AUTO_BIND)的建立依赖于constr/top.nxdc

python3 $(NVBOARD_HOME)/scripts/auto_pin_bind.py $^ $@

# python3 $(NVBOARD_HOME)/scripts/auto_pin_bind.py constr/top.nxdc auto_bin.cpp

#此命令用来生成auto_bin.cpp文件

VSRCS = $(shell find $(abspath ./vsrc) -name "*.v")

#在~/vtest/ex2/part4/vsrc目录中寻找所有的.v文件

#VSRCS = top.v bcd7seg.v

CSRCS = $(shell find $(abspath ./csrc) -name "*.c" -or -name "*.cc" -or -name "*.cpp")

#CSRCS = sim_main.cpp

CSRCS += $(SRC_AUTO_BIND)

#CSRCS = sim_main.cpp auto_bind.cpp

include $(NVBOARD_HOME)/scripts/nvboard.mk

#在该Makefile中引用其他Makefile

INCFLAGS = $(addprefix -I, $(INC_PATH))

#INCFLAGS = -I

CFLAGS += $(INCFLAGS) -DTOP_NAME="\"V$(TOPNAME)\""

#CFLAGS = -I -DTOP_NAME="\"Vtop\""

LDFLAGS += -lSDL2 -lSDL2_image

$(BIN): $(VSRCS) $(CSRCS) $(NVBOARD_ARCHIVE)

#./build/top文件的建立依赖于 top.v bcd7seg.v sim_main.cpp auto_bind.cpp 以及verilator仿真可执行文件

@rm -rf $(OBJ_DIR)

$(VERILATOR) $(VERILATOR_CFLAGS)\

--top-module $(TOPNAME) $^\

$(addprefix -CFLAGS , $(CFLAGS)) $(addprefix -LDFLAGS , $(LDFLAGS)) \

--Mdir $(OBJ_DIR) --exe -o $(abspath $(BIN))

# verilator -MMD --build --cc -O3 --x-assgin fast --x-initial fast --noassert --trace \

#--top-module top top.v bcd7seg.v sim_main.cpp auto_bind.cpp \

#-CFLAGS -I -DTOP_NAME="\"VTOP\"" -LDFLAGS -lSDL2 -lSDL2_image \

#--Mdir ./build/obj_dir --exe -o ./build/top

#--top-module top 指定顶层文件名 --Mdir 将生成的文件都放入obj_dir目录中 --exe -o ./build/top 产生可执行文件并指定名字为./build/top

all: default

run:$(BIN)

@$^

#make run 执行可执行文件 ./build/top

clean:

rm -rf $(BUILD_DIR)

.PHONY: default all clean run

For best performance, run Verilator with the -O3 --x-assign fast --x-initial fast --noassert options. The -O3 option will require a longer time to run Verilator, and --x-assign fast --x-initial fast may increase the risk of reset bugs in trade for performanc.

上句摘录自verilator官网

GCC的命令参数有很多,下面只介绍-MMD:

生成文件关联的信息。包含目标文件所依赖的所有源代码,但是输出将导入到.d的文件里面。

想要了解更多可以点击这里

.PHONY(伪目标)

伪目标是这样一个目标:它不代表一个真正的文件名,在执行make时可以指定这个目标来执行所在规则定义的命令,有时也可以将一个伪目标称为标签。伪目标通过PHONY来指明。 PHONY定义伪目标的命令一定会被执行。

更详细的内容可以参考这里

特技

- 可以用

include/configs.h选择贴图,让自己的虚拟FPGA开发板更有特色,贴图放在pic目录下;

3247

3247

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?