状态机,启动!!!

Finite State Machines

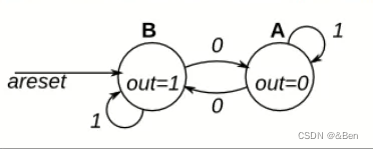

119 Simple FSM 1 (asynchronous reset)

Moore型和Mealy型状态机:

- 摩尔状态机:输出只和当前状态有关而与输入无关。在波形上,如果想输出z=1,必须C状态形成,即寄存器中的两个1都打进去后才可以,输出z=1会在下一个有效沿到来的时候被赋值。

- 米利状态机:输出不仅和当前状态有关而且和输入有关。在波形上,状态在B的时候如果输入为1,则直接以组合电路输出z=1,不需要等到下个有效沿到来。

题目要求设计如图所示的摩尔型状态机,使用异步复位。题目给了两段式状态机的模板。

module top_module(

input clk,

input areset, // Asynchronous reset to state B

input in,

output out);//

parameter A=0, B=1;

reg state, next_state;

always @(*) begin // This is a combinational always block

case(state)

A:begin

if(in==1)

next_state<=A;

else

next_state<=B;

end

B:begin

if(in==1)

next_state<=B;

else

next_state<=A;

end

default:;

endcase

end

always @(posedge clk, posedge areset) begin // This is a sequential always block

// State flip-flops with asynchronous reset

if(areset)

state<=B;

else

state<=next_state;// State transition logic

end

// Output logic

// assign out = (state == ...);

assign out = (state==B);

endmodule

120 Simple FSM 1 (synchronous reset)

与119一致,只是复位变成了同步复位,同时题目给的模板变成一段式。

// Note the Verilog-1995 module declaration syntax here:

module top_module(clk, reset, in, out);

input clk;

input reset; // Synchronous reset to state B

input in;

output out;//

reg out;

// Fill in state name declarations

parameter A = 0,B = 1;

reg present_state, next_state;

always @(posedge clk) begin

if (reset==1'b1) begin

present_state<=B;

out<=1'b1;// Fill in reset logic

end else begin

case (present_state)

// Fill in state transition logic

A:begin

if(in==1'b1)

next_state=A;

else

next_state=B;

end

B:begin

if(in==1'b1)

next_state=B;

else

next_state=A;

end

endcase

// State flip-flops

present_state = next_state;

case (present_state)

// Fill in output logic

A:out=1'b0;

B:out=1'b1;

endcase

end

end

endmodule

这道题被阻塞赋值和非阻塞赋值整神了,在这里always里下意识用了非阻塞赋值结果报错,想了想如果用非阻塞,会在always结束才更新next_state的值。

这里还有一个点想不明白,在复位的代码里,更不更新present_state也对输出不产生影响呀,不明白为啥把present_state<=B删掉报错。

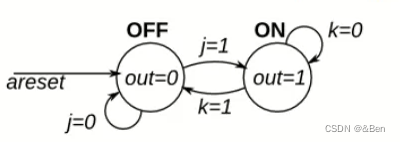

121 Simple FSM 2 (asynchronous reset)

这道题有两个状态,两个输入和一个输出,异步复位。题目给的两段式的状态机模板。

module top_module(

input clk,

input areset, // Asynchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case(state)

OFF:begin

if(j==1)

next_state<=ON;

else

next_state<=OFF;

end

ON:begin

if(k==1)

next_state<=OFF;

else

next_state<=ON;

end

endcase

end

always @(posedge clk, posedge areset) begin

// State flip-flops with asynchronous reset

if(areset)

state<=OFF;

else begin

state<=next_state;

end

end

// Output logic

// assign out = (state == ...);

assign out = (state==ON);

endmodule

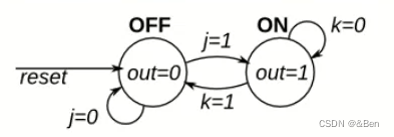

122 Simple FSM 2 (synchronous reset)

与121相同,变成了同步复位。

module top_module(

input clk,

input reset, // Synchronous reset to OFF

input j,

input k,

output out); //

parameter OFF=0, ON=1;

reg state, next_state;

always @(*) begin

// State transition logic

case(state)

ON:begin

if(k==1)

next_state<=OFF;

else

next_state<=ON;

end

OFF:begin

if(j==1)

next_state<=ON;

else

next_state<=OFF;

end

endcase

end

always @(posedge clk) begin

// State flip-flops with synchronous reset

if(reset)

state<=OFF;

else

state<=next_state;

end

// Output logic

// assign out = (state == ...);

assign out = (state == ON);

endmodule

感觉这四个题不仅考了状态机还想考同步异步复位的知识点,却没想到我花时间最多的地方在纠结一段式的阻塞赋值和非阻塞赋值。。。。。。。

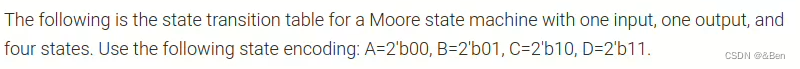

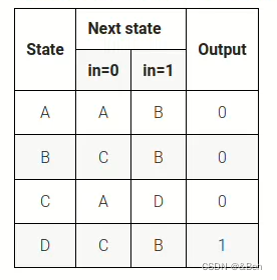

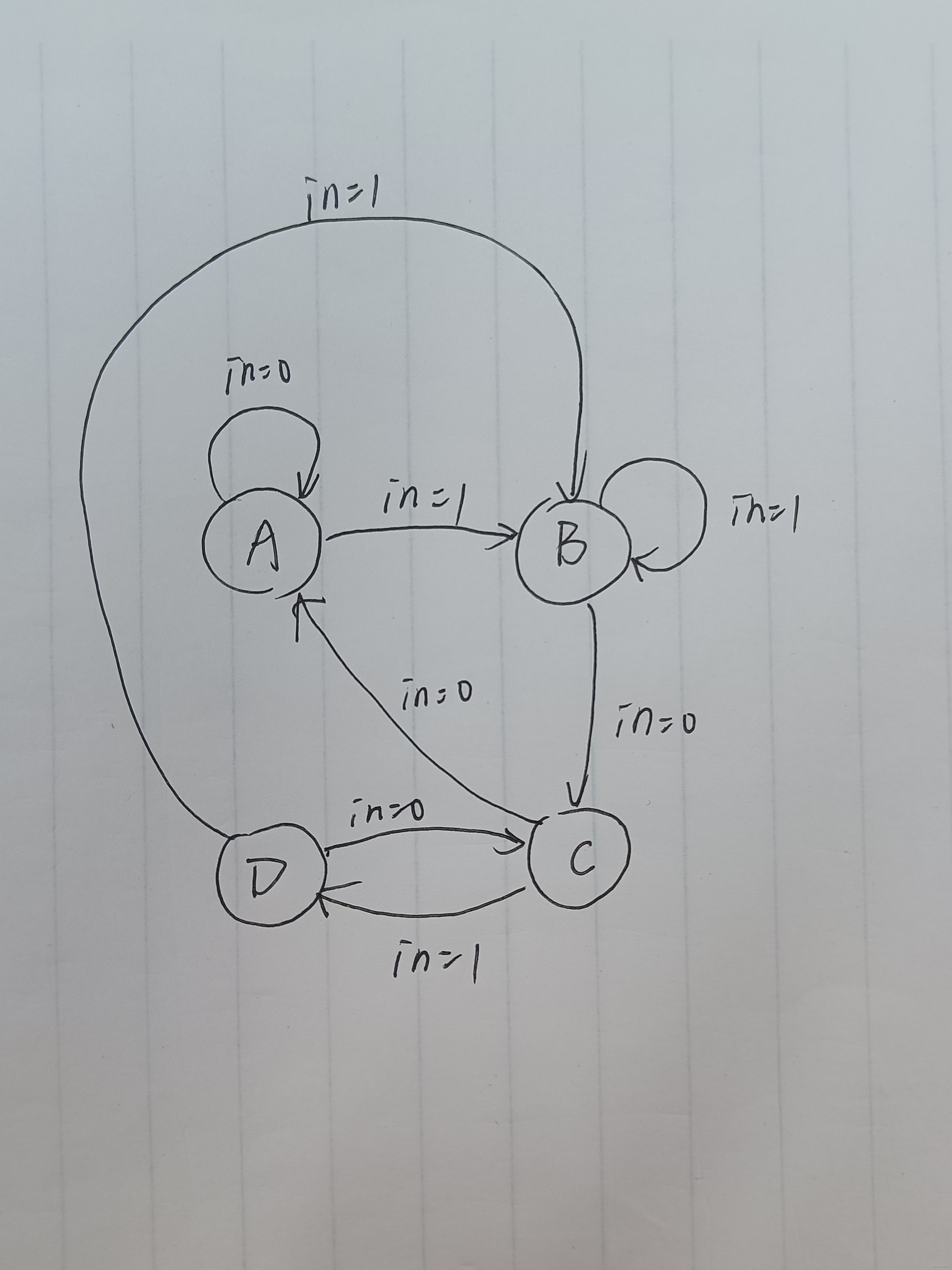

123 Simple state transitions 3

给了状态转移表和编码方式,要求完成状态机代码的设计。

这个题其实把状态转移图画出来就好了。 值得注意的是,本题并没有给出复位和时钟,所以整体其实是个组合逻辑。

module top_module(

input in,

input [1:0] state,

output [1:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

always @(*)begin

case(state)

A:begin

if(in==1)

next_state=B;

else

next_state=A;

end

B:begin

if(in==1)

next_state=B;

else

next_state=C;

end

C:begin

if(in==1)

next_state=D;

else

next_state=A;

end

D:begin

if(in==1)

next_state=B;

else

next_state=C;

end

endcase

end

assign out = (state==D);

endmodule

124 Simple one-hot state transitions 3

124和123的状态转移逻辑是一样的,不同的是124采用的是独热码的编码方式。

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = (state[A]&~in)|(state[C]&~in);

assign next_state[B] = (state[A]&in)|(state[B]&in)|(state[D]&in);

assign next_state[C] = (state[B]&~in)|(state[D]&~in);

assign next_state[D] = state[C]∈

// Output logic:

assign out = state[D];

endmodule

125 Simple FSM 3 (asynchronous reset)

与123的状态转移逻辑相同,不同的是加入了时钟和复位,采用异步复位。

module top_module(

input clk,

input in,

input areset,

output out); //

parameter A=2'b00,B=2'b01,C=2'b10,D=2'b11;

reg [1:0] state,next_state;

// State transition logic

always @(*)begin

case(state)

A:begin

if(in==1)

next_state<=B;

else

next_state<=A;

end

B:begin

if(in==1)

next_state<=B;

else

next_state<=C;

end

C:begin

if(in==1)

next_state<=D;

else

next_state<=A;

end

D:begin

if(in==1)

next_state<=B;

else

next_state<=C;

end

endcase

end

// State flip-flops with asynchronous reset

always @(posedge clk or posedge areset)begin

if(areset)

state<=A;

else

state<=next_state;

end

// Output logic

assign out = (state == D);

endmodule

126 Simple FSM 3 (synchronous reset)

与125相同,不同的是复位方式变成了同步复位。

module top_module(

input clk,

input in,

input reset,

output out); //

parameter A=2'b00,B=2'b01,C=2'b10,D=2'b11;

reg [1:0] state,next_state;

// State transition logic

always @(*)begin

case(state)

A:begin

if(in==1)

next_state<=B;

else

next_state<=A;

end

B:begin

if(in==1)

next_state<=B;

else

next_state<=C;

end

C:begin

if(in==1)

next_state<=D;

else

next_state<=A;

end

D:begin

if(in==1)

next_state<=B;

else

next_state<=C;

end

endcase

end

// State flip-flops with asynchronous reset

always @(posedge clk)begin

if(reset)

state<=A;

else

state<=next_state;

end

// Output logic

assign out = (state == D);

endmodule

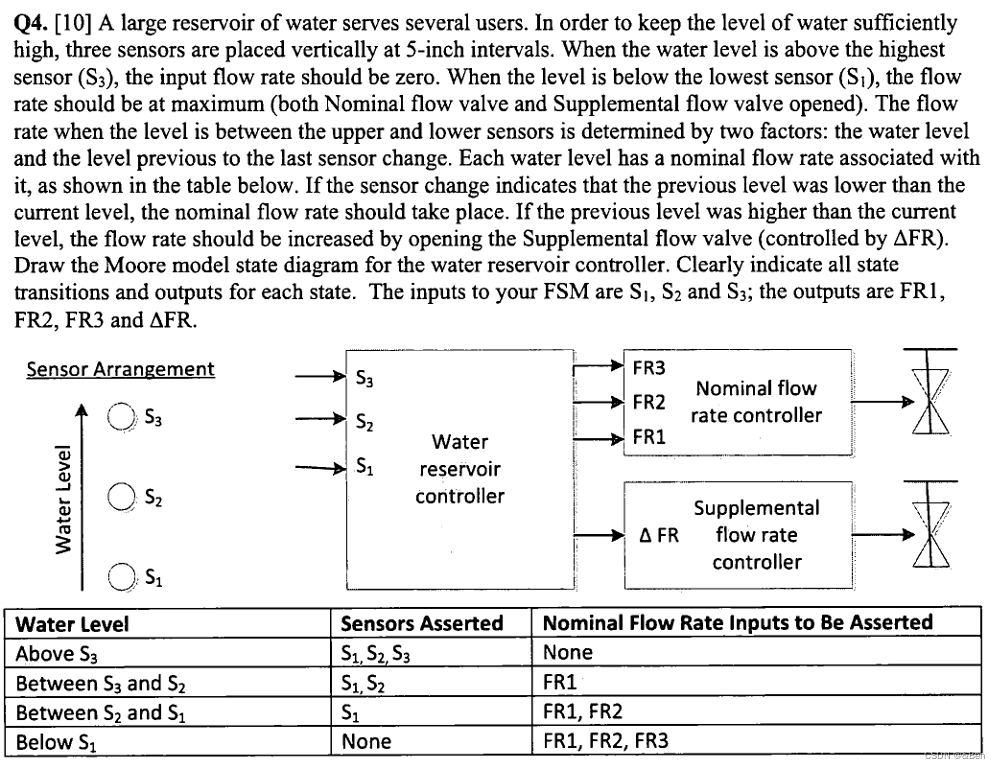

127 Design a Moore FSM

Q4.[10]一个大型蓄水池为几个用户服务。为了保持足够高的水位,三个传感器垂直放置在5英寸间隔。当水位高于最高传感器(S3)时,输入流量应为零。当水位低于最低传感器(S1)时,流量应在最大(公称流量阀和补充流量阀都打开)。上下传感器之间的流量是由两个因素决定的:水位和上次传感器之前的水位变化。如下表所示,每个水位都有一个与之相关的名义流量。如果传感器变化表明前一电平低于当前水平,则应进行标称流量。如果以前的水位高于楔形水位,则应通过开启补充流量阀(由OFR控制)来提高流量。明确表示所有状态

每个状态的转换和输出。您的FSM的输入是S、S2和S3;输出是FR1、FR2、FR3和dfr。

这个题有两个关键点,首先是根据当前水位来调整Nominal flow的个数,其次是根据前一状态的水位和当前状态的水位来控制Supplemental是否开关。同时题目要求异步复位为与水位长时间低的状态。

这种题目先应该分析状态的个数以及状态转移的方式。此题中一共有6个状态,有fr1fr2fr3和dfr组成,{fr3,fr2,fr1}只有4中状态,{000,001,011,111}通过分析可以知道,当水位处于最高位和最低位时,dfr要么为0要么为1(前一状态不可能比现一状态还高,前一状态不可能比现一状态还低),在中间时,dfr都有两种选择,即前一状态要么比现一状态高,要么比现一状态低。

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

parameter A=0,B=1,C=2,D=3,E=4,F=5;

reg [2:0] state,next_state;

always @(*)

begin

case(state)

A:next_state = s[1]?B:A;

B:next_state = s[2]?D:(s[1]?B:A);//看s第二位是否为1,若不为1,若1位位1任可保持在第二位,维持B状态,否则掉回A状态

C:next_state = s[2]?D:(s[1]?C:A);

D:next_state = s[3]?F:(s[2]?D:C);

E:next_state = s[3]?F:(s[2]?E:C);

F:next_state = s[3]?F:E;

default:next_state = 'x;

endcase

end

always @(posedge clk)

begin

if(reset)

state <= A;

else

state <= next_state;

end

always @(*)

begin

case(state)

A:{fr3,fr2,fr1,dfr} = 4'b1111;

B:{fr3,fr2,fr1,dfr} = 4'b0110;

C:{fr3,fr2,fr1,dfr} = 4'b0111;

D:{fr3,fr2,fr1,dfr} = 4'b0010;

E:{fr3,fr2,fr1,dfr} = 4'b0011;

F:{fr3,fr2,fr1,dfr} = 4'b0000;

default: {fr3,fr2,fr1,dfr} = 'x;

endcase

end

endmodule

316

316

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?