目录

1、频率计介绍

频率计是检测脉冲信号频率的电子测量仪器。对于其它波形,需通过前级电路处理得到脉冲波再送往

2、频率计测量方法

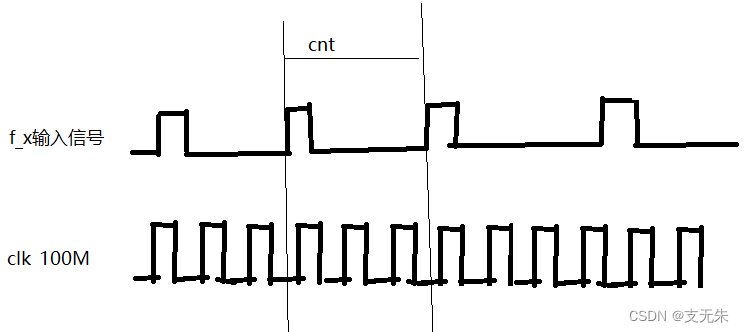

检测脉冲信号上升沿的时间间隔,对获得的数据进行处理,可以得到脉冲信号的频率。

计算公式:Fx=Fclk/cnt;

此种测量方法适合测量低频信号。在实际应用中非常适合测量汽车车速传感器等传感器模块产生的脉冲波频率。

3、Verilog代码

获得上升沿之间计数器的数值,本模块主要完成此设计。

module cesu(clk,clr,f_x,f);

input clk;

input clr;

input f_x;//输入信号

output [10:0]f;//测得频率

parameter SYS_CLK = 100000000;

wire f_x_edge;//脉冲信号上升沿检测

reg f_x_r;

reg f_x_r_p;

//脉冲信号上升沿检测

always@(posedge clk or posedge clr)//复位信号clr高电平有效

if(clr)

begin

f_x_r<=0;

f_x_r_p<=0;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

554

554

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?