名称:频率计的设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

实训要求

1.用FPGA实现8位频率计的设计

2、被测频率范围为00000000到99999999Hz 3用8个八段数码管显示测频结果 4、其它功能

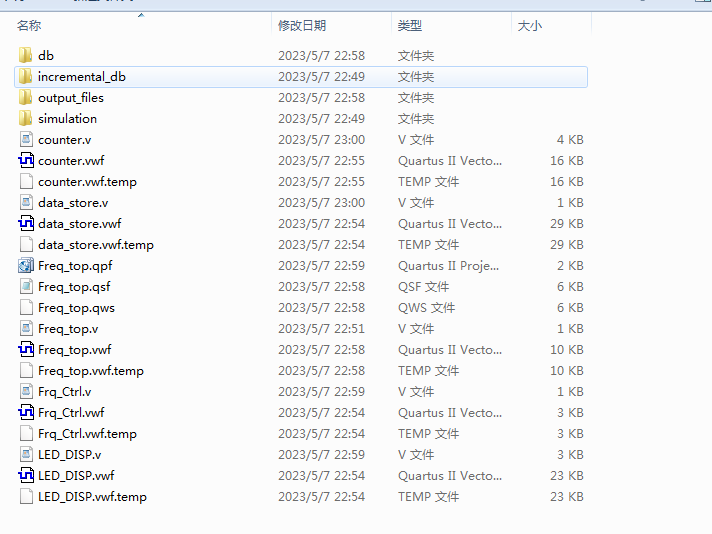

1. 工程文件

a

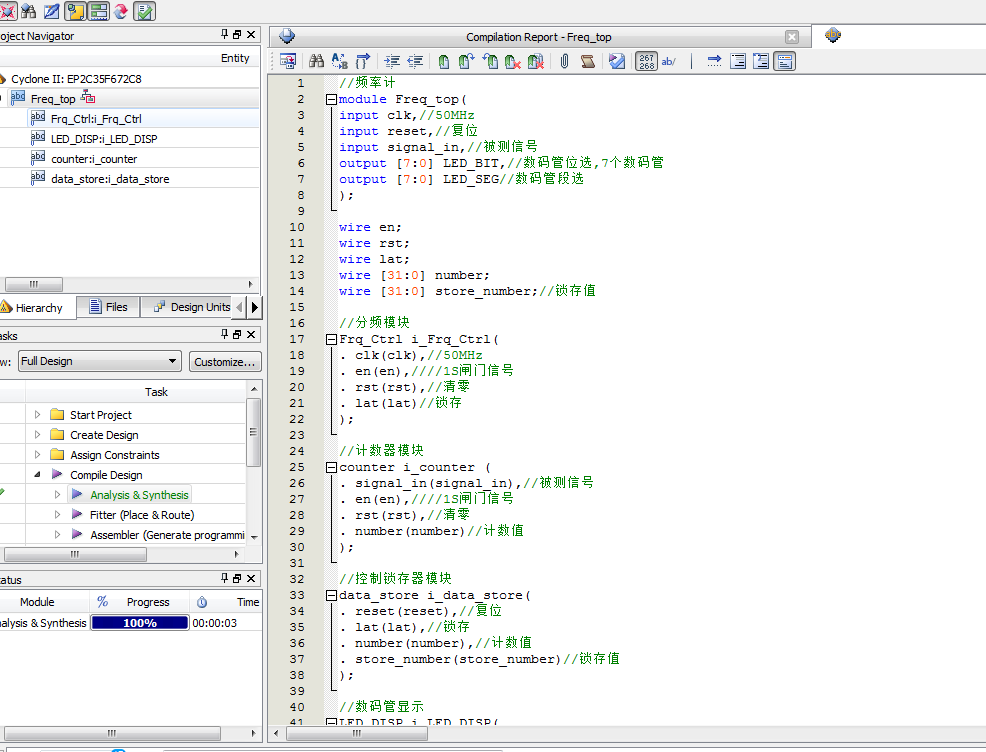

2. 程序文件

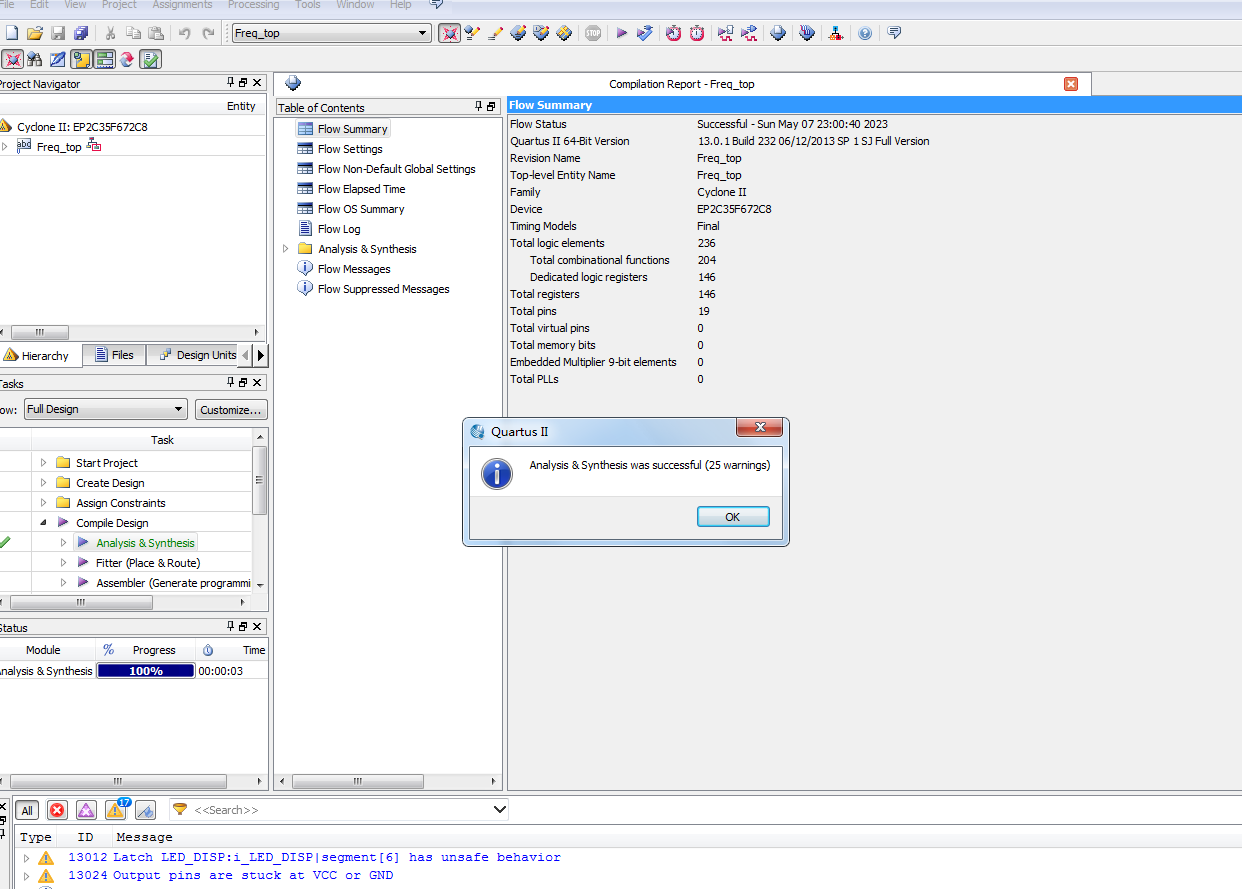

3. 程序编译

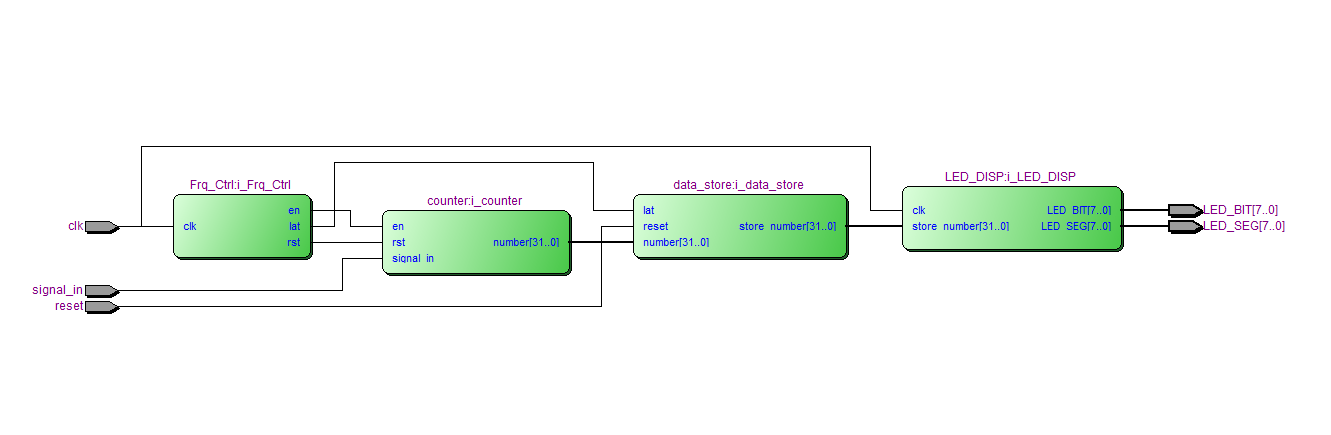

4. RTL图

5. 仿真图

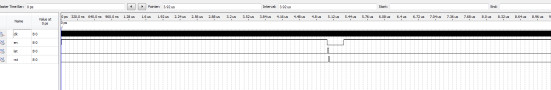

整体仿真图

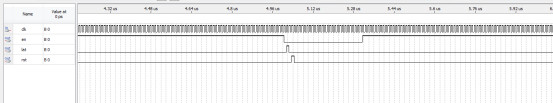

控制信号产生模块

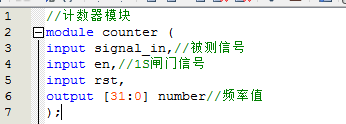

计数器模块

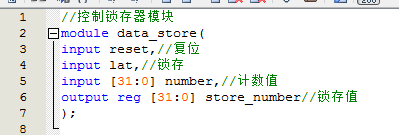

控制锁存器模块

动态显示模块

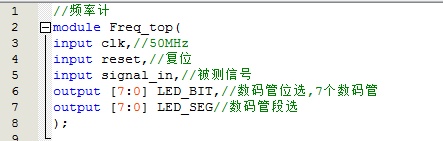

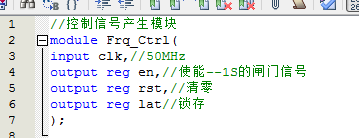

部分代码展示:

//频率计 module Freq_top( input clk,//50MHz input reset,//复位 input signal_in,//被测信号 output [7:0] LED_BIT,//数码管位选,7个数码管 output [7:0] LED_SEG//数码管段选 ); wire en; wire rst; wire lat; wire [31:0] number; wire [31:0] store_number;//锁存值 //控制信号产生模块 Frq_Ctrl i_Frq_Ctrl( . clk(clk),//50MHz . en(en),1S闸门信号 . rst(rst),//清零 . lat(lat)//锁存 ); //计数器模块 counter i_counter ( . signal_in(signal_in),//被测信号 . en(en),1S闸门信号 . rst(rst),//清零 . number(number)//计数值 ); //控制锁存器模块 data_store i_data_store( . reset(reset),//复位 . lat(lat),//锁存 . number(number),//计数值 . store_number(store_number)//锁存值 ); //数码管显示 LED_DISP i_LED_DISP( . clk(clk),// . store_number(store_number),//锁存值 . LED_BIT(LED_BIT),//数码管位选,4个数码管 . LED_SEG(LED_SEG)//数码管段选 ); endmodule

源代码

扫描文章末尾的公众号二维码

1391

1391

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?