名称:基于FPGA的数字频率计设计VHDL代码ISE仿真(文末获取)

软件:ISE

语言:VHDL

代码功能:

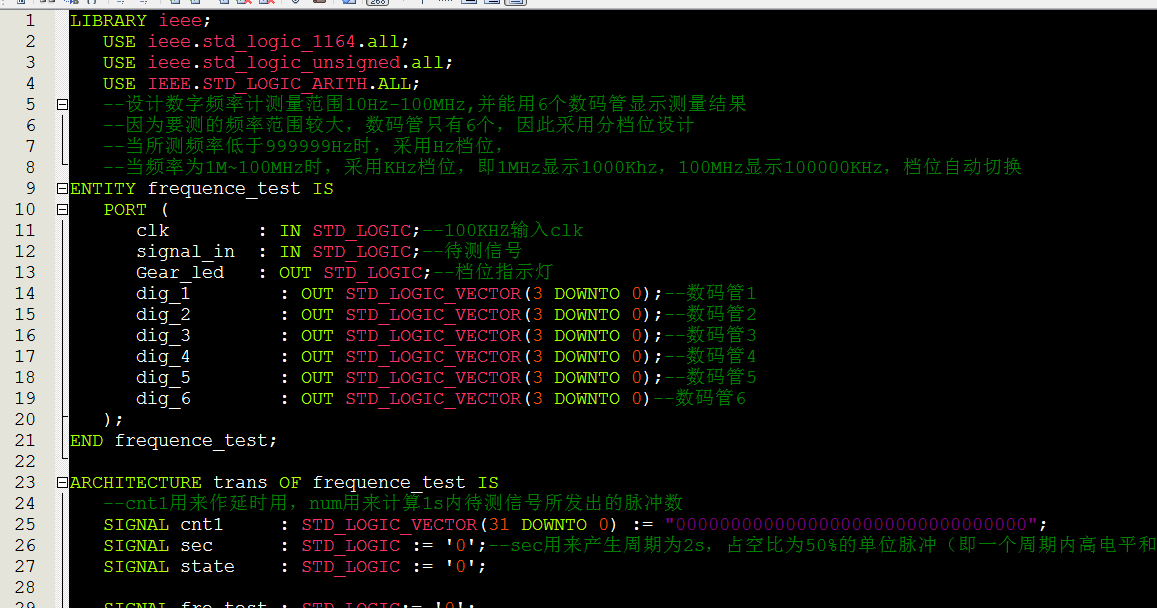

设计数字频率计测量范围10Hz-100MHz,并能用6个数码管显示测量结果

因为要测的频率范围较大,数码管只有6个,因此采用分档位设计

当所测频率低于999999Hz时,采用Hz档位,

当频率为1M~100MHz时,采用KHz档位,即1MHz显示1000Khz,100MHz显示100000KHz,档位自动切换

1.设计方案

频率计的功能是用于测试输入信号的频率,信号频率等于每秒钟的信号周期个数,即信号脉冲个数。因此设计思路为首先产生一个1秒计时窗口信号,然后再这1秒内计算待测信号的脉冲个数,最后将该计数值显示在数码管上即得到信号频率。

设计数字频率计测量范围10Hz-100MHz,并能用6个数码管显示测量结果,因为要测的频率范围较大,数码管只有6个,因此采用分档位设计,当所测频率低于999999Hz时,采用Hz档位,当频率为1M~100MHz时,采用KHz档位,即1MHz显示1000Khz,100MHz显示100000KHz,档位自动切换。

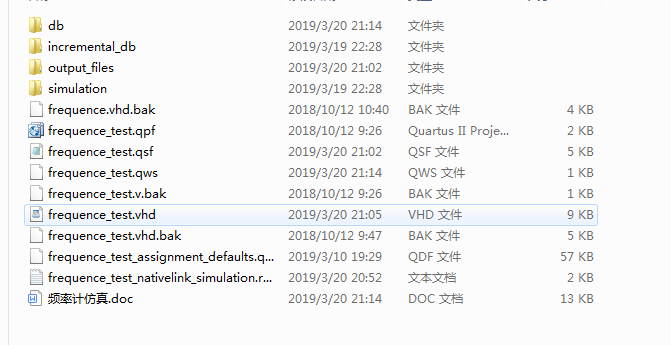

2.工程文件

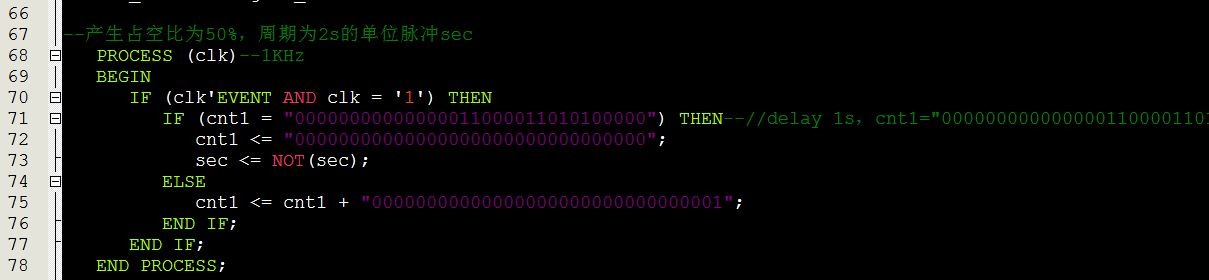

2.1 计时进程

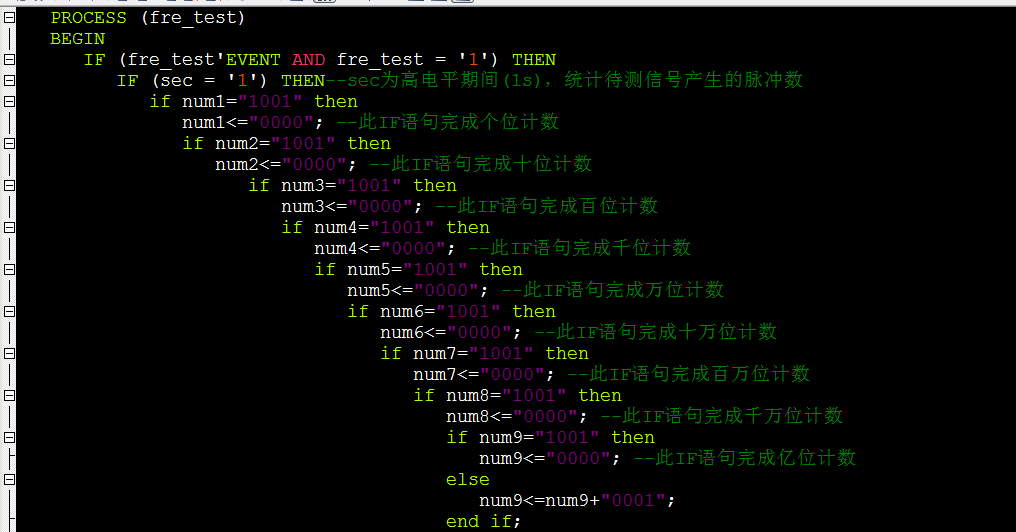

2.2 脉冲计数进程

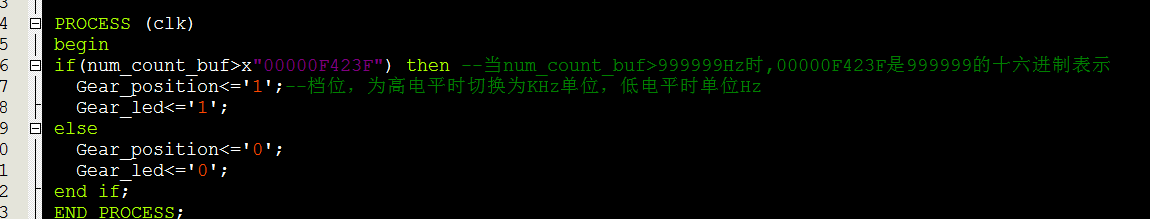

自动切换档位

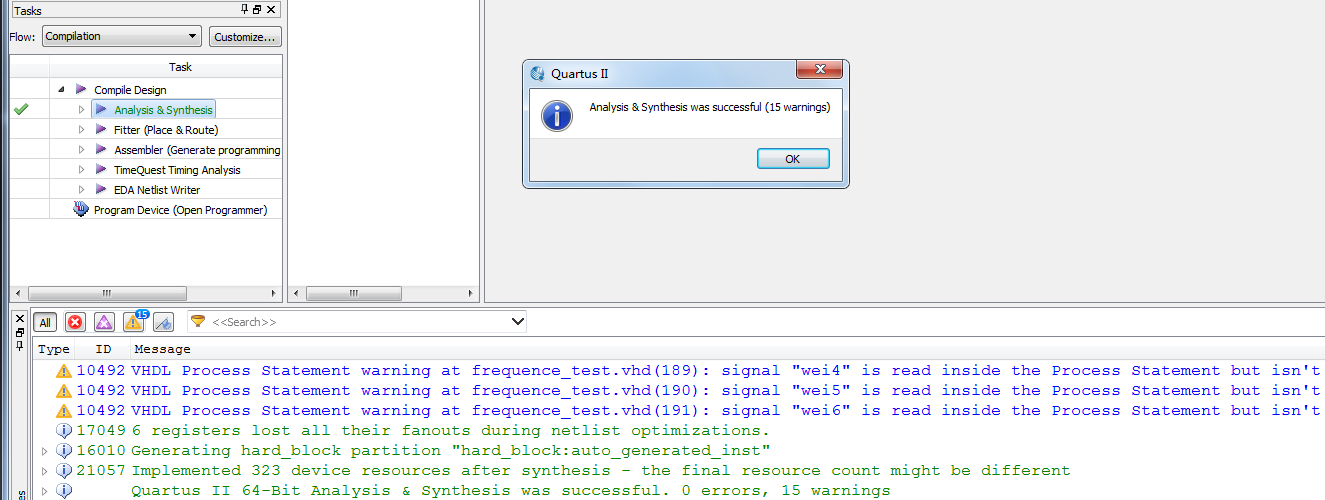

3.程序运行

4.程序仿真

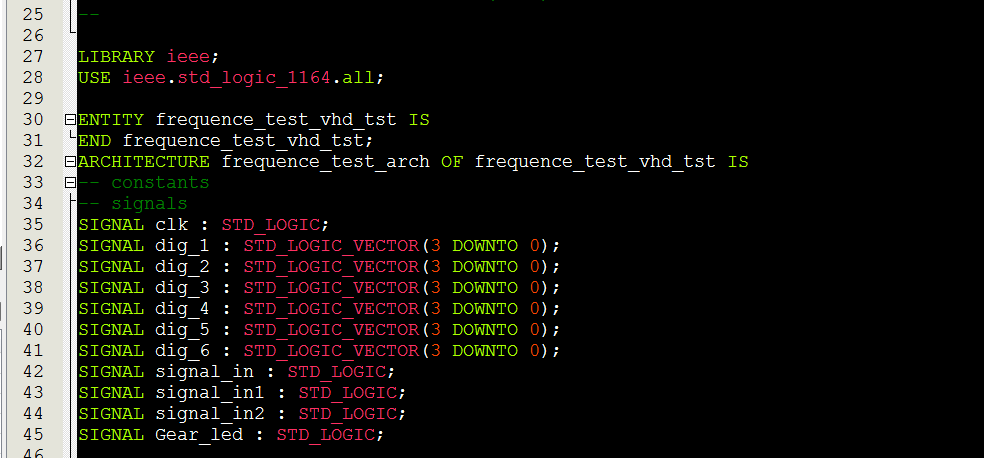

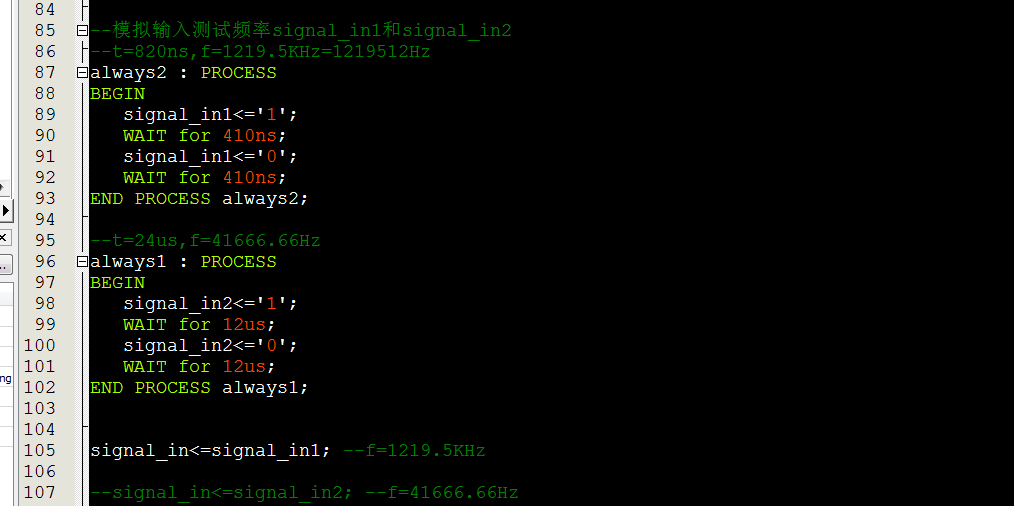

Testbench

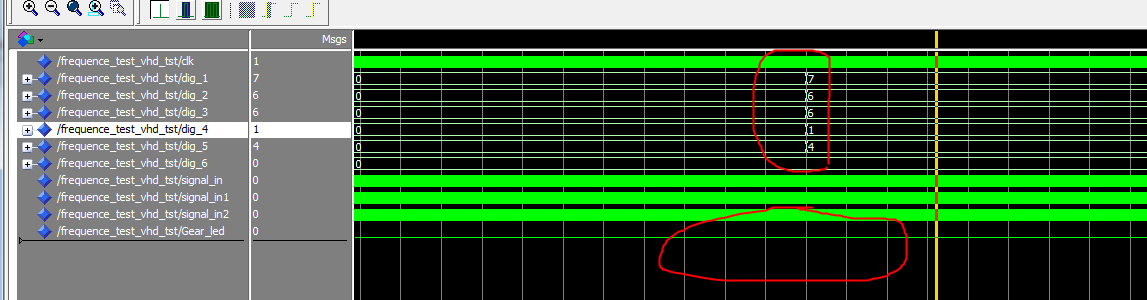

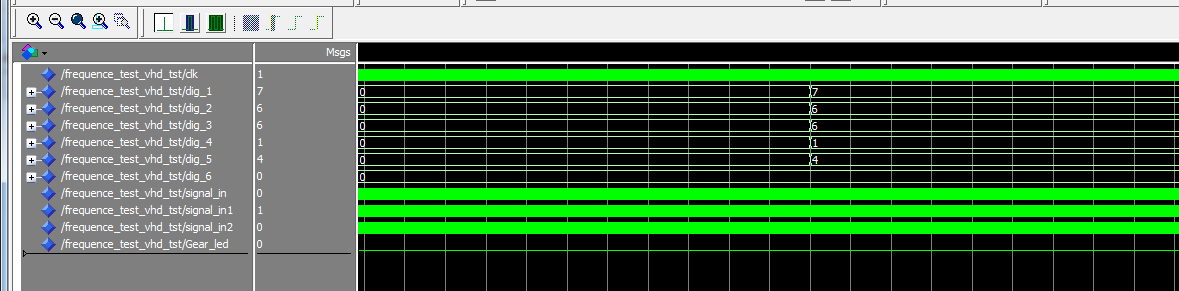

Testbench模拟2种不同档位的频率输入,频率1=1219KHz,频率2=41666.7Hz

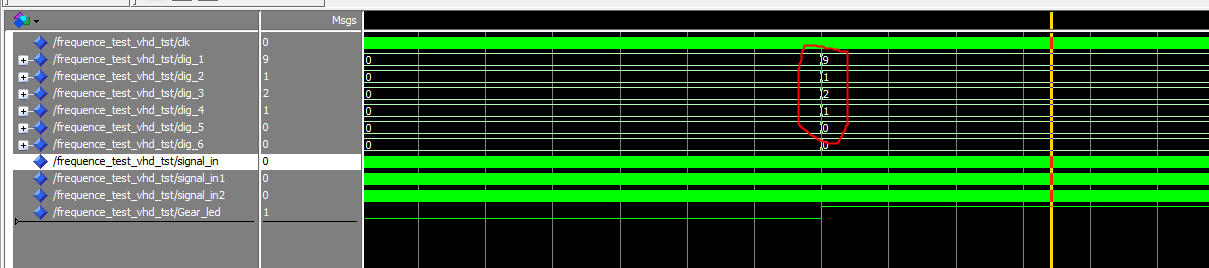

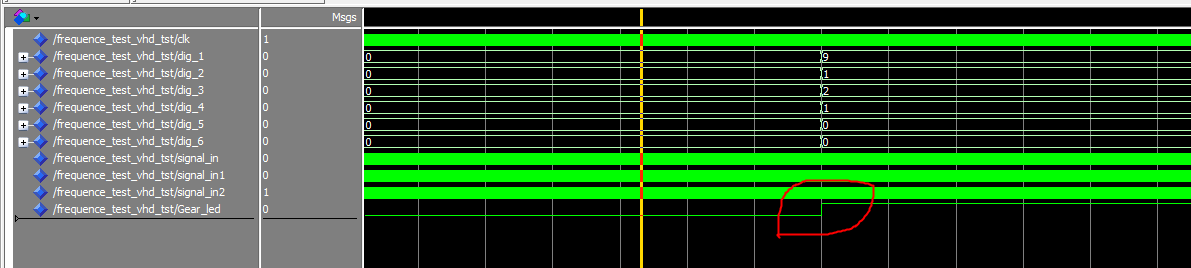

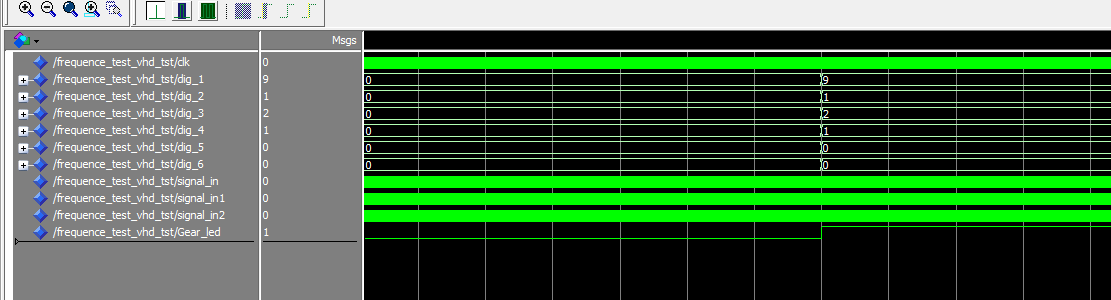

仿真图

signal_in<=signal_in1; --f=1219.5KHz

下图红圈可见档位指示信号切换为高电平

signal_in<=signal_in2; --f=41666.66Hz

下图红圈可见档位指示信号为低电平

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; USE IEEE.STD_LOGIC_ARITH.ALL; --设计数字频率计测量范围10Hz-100MHz,并能用6个数码管显示测量结果 --因为要测的频率范围较大,数码管只有6个,因此采用分档位设计 --当所测频率低于999999Hz时,采用Hz档位, --当频率为1M~100MHz时,采用KHz档位,即1MHz显示1000Khz,100MHz显示100000KHz,档位自动切换 ENTITY frequence_test IS PORT ( clk : IN STD_LOGIC;--100KHZ输入clk signal_in : IN STD_LOGIC;--待测信号 Gear_led : OUT STD_LOGIC;--档位指示灯 dig_1 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管1 dig_2 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管2 dig_3 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管3 dig_4 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管4 dig_5 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--数码管5 dig_6 : OUT STD_LOGIC_VECTOR(3 DOWNTO 0)--数码管6 ); END frequence_test; ARCHITECTURE trans OF frequence_test IS --cnt1用来作延时用,num用来计算1s内待测信号所发出的脉冲数 SIGNAL cnt1 : STD_LOGIC_VECTOR(31 DOWNTO 0) := "00000000000000000000000000000000"; SIGNAL sec : STD_LOGIC := '0';--sec用来产生周期为2s,占空比为50%的单位脉冲(即一个周期内高电平和低电平持续时间均为1s) SIGNAL state : STD_LOGIC := '0'; SIGNAL fre_test : STD_LOGIC:= '0'; SIGNAL wei1 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei2 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei3 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei4 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei5 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei6 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei7 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei8 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei9 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; -- SIGNAL num1 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num2 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num3 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num4 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num5 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num6 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num7 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num8 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL num9 : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL jishu : STD_LOGIC_VECTOR(15 DOWNTO 0):= "0000000000000000"; SIGNAL tab : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL Gear_position : STD_LOGIC:= '0';--档位,为高电平时切换为KHz单位,低电平时单位Hz SIGNAL num_count : STD_LOGIC_VECTOR(39 DOWNTO 0):= x"0000000000"; SIGNAL num_count_buf : STD_LOGIC_VECTOR(39 DOWNTO 0):= x"0000000000"; SIGNAL wei1_display : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei2_display : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei3_display : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei4_display : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei5_display : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; SIGNAL wei6_display : STD_LOGIC_VECTOR(3 DOWNTO 0):= "0000"; BEGIN fre_test <= signal_in;

源代码

扫描文章末尾的公众号二维码

1834

1834

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?