Quartus-II 实现D触发器

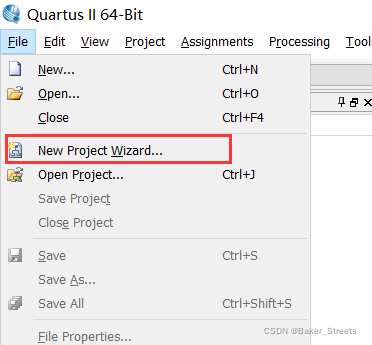

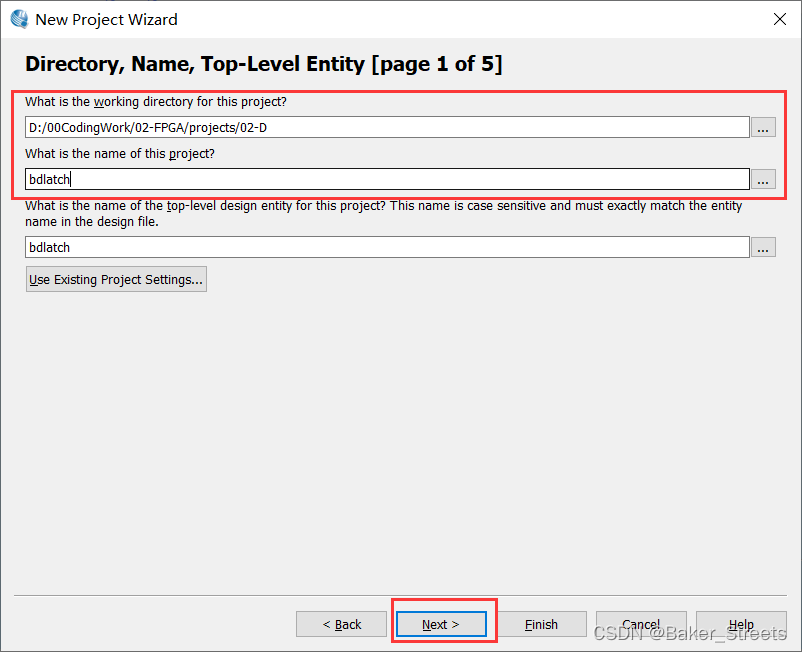

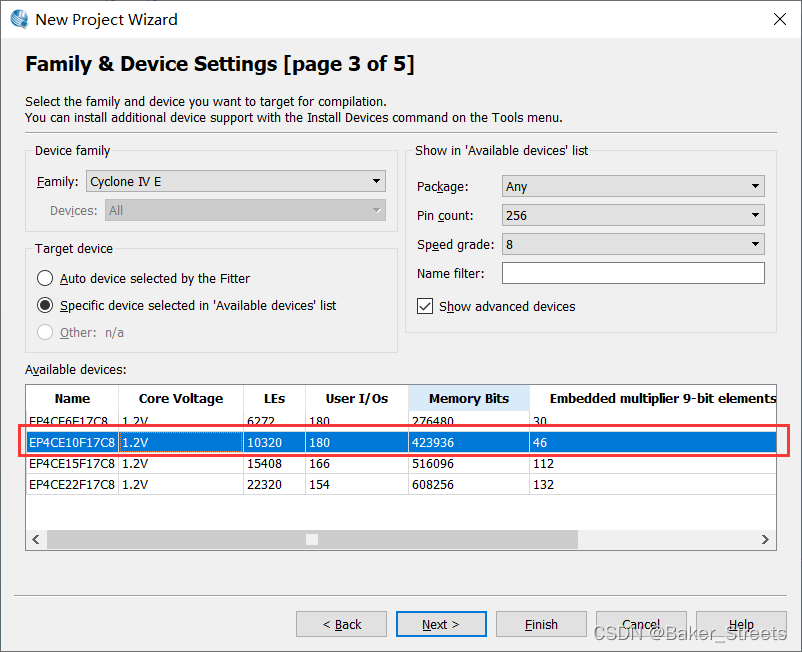

一、新建工程

详细可看QuartusⅡ 13.1 安装

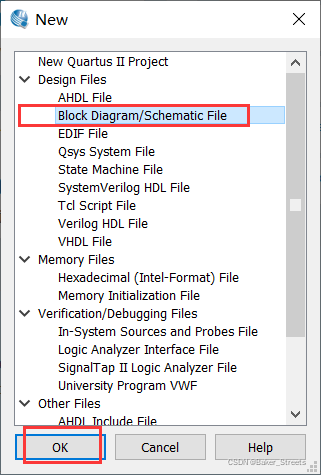

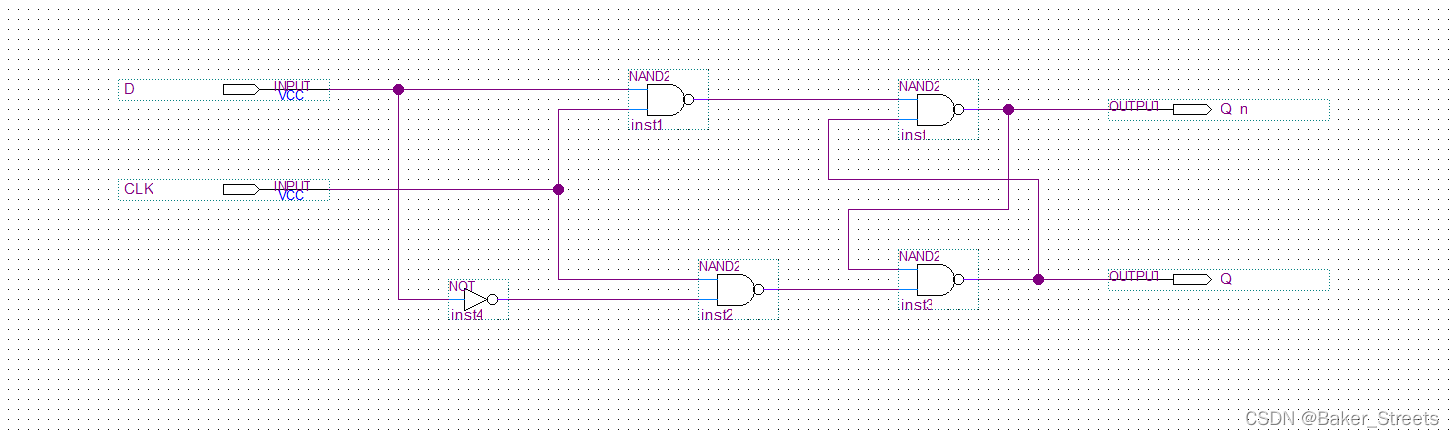

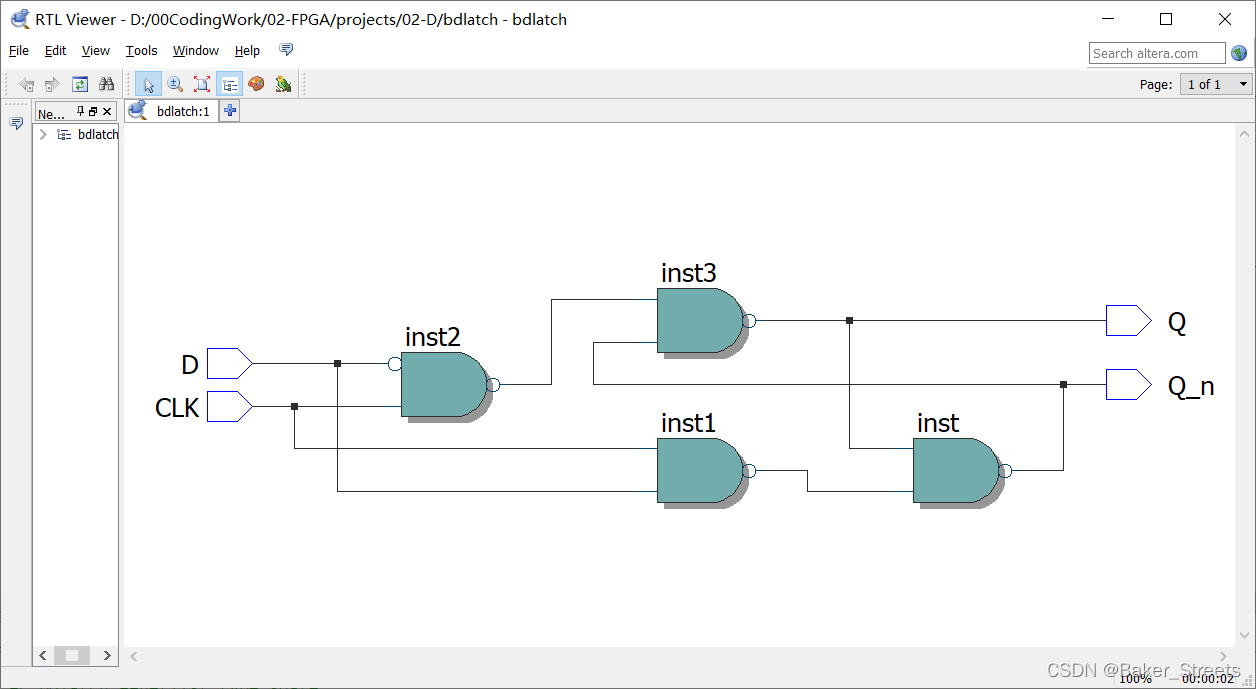

二、创建原理图文件

设计电路图:

需要

- 4个nand2 与非门

- 1个not 非门

- 2个input

- 2个output

保存:

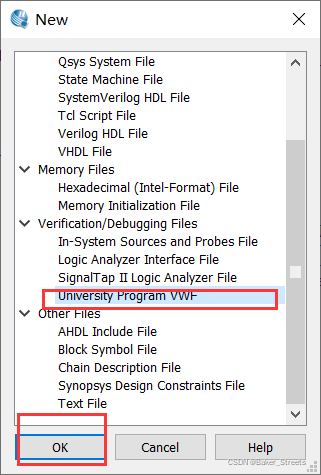

三、仿真

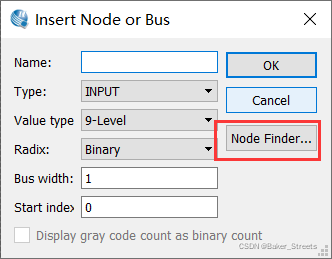

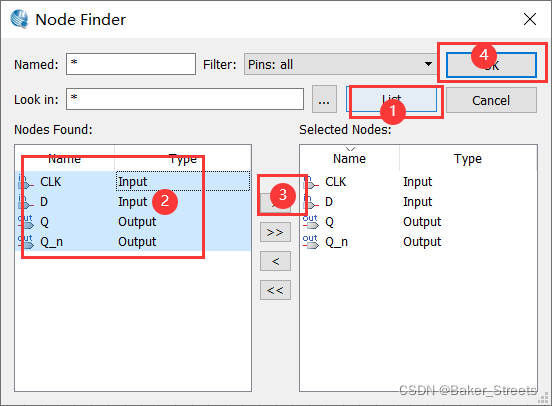

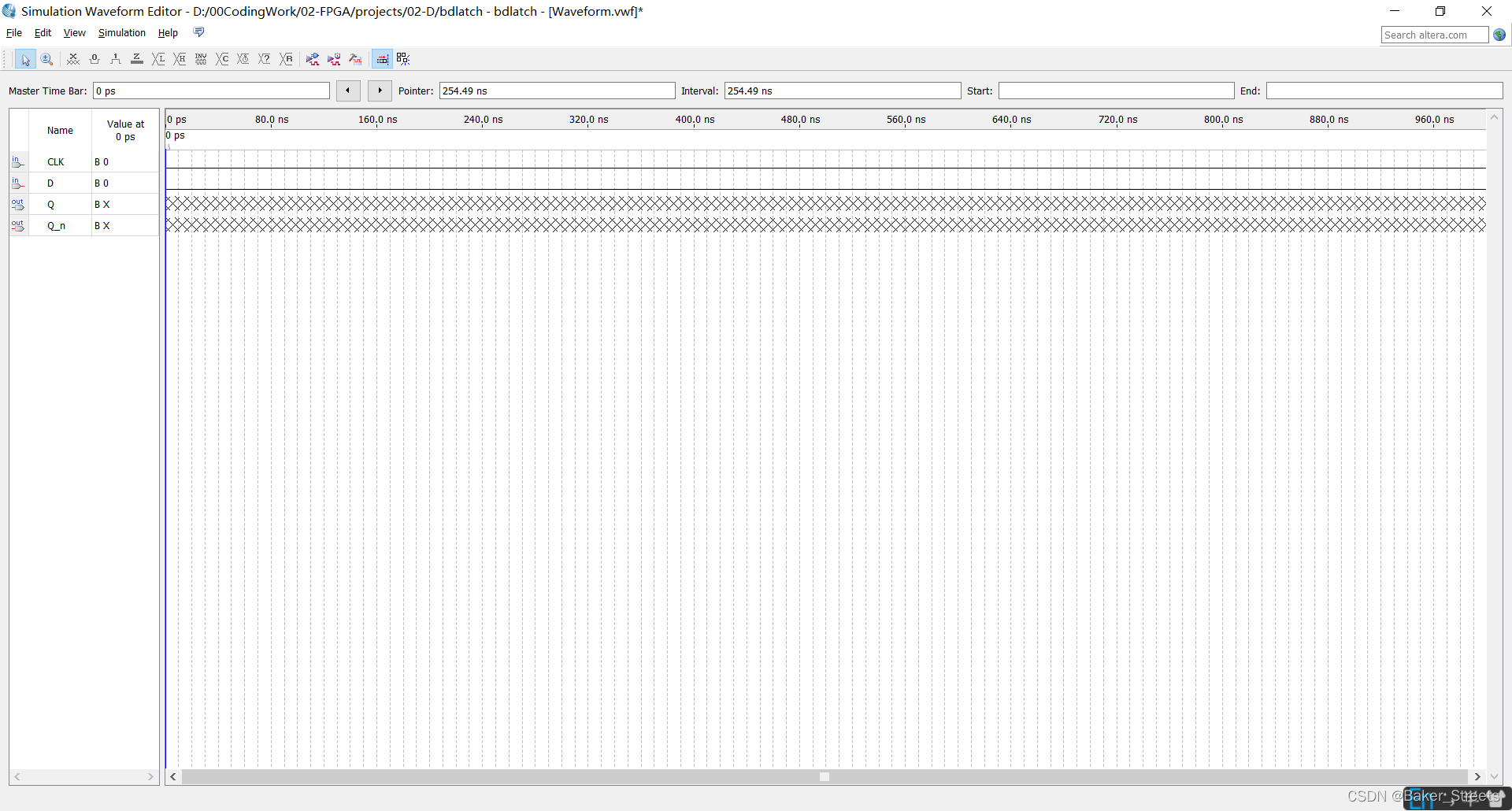

新建.vwf文件并加入管脚:

选择CLK,产生时钟信号:

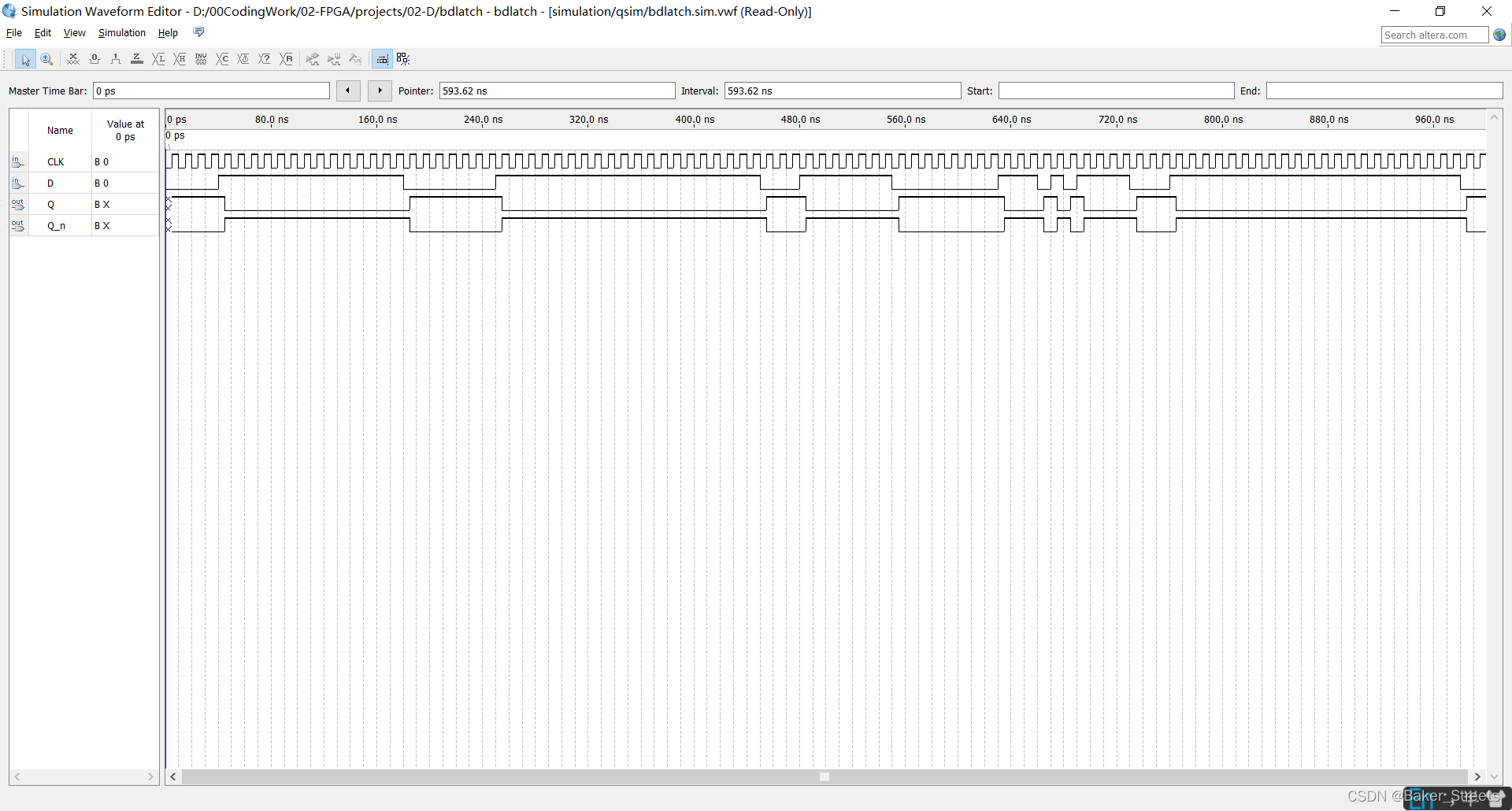

保存文件后,仿真:

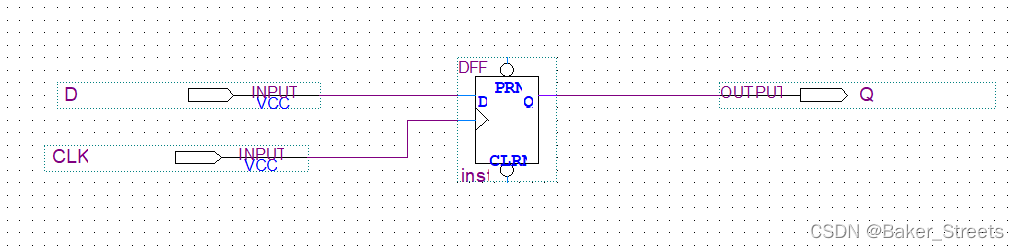

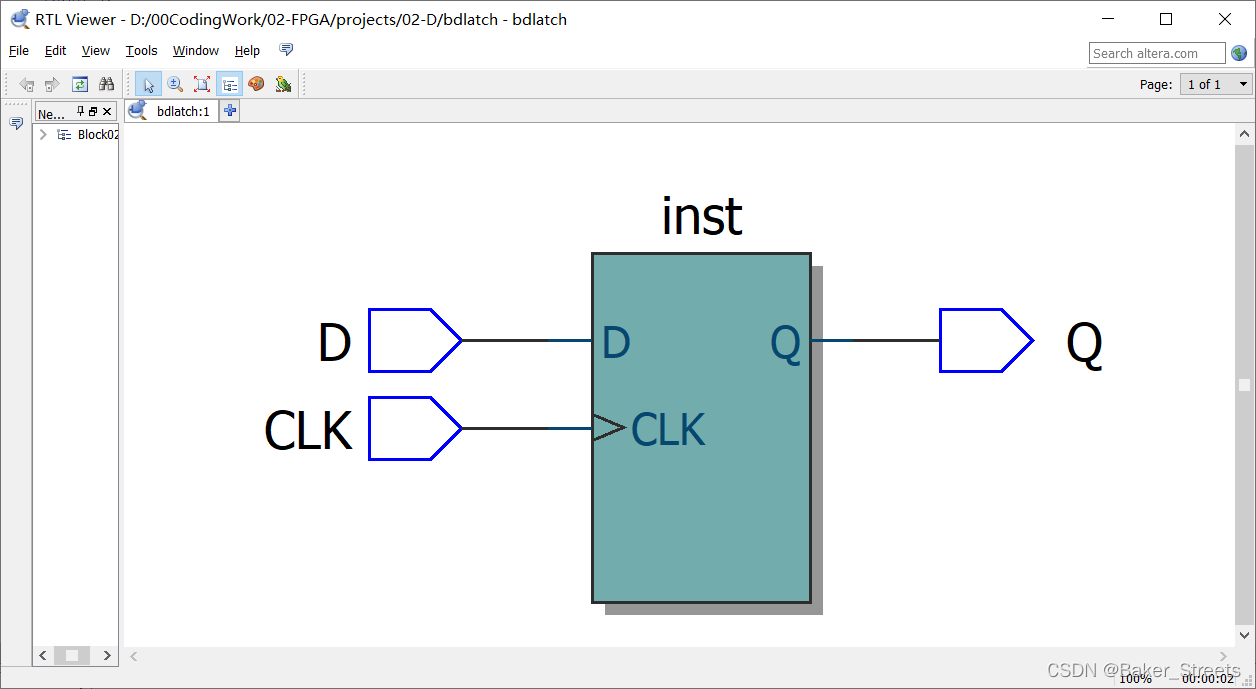

四、调用D触发器并仿真

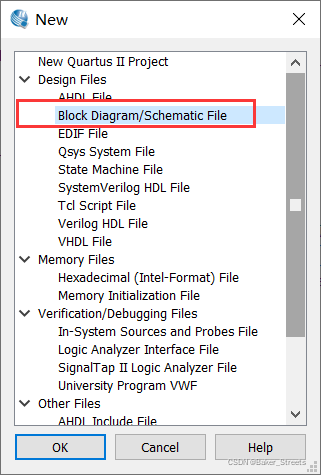

新建原理图文件:

直接使用D触发器:

添加两个input和一个output:

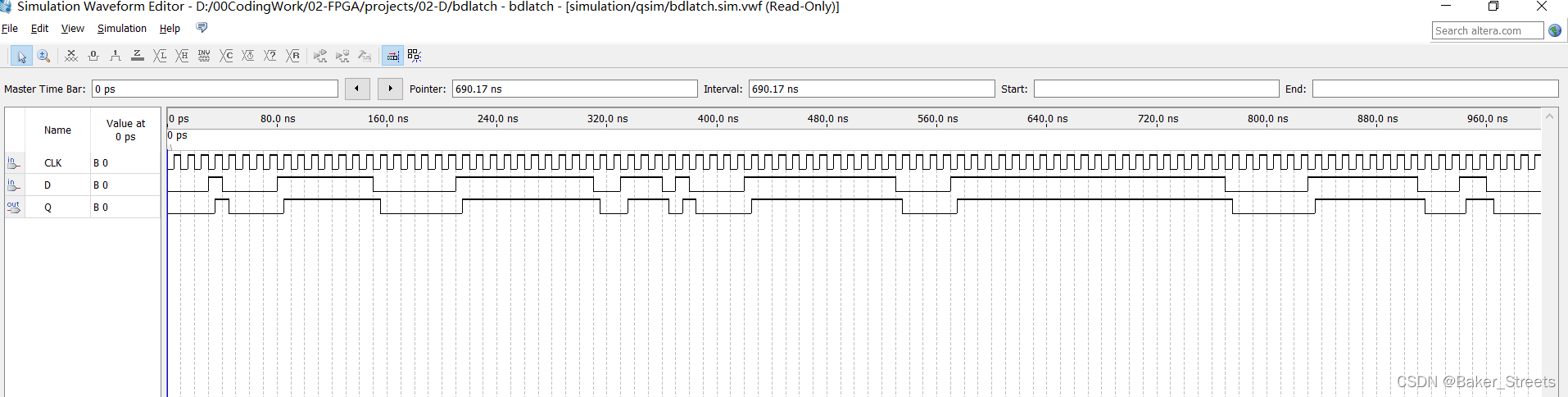

仿真:

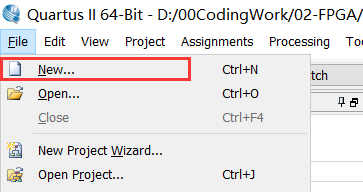

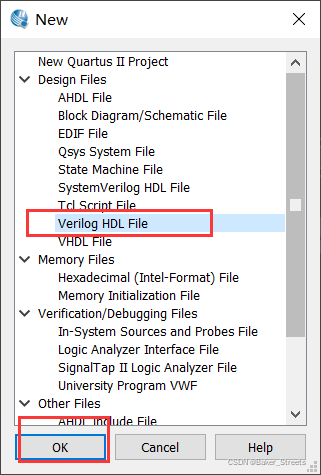

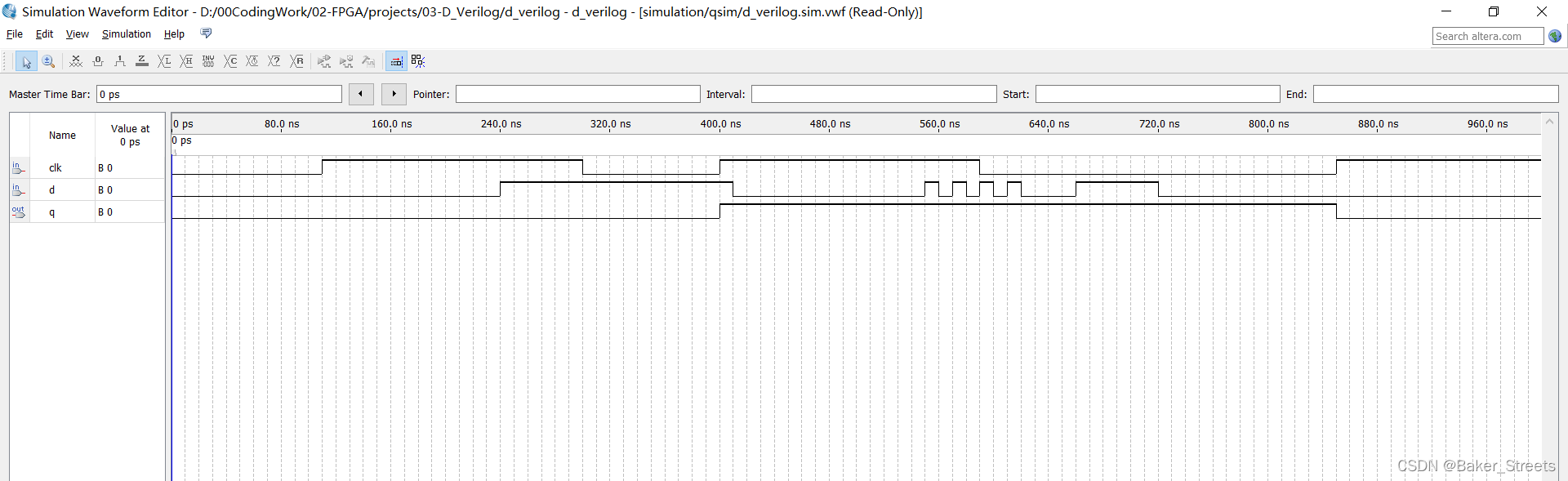

五、Verilog实现D触发器

New:

// dwave是文件名

module dwave(d,clk,q);

input d;

input clk;

output q;

reg q;

always @ (posedge clk)//我们用正的时钟沿做它的敏感信号

begin

q <= d;//上升沿有效的时候,把d捕获到q

end

endmodule

编译:

仿真:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?