Quartus II三种方式实现D触发器及时序仿真

一、准备工作

(一)软件下载

本实验需要用到两个软件:Quartus II和Modelsim SE,安装这里不做过多的介绍,具体请参照以下教程

Quartus II 13.1的安装及使用

Modelsim SE安装与介绍

- Quartus II 是Altera公司的综合性CPLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware 支持Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程

- modelsim是Mentor公司开发的优秀的HDL语言仿真软件。它能提供友好的仿真环境,采用单内核支持VHDL和Verilog混合仿真的仿真器。它采用直接优化的编译技术、Tcl/Tk技术和单一内核仿真技术,编译仿真速度快且编译的代码与平台无关。

(二)D触发器原理

1.简介

D触发器中的D是英文Delay的缩写,可见D触发器是一种延时电路D触发器中的D是英文Delay的缩写,可见D触发器是一种延时电路

2.D触发器的基本结构与信号输入输出关系

3.状态转移真值表以及状态转移图

特征方程 Qn+1=D

二、实验要求

- 在 Quartus-II 中自己用门电路设计一个D触发器,并进行仿真,时序波形验证;

- 在 Quartus-II 中直接调用一个D触发器电路,进行仿真,时序波形验证,与1做比较;

- 在 Quartus-II用Verilog语言写一个D触发器,进行仿真验证,与2做比较;

三、设计D触发器并仿真

(一)创建工程

1.File->New Project Wizard...

2.点击Next

3.设置工程的存储位置和项目名称

4.选择Next

5.选择目标芯片:cyclone IV E系列的EP4CE115F29C7

6.EDA Tool Setting设置,直接Next

7.点击finish

之后界面上会出现顶层文件名和项目名:

(二)创建原理图

1file->new

2.Design Files->Block Diagram/Schematic File ->OK

3.点击按纽 Symbol Tool或直接双击原理图空白处

4.从Symbol窗中选择需要的符号,或者直接在name文本框中键入元件名

- 个 nand2 与非门、1 个 not 非门、两个输入管脚和两个输出管脚

- 保存

File->Save As...

(三)编译

1.点击图标进行编译,若无错误则可进行下一步,若有错进行原理图修改

2.查看硬件电路图,Tools→Netlist Viewers→RTL Viewer

如图

(四)仿真波形图

1.新建波形文件file→new→university program VWF,选择后点击OK

2.点击空白处,选择insert node or bus→node finder

3.点击List,左面出现则触发器中所有的输入输出引脚。再在该界面上点击>>,则把左边所有的端口都选择到右边,点击两次OK,进入波形,如图

4.编辑输入CLK,产生时钟信号

5.输入D设置几个低电平和高电平

6.保存文件File→Save

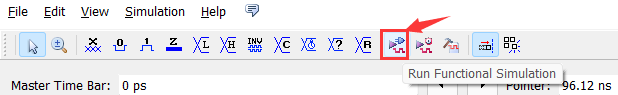

7.点击功能仿真编译按钮

报错

解决办法:

(1)点击Tools→launch Simulation Library Complier

(2)配置相关设置

注意Output Directory一定要选择到

simulation\qsim目录底下,不然还会报错

(3)出现以下提示就说明可以了

最终结果如下:

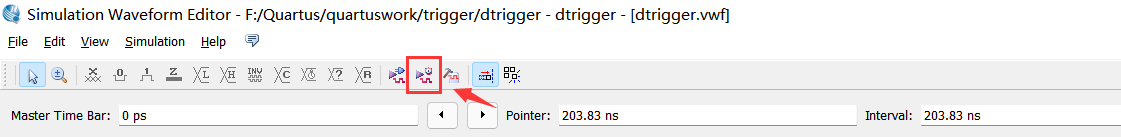

8.点击时序仿真按钮

结果如下

四、调用D触发器并仿真

(一)新建工程

(二)新建原理图

1.直接调用D触发器,输入元件名dff查找

2.添加两个输入一个输出管脚,原理图如下

(三)编译

1.保存

2.编译

3.查看硬件原理图

(四)仿真波形图

1.功能仿真波形图

2.时序仿真波形图

五、用Verilog语言实现D触发器

(一)创建工程

(二)创建Verilog HDL文件

1.File->New->Verilog HDL File

2.编写代码

module dtrigger(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)//我们用正的时钟沿做它的敏感信号

begin

Q <= D;//上升沿有效的时候,把d捕获到q

end

endmodule

3.保存文件

(三)编译

1.编译

2.查看硬件原理图

(四)波形仿真

1.Quartus II仿真

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-fjuoI0aN-1647324468301)(C:\Users\86199\AppData\Roaming\Typora\typora-user-images\image-20220315011159396.png)]](https://img-blog.csdnimg.cn/45ed0fd30741489ca3152aa2e855cb79.png?x-oss-process=image/watermark,type_d3F5LXplbmhlaQ,shadow_50,text_Q1NETiBA5LiA5Y-q54m556uL54us6KGM55qE54yqCu-4jw==,size_20,color_FFFFFF,t_70,g_se,x_16)

2.ModeSim仿真

(1)在当前目录下,新建一个文件夹modework

(2)点击Flie->Change Directory,选择modework文件夹

(3)创建新项目,File->New ->Project…

(4)项目命名选择储存位置,点击OK

(5)添加现有文件Add Existing File

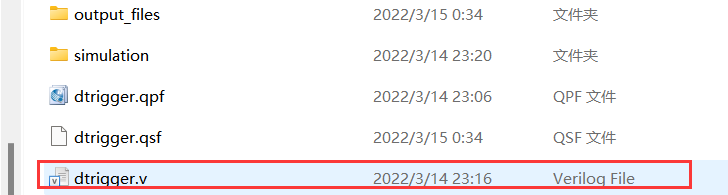

找到刚刚的dtrigger.v文件,文件类型选择Verilog,再点击OK

(6)再创建一个文件,Create New File

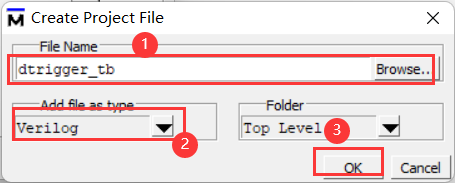

(7)命名,文件类型选择Verilog,再点击OK,关闭添加文件的窗口

(8)双击dtrigger_tb.v文件,添加代码

//测试代码

`timescale 1ns / 1ns

module dtrigger_tb;

reg CLK,D;

wire Q;

dtrigger u1(.D(D),.CLK(CLK),.Q(Q));

initial

begin

CLK = 1;

D <= 0;

forever

begin

#60 D <= 1;//人为生成毛刺

#22 D <= 0;

#2 D <= 1;

#2 D <= 0;

#16 D <= 0;//维持16ns的低电平,然后让它做周期性的循环

end

end

always #20 CLK <= ~CLK;//半周期为20ns,全周期为40ns的一个信号

endmodule

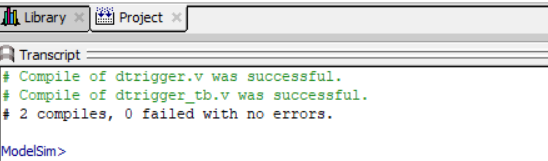

(9)保存编译

(10)点击Simulate->Start Simulate...

找到dtrigger_tb.v,取消勾选,点击OK

(11)右键点击dtrigger_tb.v,选择Add Wave

(12)设置运行时长,点击运行

六、总结

本次实学到了三种方式,自己设计D触发器可以更加深入的了解D触发器的内部元件构成,需要设计门电路;调用D触发器比较简单快捷;而用Verilog语言写D触发器比较灵活,可以通过编程仿真实现硬件原理,省去了画图的步骤,但是Verilog语言语法要求比较严格,大小写区分明显。通过三种方式实现D触发器,对Quartus II 和ModeSim两个软件的仿真实现过程更加熟悉,对D触发器的功能原理进一步了解。

七、参考资料

Quartus II搜狗百科

modelsim搜狗百科

D触发器工作原理是什么?

D触发器是什么,D触发器的基本结构与信号输入输出关系

2542

2542

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?