项目要求:

待检测数据“1”由外部输入,并用LED灯显示;

待检测串行数据长度为256位,由ROM输出;

一组数据检测完毕后,指示信号DONE为1;

“1”的个数由数码管显示;

设计时需给出仿真结果。

设计结果下载到FPGA上实现功能的硬件验证。

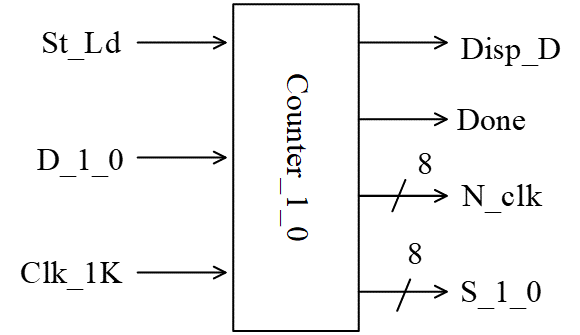

Clk_1k | 频率为1kHz的时钟信号,上升沿有效 |

D_1_0 | 待统计信号,手动输入。 |

St_Ld | 开始统计同步置数/清零信号,手动输入脉冲信号。在高电平将D_1_0置入电路,并输出,同时清零S_1_0,N_clk和Done。在St_Ld由高变低时,电路开始统计工作。 |

Disp_D | 显示置入的D_1_0值。 |

S_1_0 | 一帧256位数据中,与D_1_0相等的二进制数的个数,8位宽。 |

N_clk | 统计256位数据实际需要的clk的周期数,8位宽。 |

Done | 一帧统计结束信号,当Done=1时,表示统计结束。 |

电路设计要求:

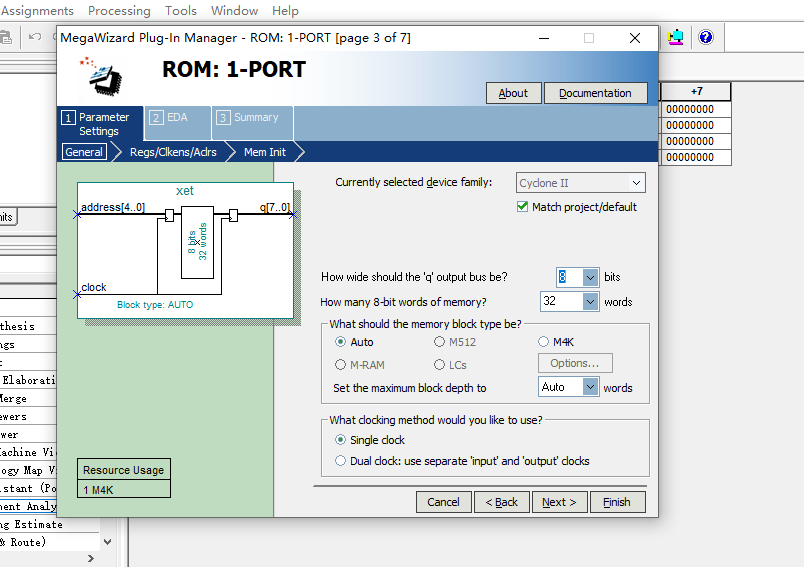

待检测的256位数据可以任意产生,事先存储在8位宽,深度为32的ROM中;

将ROM中并行读出的8位数据转换为串行输出数据,然后检测串行数据中与D_1_0一样的二进制数个数;不允许先一次性转换成256位的串行数据然后再监测0或1个数的设计。

在St_Ld信号为高电平时,实现D_1_0的同步载入和S_1_0的同步清零,同时必须在St_Ld由高变低后,电路才开始统计工作,直达Done=1为止。

改变D_1_0的值实现0的个数统计。且0的个数加1的个数一定要等于256.

需要解决的问题:(1)如何实行并串转化,并实现数据的连续输出?(2)控制电路允许统计的信号该如何表示;

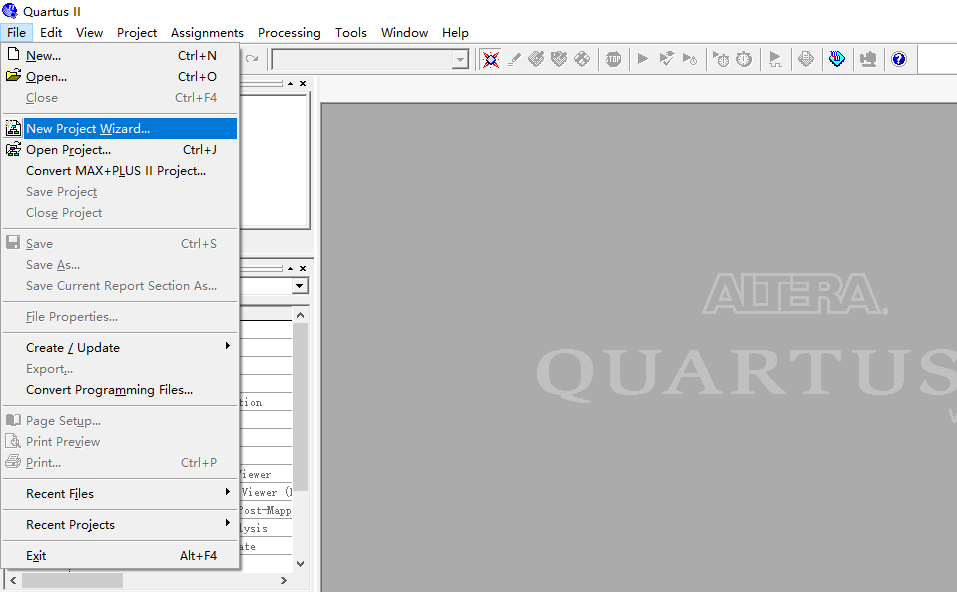

创建项目步骤:

1.创建项目 File->New Project Wizard....

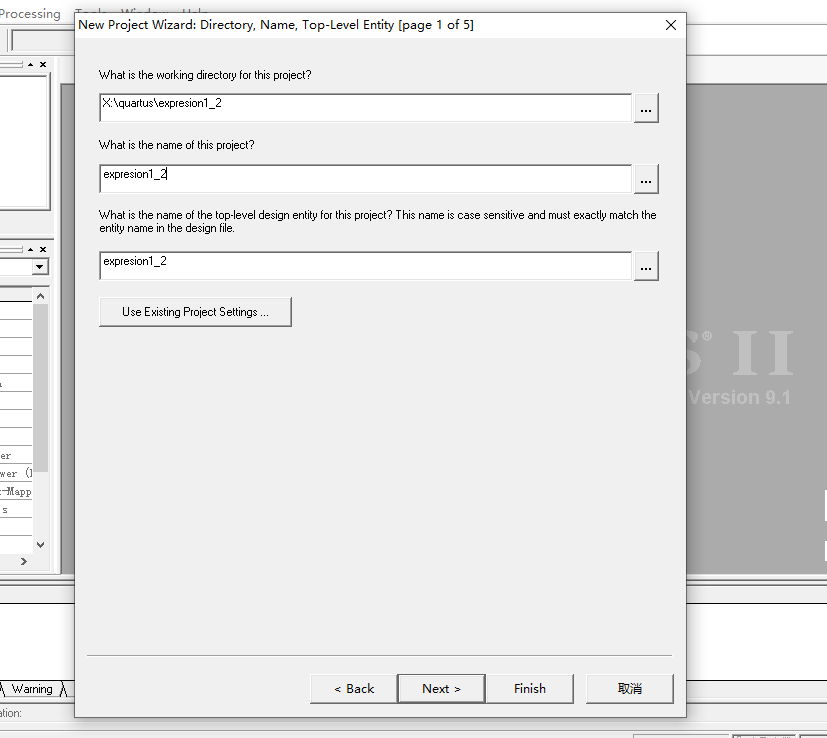

2.设置项目名称

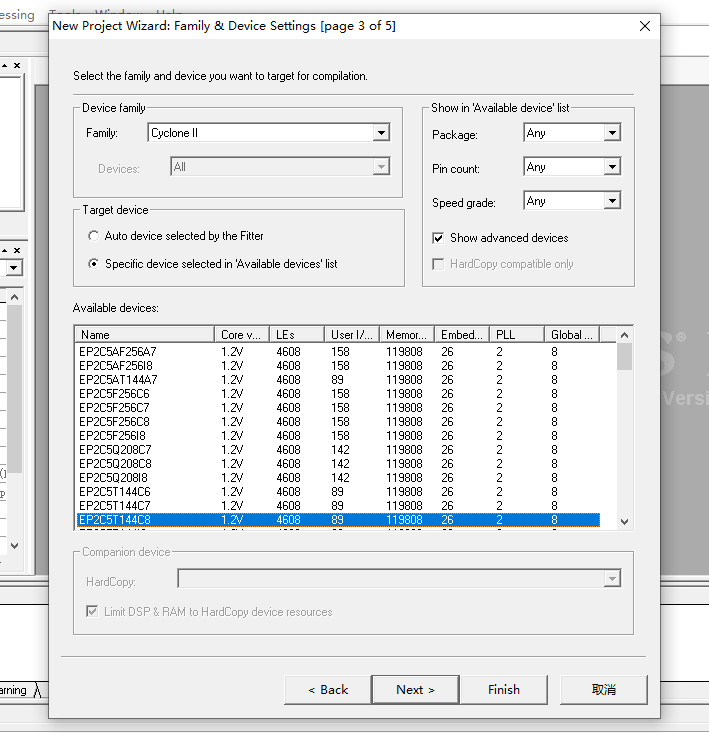

3.选择电路板信号

4.其他步骤直接点击next就项目好了。

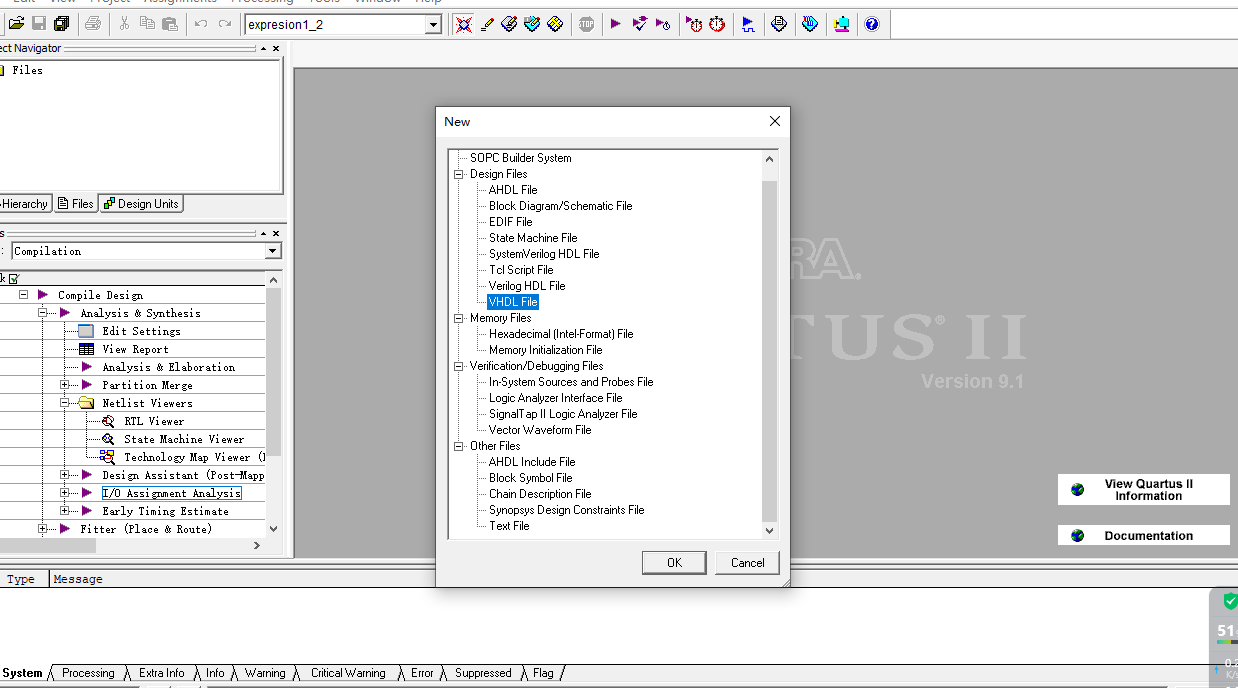

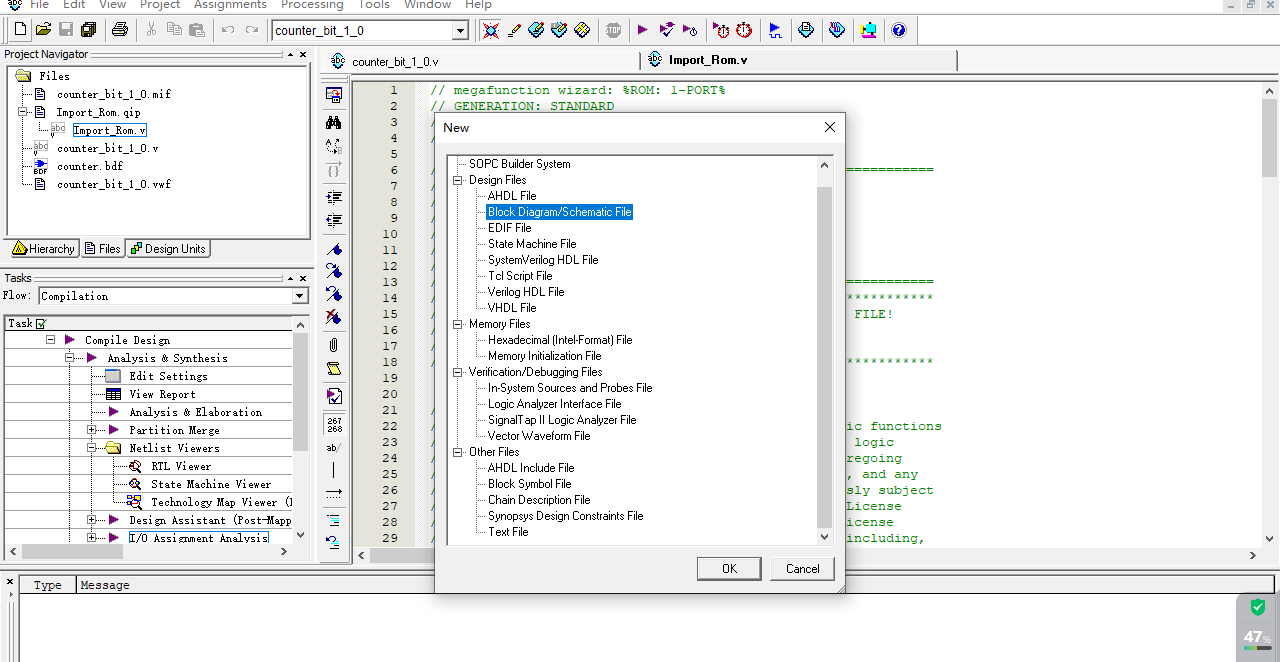

开始创建Verilog hdl文件

new -> VHDL file ->OK 就好了

写入程序代码:

参考代码如下:

module counter_bit_1_0(shift_date,clk,st,d,rom_addr,N_clk,S_1_0,Done,Disp_d);

input [7:0]shift_date;

input clk,st,d;

output reg [4:0]rom_addr = 0;

output reg [7:0]N_clk;

output reg [7:0]S_1_0;

output reg Done;

output reg Disp_d;

reg [7:0]reg_date;

always@(posedge clk)begin

if(st)begin

N_clk <= 0;

Done <= 0;

end

else if(N_clk == 255)

Done <= 1;

else if(Done)

N_clk <= N_clk;

else

N_clk <= N_clk + 1;

end

always@(posedge clk)begin

if(st)begin

S_1_0 <= 0;

Disp_d <= d;

end

else if(Done)

S_1_0 <= S_1_0;

else if(reg_date[0] == d)

S_1_0 <= S_1_0 + 1;

end

always@(posedge clk)begin

if(N_clk % 8 == 6)

rom_addr <= rom_addr + 1;

else

rom_addr <= rom_addr;

end

always@(posedge clk)begin

if(st)

reg_date <= shift_date;

else if(N_clk % 8 == 7)

reg_date <= shift_date;

else

reg_date <= reg_date>>1;

end

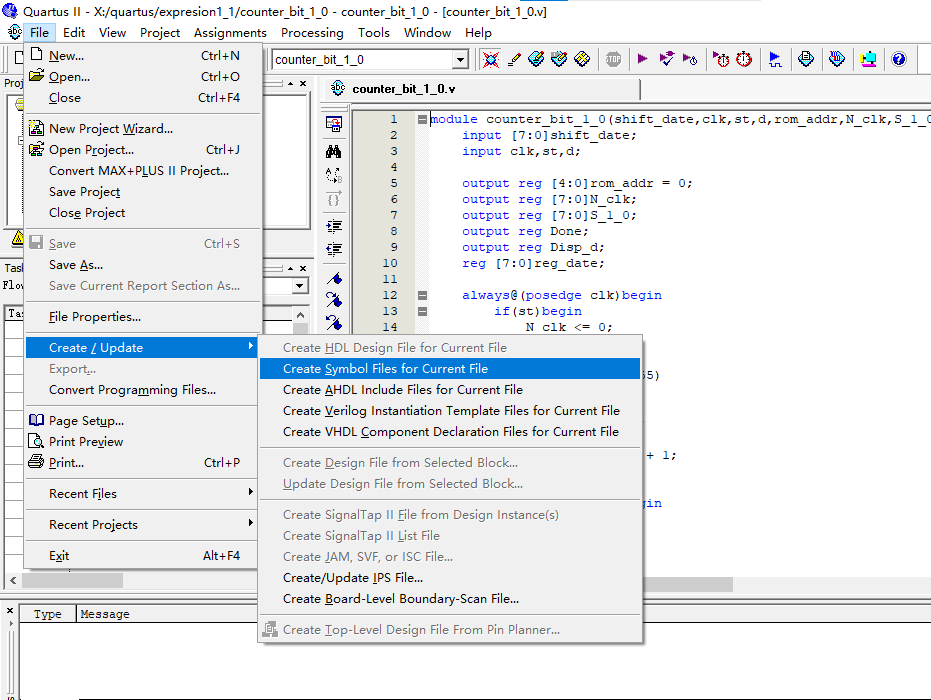

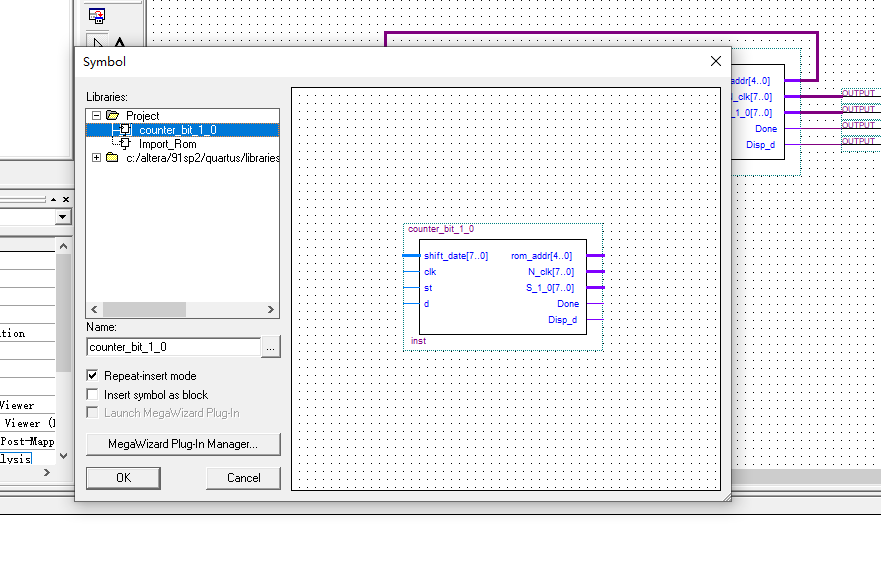

endmodule生成Symbol模块

以上步骤就核心功能实现了。

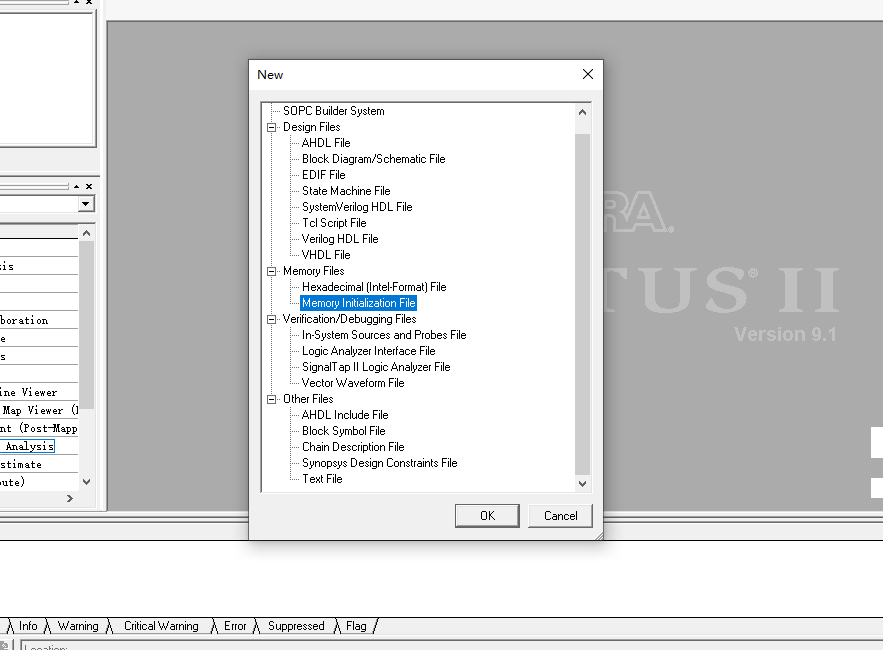

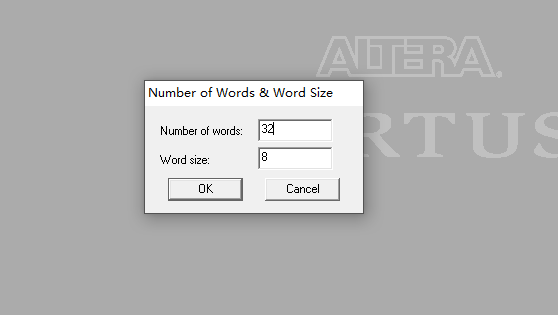

创建从ROM读取数据的mif后缀文件

new->Memory Initialization File

设置宽为8,深为32;OK就创建好了

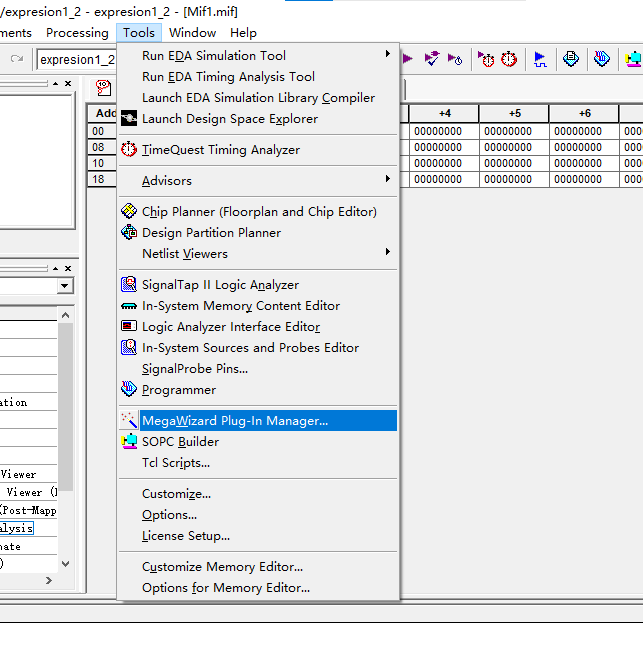

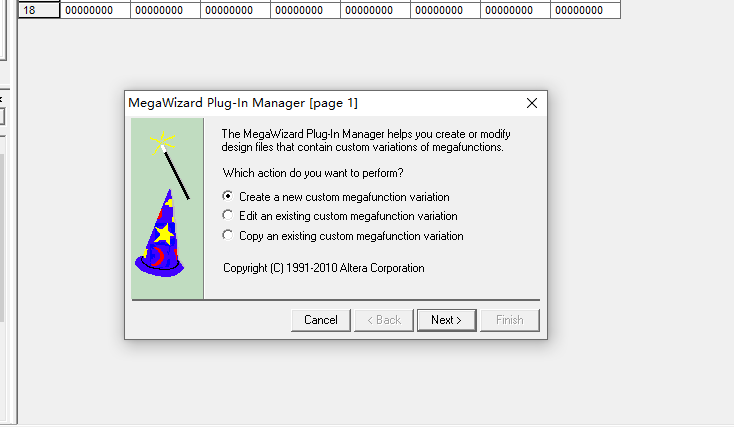

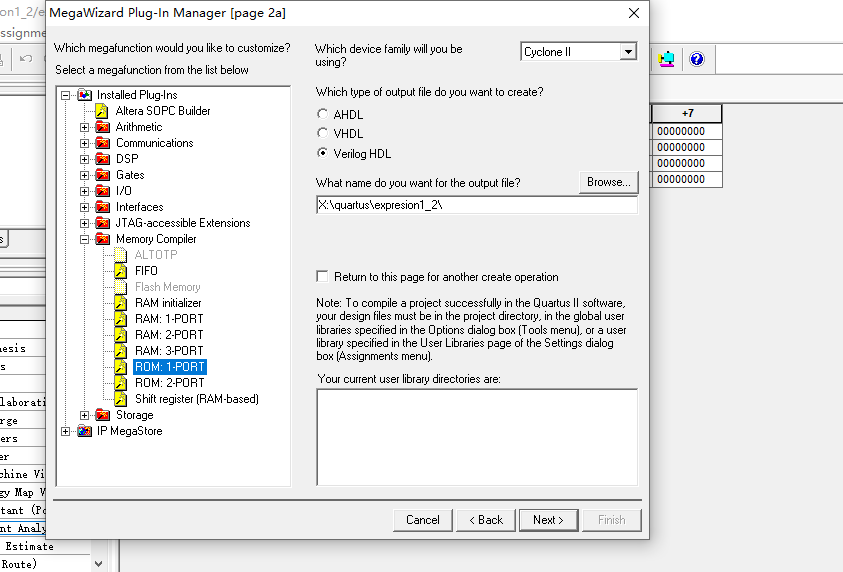

创建从ROM并行读取模块

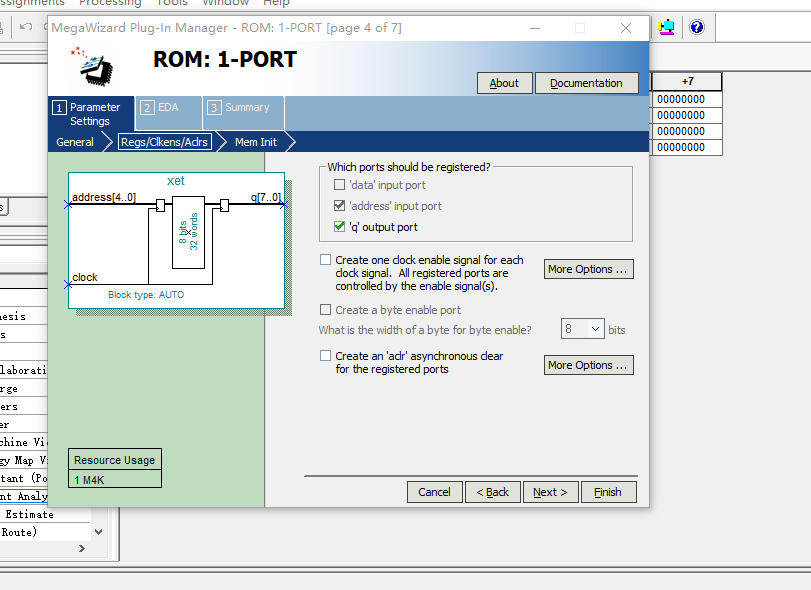

1.如下图

2.如下图

这步设计文件名

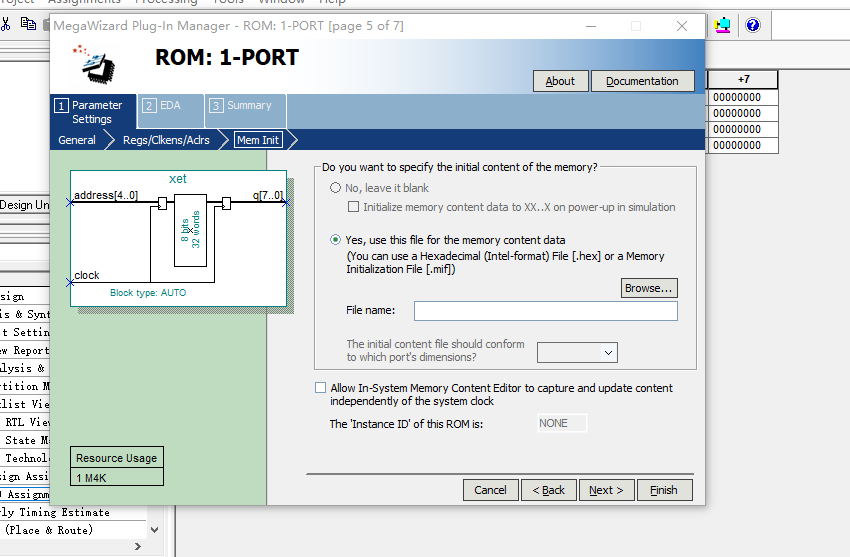

这里选择上一步创建的mif文件

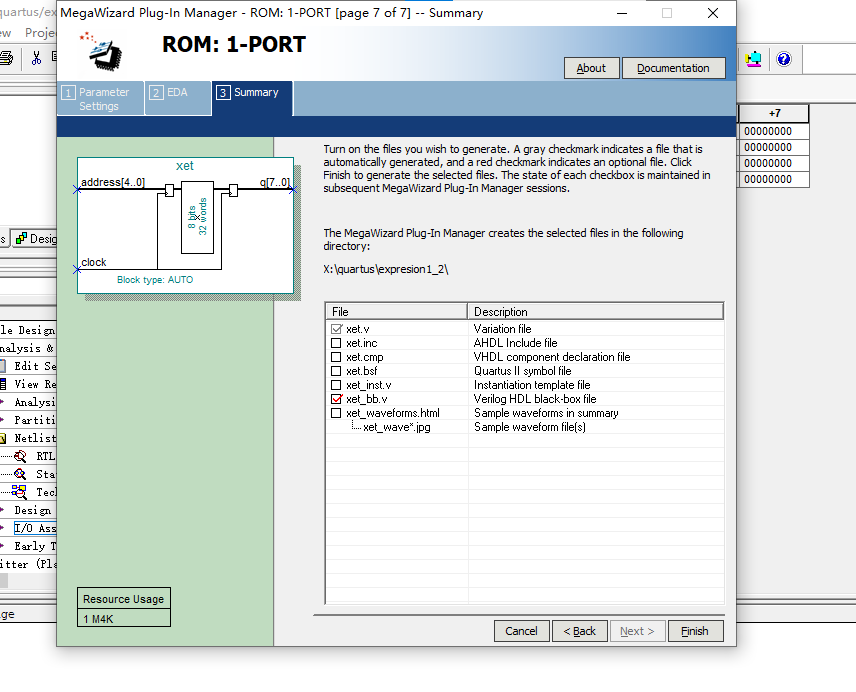

把这个文件转换为Symbol模块。

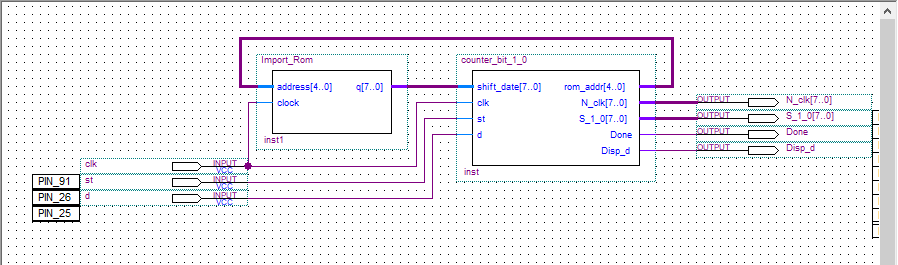

创建图形设计界面连接线路

1.创建

2.从Symbol Tool里找到刚才我们创建的模块

3.两个都导入以后连接引脚

以上步骤就完成了所有功能。

tips:

希望上述方法能够帮到您。

以上创建文件过程有些步骤省略了,有什么不懂及其他问题欢迎评论留言或私信我,可能不能及时回复,但我有时间都会回答的。

其实我也是菜鸟一只,有问题提出来一起进步。

293

293

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?