1.AXI总线介绍

AXI全称Advanced Extensible Interface,是Xilinx从6系列的FPGA开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。AXI协议在Xilinx的ZYNQ系列芯片中继续使用,协议版本是AXI4。

ZYNQ为Xilinx推出的首款将高性能ARM Cortex-A9系列处理器与高性能 FPGA逻辑资源整合在单芯片上的产品。Xilinx正是通过AXI总线技术在ZYNQ系列芯片上实现了ARM处理器和FPGA之间的高速通信和数据交互,发挥了ARM处理器和FPGA的性能优势。

在ZYNQ中,支持AXI-Lite,AXI4和AXI-Stream三种总线,通过下表我们可以看到这三种AXI接口的特性。

| 接口协议 | 特性 | 应用场合 |

| AXI4-Lite | 地址/单数据传输 | 低速外设或控制 |

| AXI4 | 地址/突发数据传输 | 带地址数据的批量传输 |

| AXI4-Stream | 仅传输数据、突发传输 | 数据流和媒体流传输 |

-

AXI4-Lite:

具有轻量级,结构简单的特点,适合小批量数据、简单控制场合。不支持批量传输,读写时一次只能读写一个字(32bit)。主要用于访问一些低速外设的控制和数据传输。

-

AXI4:

接口和AXI-Lite差不多,增加了批量传输功能,可以连续对一片地址进行一次性数据读写。也就是说具有数据读写的burst(突发)功能。

AXI4-Lite和AXI4两种协议均采用内存映射控制方式,即FPAG将用户自定义模块编入某一地址进行访问,读写时就像在读写自己的片内RAM,编程也很方便,开发难度较低。代价就是资源占用相对较多,需要额外的读地址线、写地址线、读数据线、写数据线、写应答线等配套信号线。

-

AXI4-Stream:

这是一种连续数据流接口,不需要地址线(与FIFO类似,一直读或一直写就行)。对于这类接口,FPGA不能通过上面的内存映射方式来控制模块,必须有一个接口转换模块,例如AXI-DMA模块来实现内存映射(AXI4-Lite/AXI4)到流式接口(AXI4-Stream)的转换。

AXI-Stream适用的场合有很多:视频流处理;通信协议转换;数字信号处理;无线通信等。其本质都是针对数值流构建的数据通路,从信源(例如ARM内存、DMA、无线接收前端等)到信宿(例如HDMI显示器、高速ADC、音频输出等)构建起连续的数据流。这种接口适合做实时信号处理。

2.AXI协议通道介绍

AXI4和AXI4-Lite接口包含5个不同的通道,分别是:

(1)读地址通道(Read Address Channel);

(2)写地址通道(Write Address Channel);

(3)读数据通道(Read Data Channel);

(4)写数据通道(Write Data Channel);

(5)写响应通道(Write Response Channel);

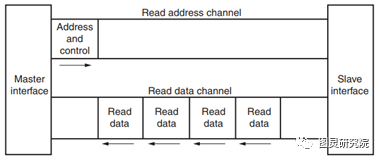

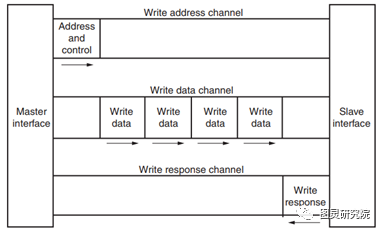

其中每个通道都是一个独立的AXI握手协议。下面两个图分别显示了读和写的模型:

AXI读数据通道

AXI写数据通道

3.ZYNQ芯片内部的AXI总线

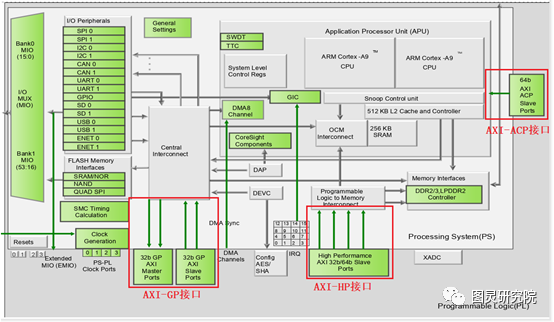

ZYNQ芯片内部用硬件实现了AXI总线协议,包括9个物理接口,分别为AXI-GP0~AXIGP3,AXI-HP0~AXI-HP3,AXI-ACP接口。

AXI_ACP接口,是ARM多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理DMA之类的不带缓存的AXI外设,PS端是Slave接口。

AXI_HP接口,是高性能/带宽的AXI3.0标准的接口,总共有四个,PL模块作为主设备连接。主要用于PL访问PS上的存储器(DDR和On-Chip RAM)

AXI_GP接口,是通用的AXI接口,总共有四个,包括两个32位主设备接口和两个32位从设备接口。

可以看到,PS端(ARM端)只有两个AXI-GP是Master Port,即主机接口,其余7个接口都是Slave Port(从机接口)。

主机接口具有发起读写的权限,ARM可以利用两个AXI-GP主机接口主动访问PL端(FPGA端)逻辑。其实是PS端把PL端映射到某个地址,读写PL寄存器如同在PS端在读写自己的存储器。其余PS端的从机接口就属于被动接口,只能接受来自PL的读写操作。

另外这9个AXI接口性能也是不同的。GP接口是32位的低性能接口,理论带宽600MB/s,而HP和ACP接口为64位高性能接口,理论带宽1200MB/s。

有人会问,为什么高性能接口不做成主机接口呢?这样可以由ARM发起高速数据传输。答案是高性能接口根本不需要ARMCPU来负责数据搬移,真正的搬运主力是位于PL端中的DMA控制器。

4.常用AXI接口IP介绍

位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。

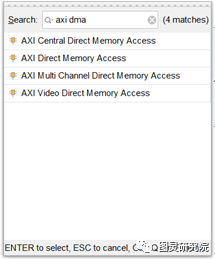

Xilinx在Vivado开发环境里提供现成AIX 接口IP,如AXI-DMA、AXI-GPIO、AXI-Dataover、AXI-Stream。使用时直接从Vivado的IP列表中添加即可实现相应的功能。下图为Vivado下的各种DMA IP:

下面为几个常用的AXI接口IP的功能介绍:

AXI-DMA:实现从PS内存到PL高速传输高速通道的转换。(AXI-HP<---->AXI-Stream)

AXI-Datamover:实现从PS内存到PL高速传输高速通道的转换,不过是完全由PL控制的,PS是完全被动的。(AXI-HP<---->AXI-Stream)

AXI-VDMA:实现从PS内存到PL高速传输高速通道的转换,是专门针对视频、图像等二维数据传输的。(AXI-HP<---->AXI-Stream)

AXI-CDMA:这个是由PL完成的将数据从内存的一个位置搬移到另一个位置,无需CPU来插手。

有时,用户需要开发自己定义的IP同PS进行通信,这时可以利用向导生成对应的IP。用户自定义IP核可以拥有AXI4-Lite、AXI4、AXI-Stream接口。

有了上面的这些官方IP和向导生成的自定义IP,用户其实不需要对AXI时序了解太多(除非确实遇到问题)。Xilinx已经将和AXI时序有关的细节都封装起来,用户只需要关注自己的逻辑实现即可。

5. 多个AXI接口互联交互

AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,需要加入一个AXI Interconnect模块,也就是AXI互联矩阵,作用是提供将一个或多个AXI主设备连接到一个或多个AXI从设备的一种交换机制(有点类似于交换机里面的交换矩阵)。

这个AXI Interconnect IP核最多可以同时支持连接16个主设备和16个从设备。如果需要更多的接口,可以级联多个AXI Interconnect IP。

AXI Interconnect基本连接模式有以下几种:

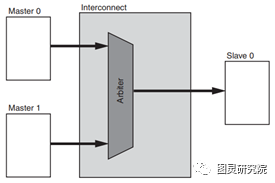

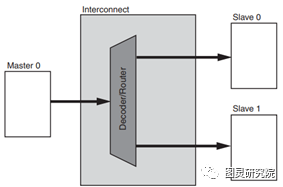

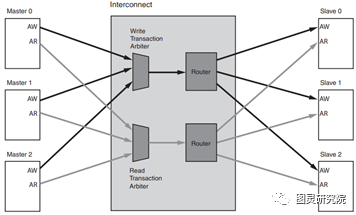

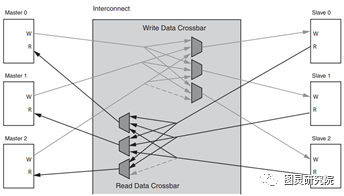

(1)多对一连接(N-to-1 Interconnect);

(2)1对多连接(1-to-N Interconnect);

(3) 多对多连接(N-to-M Interconnect Shared-Address Multiple-Data);

shared write and read address arbitrations

sparse crossbar write and read address pathways

ZYNQ内部的AXI接口设备就是通过互联矩阵的的方式互联起来的,既保证了传输数据的高效性,又保证了连接的灵活性。

2354

2354

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?