AXI总线 是ARM公司定义的一种总线结构,属于AMBA 协议的一部分。AMBA协议视乎很陌生,但是在MCU的开发中我们一定接触过AHB,APB总线。AHB和APB总线都是属于AMBA协议,AXI也是AMBA协议的一部分。AMBA是高级微处理器总线架构的缩写。

一.AXI总线概览

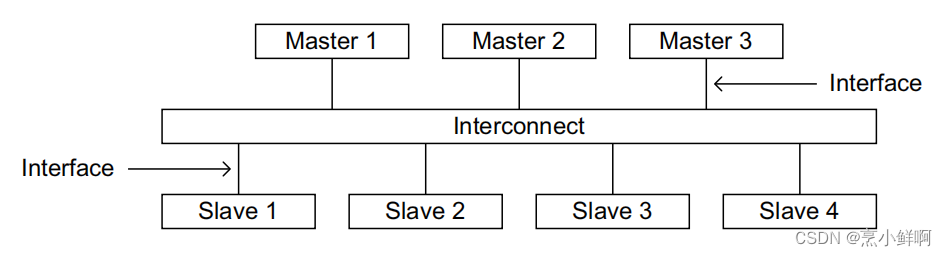

总线的本质是用于信息通用线路。AXI是分主机和从机的,它的连接方式如下所示

AXI其中的I指的是接口,Advanced eXtensible Interface。

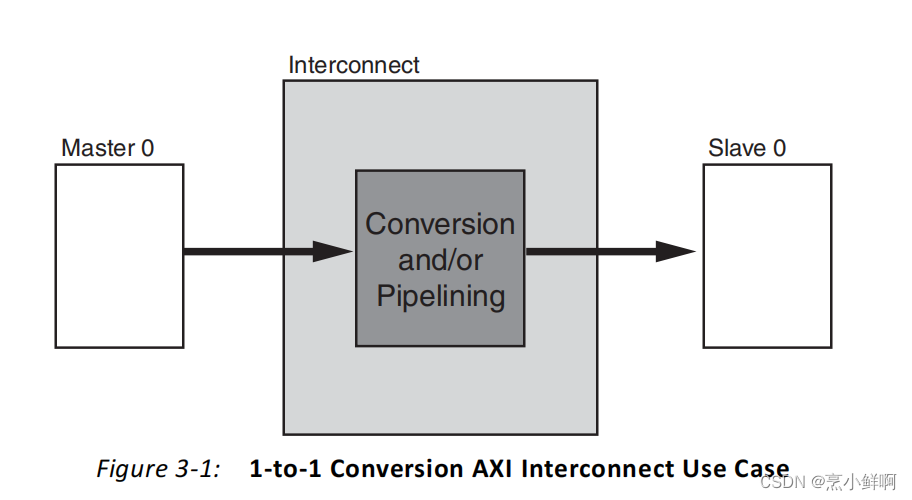

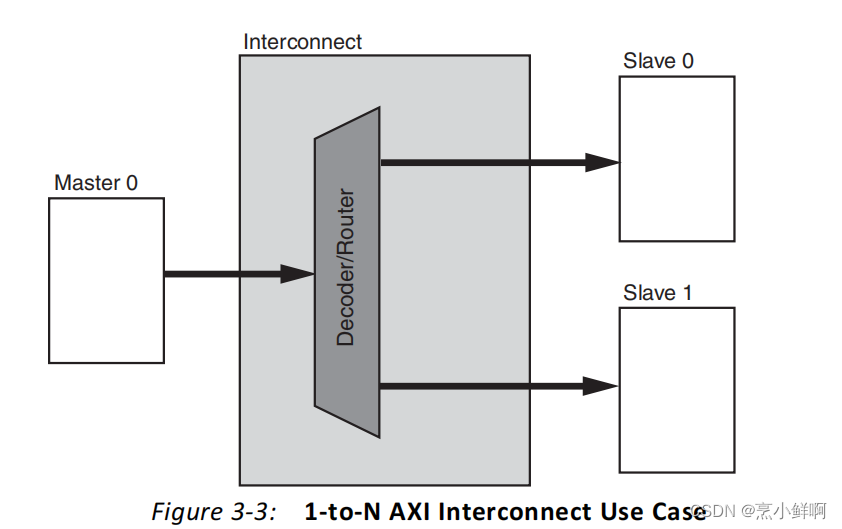

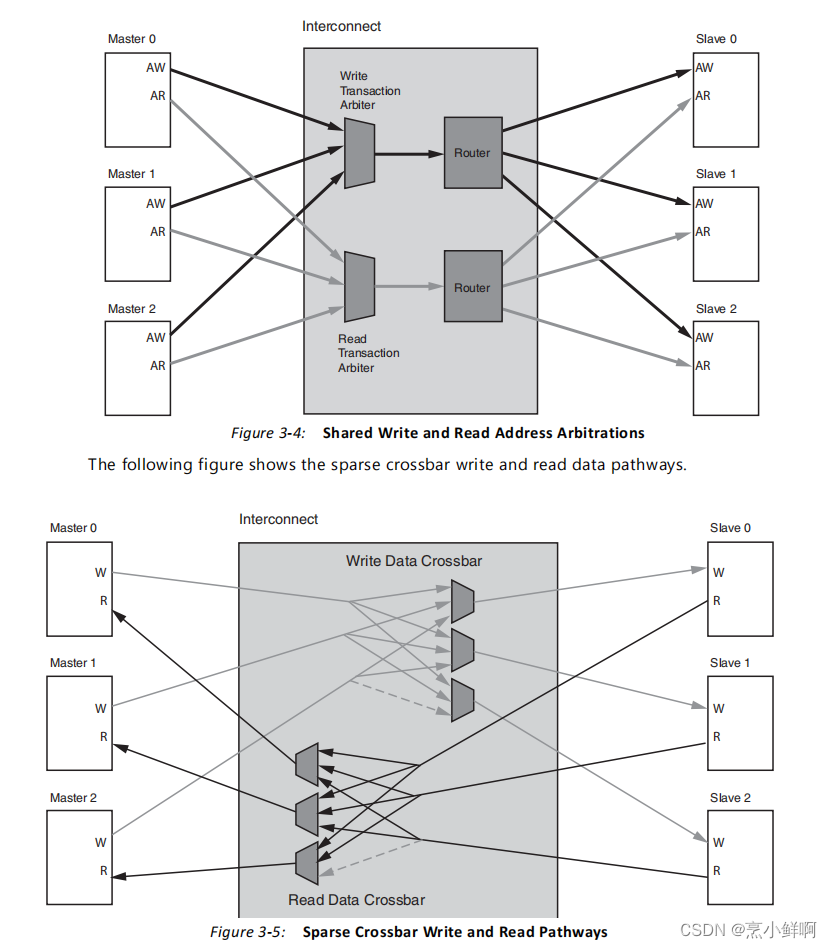

Interconnect 是连接各个AXI主从接口的互通。内部的详细构造非常复杂,有很多种结构,下图是ug1037的内容

AXI其中的I指的是接口,Advanced eXtensible Interface。eXtensible 说的是扩展,通过拓扑图可以看到扩展这个概念。

二.AXI总线的数据传输

AXI为高级可扩展总线结构协议,用于传输数据。数据的操作无非就是读写。

AXI的设计也是围绕读写进行。它做了一个有趣的设定,具有5个通道,通道是按照逻辑进行划分的。

1读通道

2写通道

3读地址通道

4写地址通道

5写回应通道

上面五个通道是逻辑上的概念,并不是说5条线缆。例如和读相关的一系列信号归为读通道。

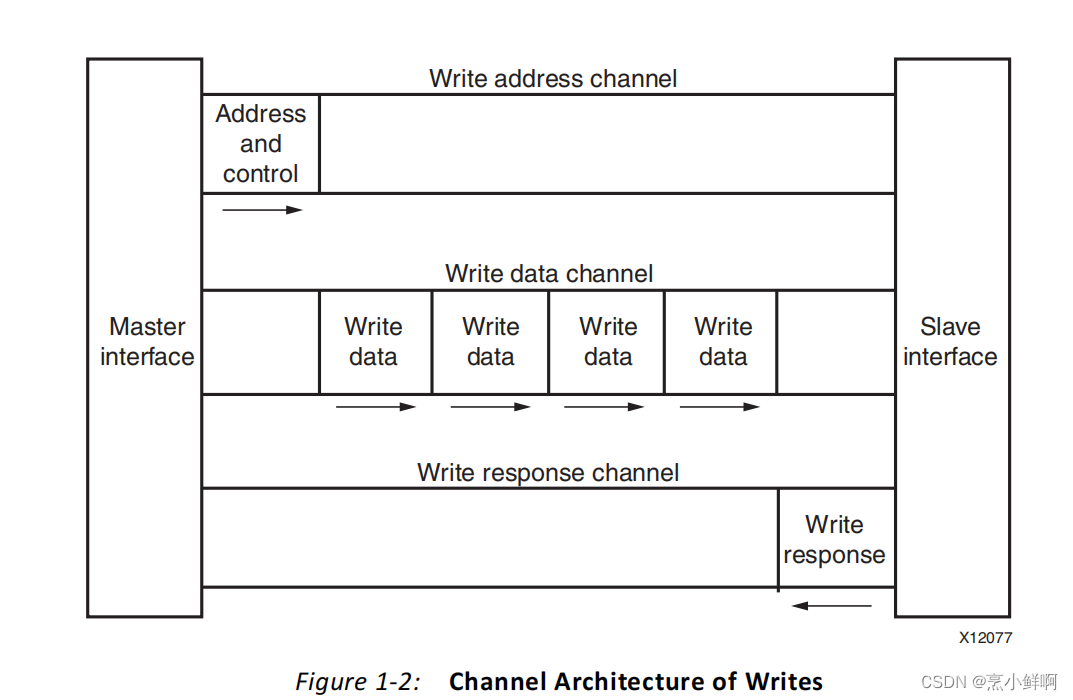

下图是写数据的示意图

Write address channel 是写地址通道,主设备需要把数据传输到的位置,位置信息就是地址。

Write data channel 就是数据本身

Write response channel 写数据的回应信息

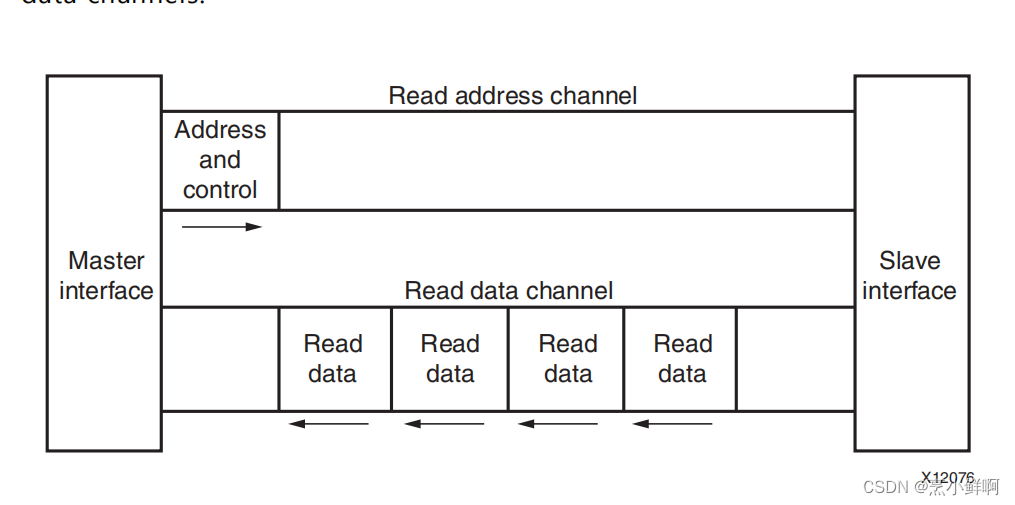

下图是读数据

三. AXI 传输的时序图

如果你去看ARM的IHI0022D的AXI协议介绍,可能花个大半天都是懵懵懂懂的。

对于有基础的大部分人,理解协议可以直接先上时序图。

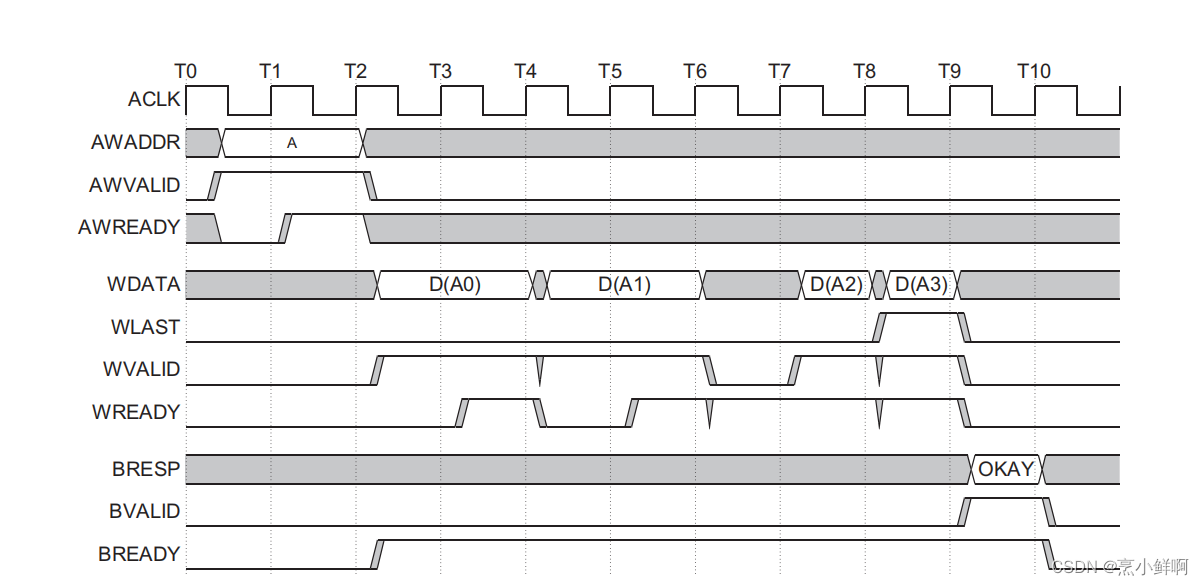

1.ACLK 是时钟信号,AWADDR 是写数据的地址信号,AWVALID 是主机地址通道的地址信号已经准备完毕,AWREADY指的是从机地址通道接收已经准备好了。当主从都准备好了,那么地址通道的数据传输就有效。这种机制在AXI中称为握手

2.写数据通道是W开头的信号,同样有握手信号WVALID和WREADY。两个信号都有效边上写数据通道的数据准备完毕,接受端也做号接收数据的准备。下个时刻开始输出传输。WLAST 表示最后一个数据。

3.同样可以看到握手信号,和BRESP。看懂1,2这里也是一样的。

可以看出来,5个通道都有握手机制。

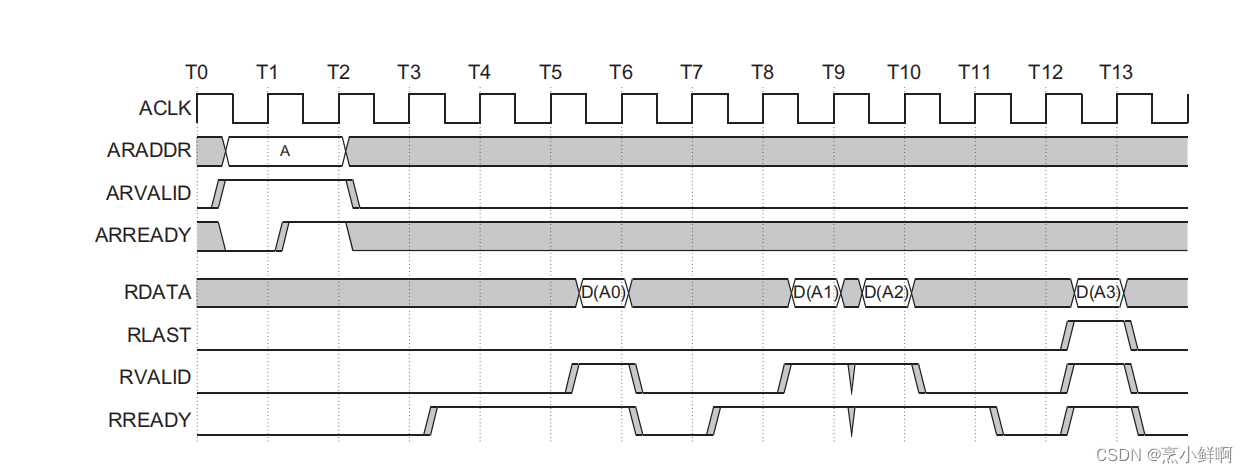

AXI读时序如下所示。逻辑和写是一样的。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?