描述

在data_en为高期间,data_in将保持不变,data_en为高至少保持3个B时钟周期。表明,当data_en为高时,可将数据进行同步。

本题中data_in端数据变化频率很低,相邻两个数据间的变化,至少间隔10个B时钟周期。

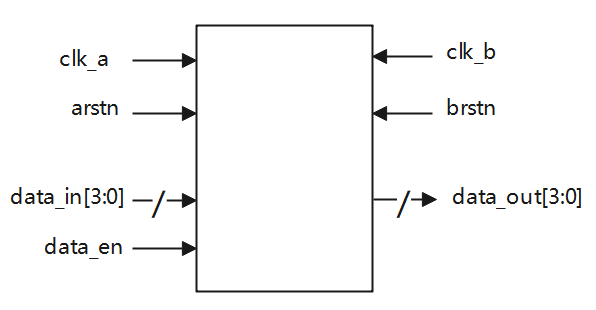

电路的接口如下图所示。端口说明如下表所示。

| 端口 | I/O | 描述 |

| clk_a | input | A时钟域时钟 |

| clk_b | input | B时钟域时钟 |

| arstn | input | A时钟域异步复位 |

| brstn | input | B时钟域异步复位 |

| data_in | input | A时钟数据输入 |

| data_en | input | A时钟数据有效信号,高电平有效 |

| data_out | output | B时钟域数据输出 |

输入描述:

input clk_a ,

input clk_b ,

input arstn ,

input brstn ,

input [3:0] data_in ,

input data_en

输出描述:

output reg [3:0] dataout

参考代码

`timescale 1ns/1ns

module mux(

input clk_a ,

input clk_b ,

input arstn ,

input brstn ,

input [3:0] data_in ,

input data_en ,

output reg [3:0] dataout

);

reg [3:0] data_b1,data_b2;

reg en_b1,en_b2;

always@(posedge clk_b or negedge brstn)

begin

if(!brstn)begin

en_b1 <= 1'd0;

en_b2 <= 1'd0;

data_b1<='d0;

data_b2<='d0;

end

else begin

en_b1 <= data_en;

en_b2 <= en_b1;

data_b1<=data_in;

data_b2<=data_b1;

end

end

always@(posedge clk_b or negedge brstn)

begin

if(!brstn)begin

dataout <='d0;

end

else begin

dataout <=en_b2?data_b2:dataout;

end

end

endmodule

631

631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?