目录

描述

题目描述:

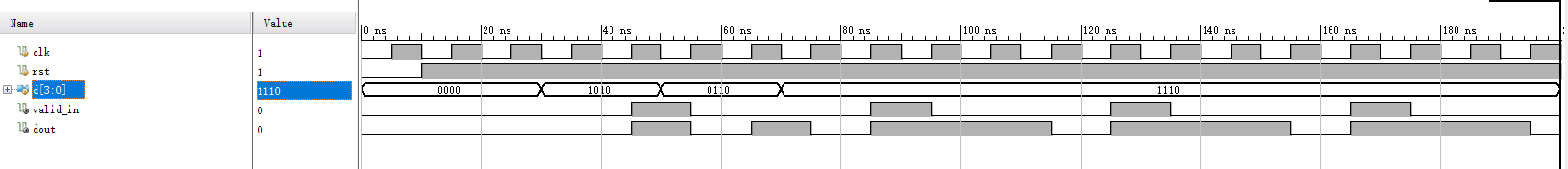

设计一个模块进行并串转换,要求每四位d输为转到一位dout输出,输出valid_in表示此时的输入有效

信号示意图:

clk为时钟

rst为低电平复位

valid_in 表示输入有效

d 信号输入

dout 信号输出

波形示意图:

输入描述:

clk为时钟

rst为低电平复位

d 信号输入

输出描述:

dout 信号输出

valid_in 表示输入有效

参考代码

`timescale 1ns/1ns

module huawei5(

input wire clk ,

input wire rst ,

input wire [3:0]d ,

output wire valid_in ,

output wire dout

);

//*************code***********//

reg [3:0] data = 'd0;

reg [1:0]cnt;//计数

reg valid;

assign dout = data[3];//data的最高位接输出线

assign valid_in =valid;

always @(posedge clk or negedge rst) begin

if(!rst)begin

data<= 'd0;

cnt <= 'd0;

valid <= 'd0;

end

else begin

if (cnt == 'd3) begin

data <= d;//这里d是在cnt清零时给到data上传的

cnt <= 'd0;

valid <= 1;

end

else begin

cnt <= cnt + 'd1;

valid <= 0;

data <= {data[2:0],data[3]};//核心也是循环左移

end

end

end

//*************code***********//

endmodule

1640

1640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?