PCB布局注意事项

1、处理好反馈环,反馈线不要走肖特基下面,不要走电感下面,不要走大电容下面,不要被大电流环路包围,必要时可在取样电阻并个100pF-10nF的电容增加稳定性(但瞬态会受到一点影响)。

2、反馈线宁可细不要粗,因为线越宽,天线效应越明显,影响环路的稳定性。一般用6-12mils的线.

3、所有电容尽可能靠近IC。

4、电感按规格书指标的120-130%的容量选取,不可过大,过大会影响效率和瞬态。电感越靠近芯片越好。不要在电感下方直接铺地,电感中间最好也不要走线,电感两引脚间距不能太近。

5、电容按规格书的150%的容量选取。如果是用贴片陶瓷电容,如果用22uF,用两个10uF并联会更好。若对成本不敏感,电容可用更大些。特别提醒:输出电容,若是用铝电解电容,千万记得要用高频低阻的,不可随便放个低频滤波电容!

6、尽可能缩小大电流环路的包围面积。如果不方便缩小,用敷铜的方式变为一条窄缝。

7、过孔要盖油,否则沾锡以后脏兮兮。尺寸可以稍微大点,阻容用0805的,方便手工焊接。

特别提醒:

输出电容,若是用铝电解电容,千万记得要用高频低阻的,不可随便放个低频滤波电容。同样的电路将输出电容从陶瓷电容改成钽电容,纹波电压会变大,若是改成电解电容纹波会变得特别大。ESR要越小越好,钽电容能不用尽量别用。

有些芯片输出电容ESR太小反而不稳定,容易振荡,最好串联一个小电阻(如1Ω)

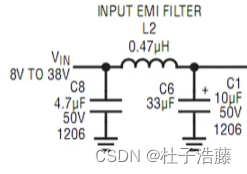

如何进一步降低EMI:

输入用电感接成滤波,输出用磁珠接成

滤波。

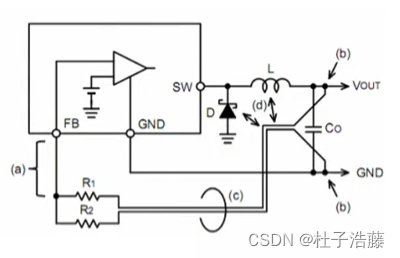

反馈引脚的走线:

(a)通常IC的反馈引脚是设计成高阻输入的。使用短线连接电阻网络和该引脚。

(b)采样输出电压的线必须连接在输出电容或其后。

(c)将分压电阻及线路靠近并平行放置,有利于噪声的抑制。

(d)线路要远离电感和二极管的开关节点。不要直接从电感或二极管下方穿过,也不要与输入电源线平行。多层板也一样。

布线范例

下图是将反馈线路布置在PCB底层,并使用过孔连接,使其远离开关节点

本文详细介绍了PCB布局中需要注意的关键要素,包括处理反馈环、选择电感和电容的合理位置、缩小电流环路、优化过孔和电容类型选择,以及降低EMI的方法和反馈引脚走线的最佳实践。

本文详细介绍了PCB布局中需要注意的关键要素,包括处理反馈环、选择电感和电容的合理位置、缩小电流环路、优化过孔和电容类型选择,以及降低EMI的方法和反馈引脚走线的最佳实践。

8428

8428

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?