一、ModelSim下载安装和基本用法

ModelSim是一种用于硬件描述语言的仿真和调试工具。它可以帮助硬件工程师在将设计实际实现到硬件之前验证其设计。

下载与安装:

-

官方网站:首先,你可以从 ModelSim 的官方网站或去B站博主的一些相关视频那里获取软件。通常,它是作为一个独立的仿真工具或与其他设计套件捆绑在一起提供的。

-

安装:安装过程可能因你使用的版本而异,但通常包括运行安装程序、选择安装目录以及遵循安装向导的步骤。

基本用法:

一旦安装完成,你可以按照以下步骤使用 ModelSim:

-

创建工程: 打开 ModelSim,创建一个新的工程,并添加你的设计文件(Verilog、VHDL 等)。

-

编译: 在工程中进行编译,这将把你的设计翻译成模型可以理解的格式。

-

仿真: 运行仿真以验证你的设计。你可以设置仿真时长、观察信号波形,以及在仿真过程中调试。

-

波形查看: 在 ModelSim 中,有一个波形查看器,你可以使用它来查看信号的变化以及仿真的结果。

-

调试: 如果在仿真过程中发现问题,可以使用 ModelSim 提供的调试功能来定位和解决问题。

二、Quartus下载安装和基本用法

Quartus Prime是由Intel(前身为 Altera)开发的一套用于 FPGA(可编程门阵列)设计的综合工具。它提供了设计、验证和实现数字电路的功能。

下载与安装:

-

官方网站:首先,你可以从 Intel 的官方网站或其指定的下载渠道获取 Quartus Prime。访问 Intel 官方网站 下载页面。

-

选择版本:选择适用于你的操作系统的 Quartus 版本。 Quartus Prime 包括 Standard 和 Lite 两个版本,根据你的需求选择适当的版本。

-

安装:下载完成后,运行安装程序并按照安装向导的步骤进行安装。你可能需要注册并获取许可证。

基本用法:

一旦安装完成,你可以按照以下步骤使用 Quartus Prime:

-

创建工程: 打开 Quartus Prime,创建一个新的工程。在工程中,你需要定义你的设计文件(Verilog、VHDL 等)。

-

设计输入: 输入你的设计,可以使用 Block Diagram、Schematic 或 HDL(硬件描述语言)。

-

编译: 在 Quartus 中进行编译,这将把你的设计综合成逻辑网表(Logic Netlist)。

-

实现: 进行布局(Place)和布线(Route)以确定在 FPGA 上的具体位置和连接方式。

-

时序分析: 进行时序分析以确保设计满足时序约束。

-

生成文件: 生成配置文件和比特流文件,用于烧录到目标 FPGA 设备。

-

下载到 FPGA: 将生成的比特流文件下载到目标 FPGA 上进行实际硬件实现。

三、3-8译码器原理及仿真实验

(一)3-8译码器原理

原理:3-8译码器是一种数字电路,它具有三个输入线和八个输出线。其功能是将三位二进制输入代码映射到其中一个输出线上。每一种可能的输入组合都对应着 8 个输出线中的一个,而其他七个输出线则保持低电平状态。

具体而言,对于一个3-8译码器:

- 输入线:有三条输入线,分别标记为 A, B, 和 C。

- 输出线:有八条输出线,标记为 Y0, Y1, Y2, ..., Y7。

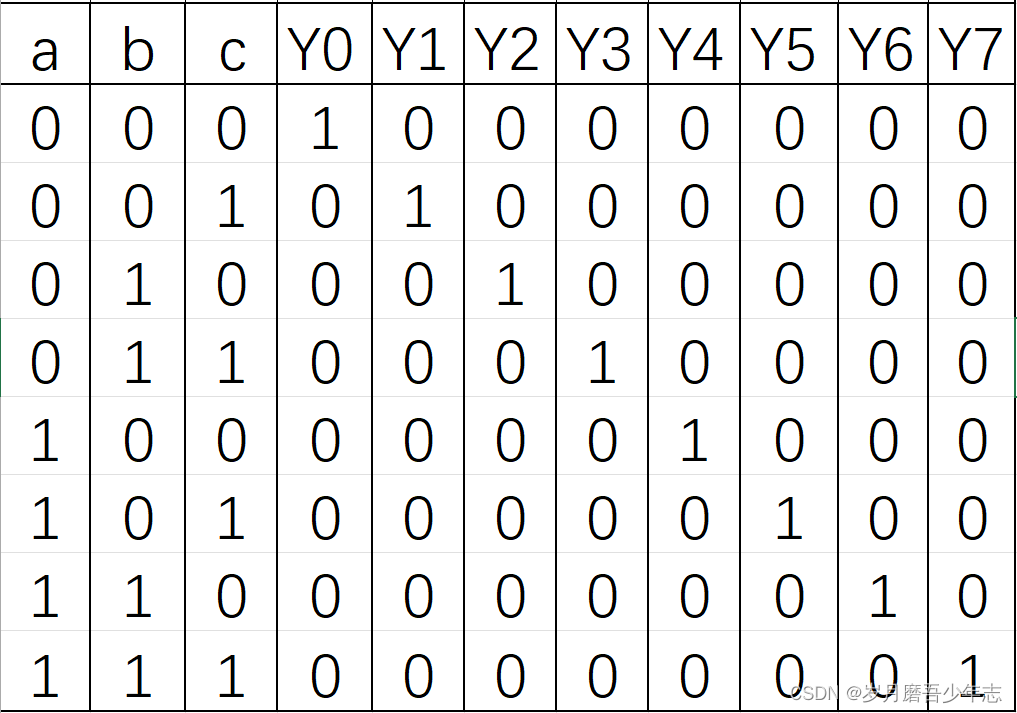

(二)3-8译码器真值表

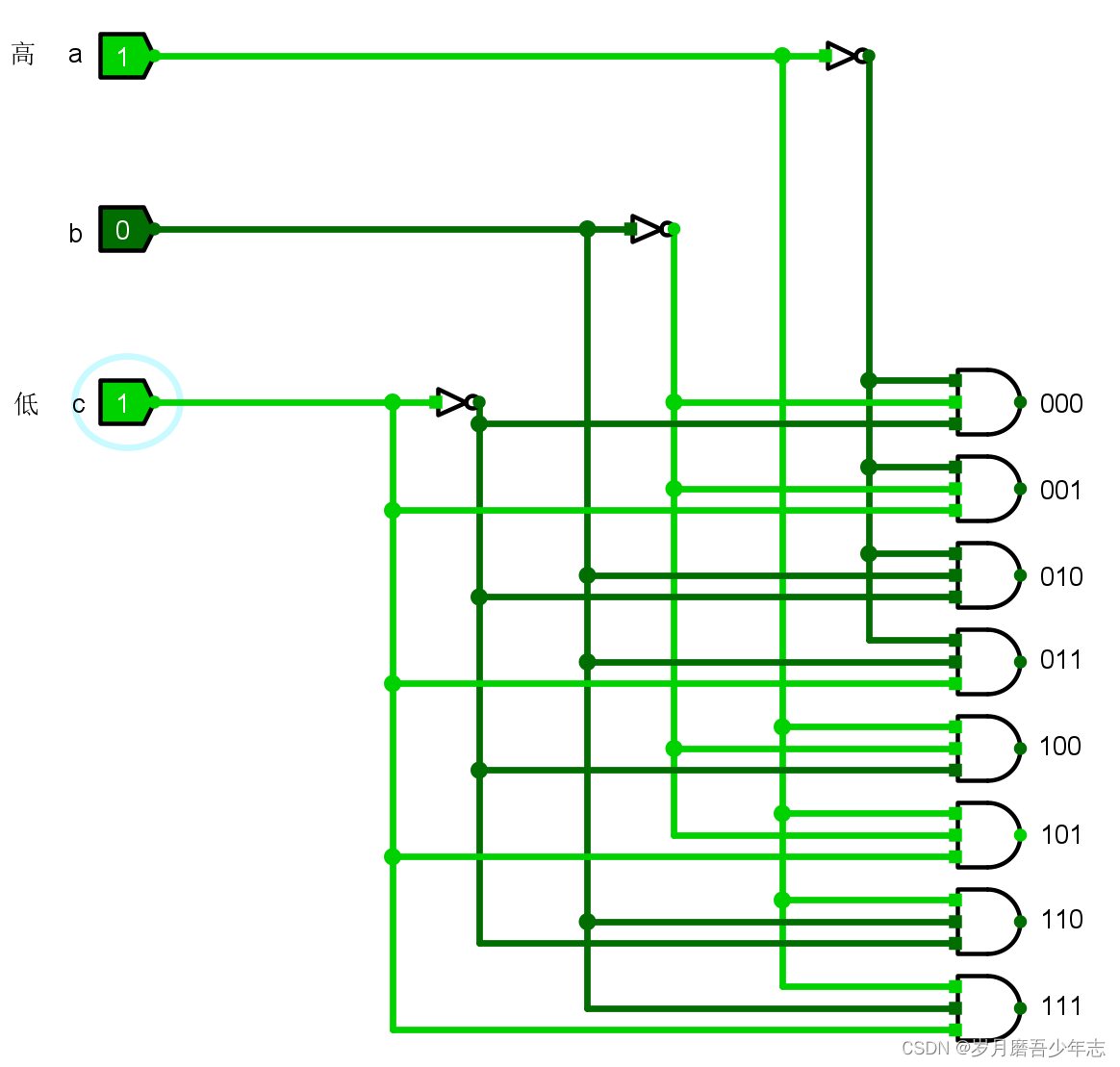

(三)在logsim中进行电路仿真

(四)在quartus中进行模拟

module Decoder_3to8 (

input [2:0] input_code, // 3-bit输入

output [7:0] output_lines // 8个输出线

);

assign output_lines[0] = (input_code == 3'b000) ? 1'b1 : 1'b0;

assign output_lines[1] = (input_code == 3'b001) ? 1'b1 : 1'b0;

assign output_lines[2] = (input_code == 3'b010) ? 1'b1 : 1'b0;

assign output_lines[3] = (input_code == 3'b011) ? 1'b1 : 1'b0;

assign output_lines[4] = (input_code == 3'b100) ? 1'b1 : 1'b0;

assign output_lines[5] = (input_code == 3'b101) ? 1'b1 : 1'b0;

assign output_lines[6] = (input_code == 3'b110) ? 1'b1 : 1'b0;

assign output_lines[7] = (input_code == 3'b111) ? 1'b1 : 1'b0;

endmodule

这个 Verilog 代码中,Decoder_3to8模块有一个3位的输入input_code和8位的输出output_lines。每个输出线通过赋值语句根据输入码的不同条件进行赋值。请注意,这只是一个简单的例子,实际上,3-8译码器通常会使用更复杂的逻辑电路进行实现。此处的代码主要用于演示Verilog中描述3-8译码器的基本方法。在实际的工程中,可能会使用更优化的逻辑电路来实现这一功能。

生成RTL电路图:

代码测试:

// Copyright (C) 1991-2013 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// *****************************************************************************

// This file contains a Verilog test bench template that is freely editable to

// suit user's needs .Comments are provided in each section to help the user

// fill out necessary details.

// *****************************************************************************

// Generated on "12/15/2023 16:30:15"

// Verilog Test Bench template for design : Decoder_3to8

//

// Simulation tool : ModelSim (Verilog)

//

`timescale 1 ps/ 1 ps

module Decoder_3to8_vlg_tst();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg [2:0] input_bits;

// wires

wire [7:0] output_bits;

// assign statements (if any)

Decoder_3to8 i1 (

// port map - connection between master ports and signals/registers

.input_bits(input_bits),

.output_bits(output_bits)

);

initial

begin

$display("Running testbench");

// Test case 1

input_bits = 3'b000;

#10;

if (output_bits !== 8'b00000001) $fatal("Test case 1 failed");

// Test case 2

input_bits = 3'b001;

#10;

if (output_bits !== 8'b00000010) $fatal("Test case 2 failed");

// Test case 3

input_bits = 3'b010;

#10;

if (output_bits !== 8'b00000100) $fatal("Test case 3 failed");

// Test case 4

input_bits = 3'b011;

#10;

if (output_bits !== 8'b00001000) $fatal("Test case 4 failed");

// Test case 5

input_bits = 3'b100;

#10;

if (output_bits !== 8'b00010000) $fatal("Test case 5 failed");

// Test case 6

input_bits = 3'b101;

#10;

if (output_bits !== 8'b00100000) $fatal("Test case 6 failed");

// Test case 7

input_bits = 3'b110;

#10;

if (output_bits !== 8'b01000000) $fatal("Test case 7 failed");

// Test case 8

input_bits = 3'b111;

#10;

if (output_bits !== 8'b10000000) $fatal("Test case 8 failed");

end

always

begin

@eachvec;

end

endmodule

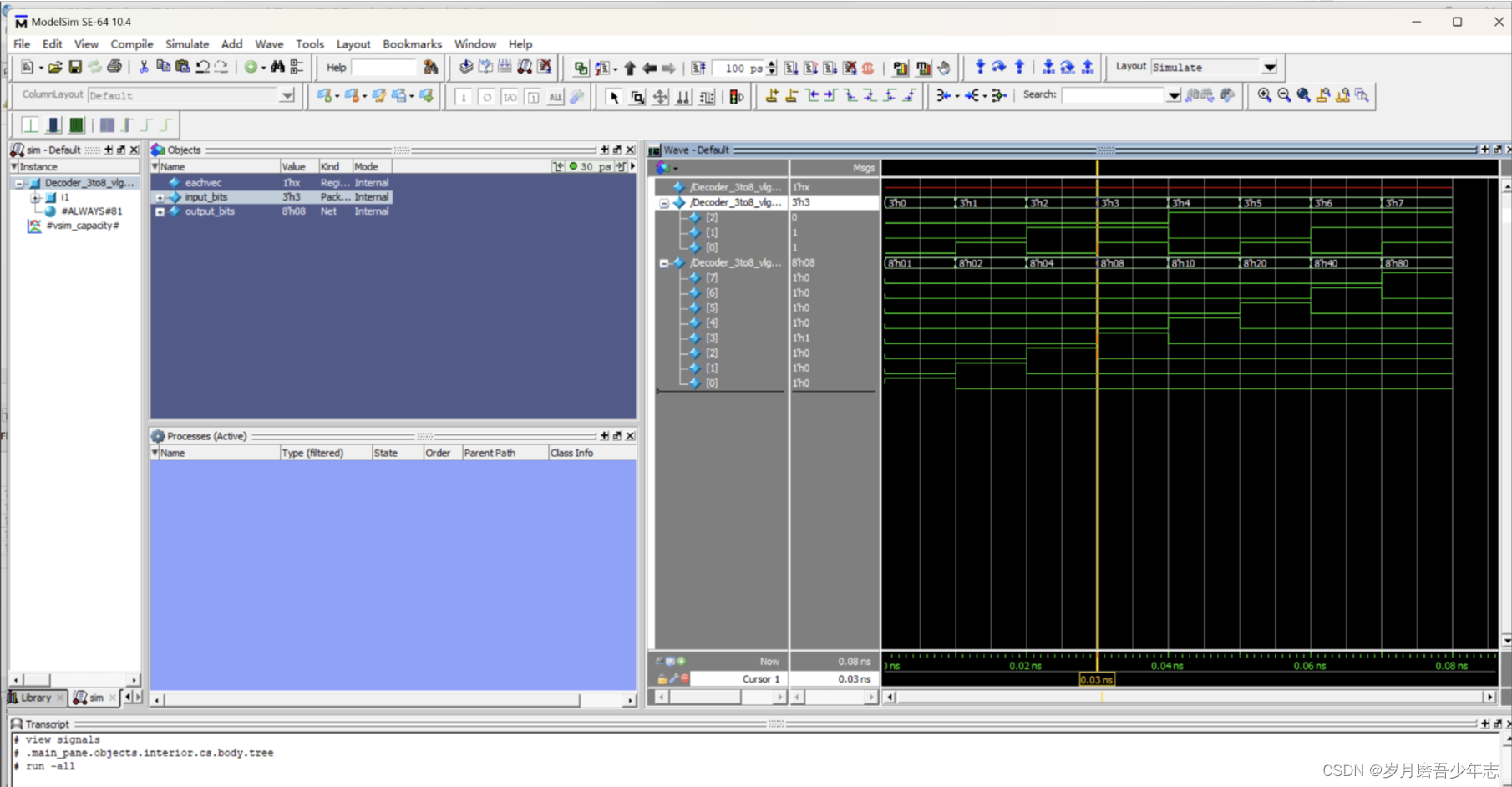

(五)在modelsim中进行仿真并生成波形图

(六)问题解决

1、Verilog 综合生成的3-8译码器电路原理图与原始设计电路存在什么差异?仿真测试生成的结果是否与真值表一致?

(1)原理图与原始设计电路基本没有什么差异,存在的差异可能是对Verilog代码进行逻辑优化,以减小了电路的面积、功耗或提高性能,这可能导致生成的电路与原始设计的逻辑电路不同。

(2)仿真测试生成的结果与真值表一致。

2、Verilog代码设计的3-8译码器模块的输出信号为何要定义为reg类型而不用默认wire(导线)类型?改成wire型是否可以?(即是否可以把 output reg [7:0] out 改为 output [7:0] out) 修改后会出现什么错误?为什么会出错?

(1)定义为reg类型而不用默认wire(导线)类型:在Verilog中,reg 和 wire 是两种不同的数据类型,用于描述信号的行为方式。一般情况下,reg用于描述存储器件,而 wire 用于描述组合逻辑电路的连线。模块的输出通常需要在组合逻辑中进行赋值,而 reg 具备这种可赋值的特性,3-8译码器模块的输出信号 out 是被赋值的,所以要定义为reg类型。

(2)改成wire型是否可以:虽然在某些情况下,你可以使用 wire 类型来声明模块的输出,但为了避免混淆和与传统实践保持一致,通常建议使用 reg 类型。

本文介绍了ModelSim和Quartus这两款硬件描述语言仿真工具的下载、安装步骤,以及它们在电路设计中的基本用法,包括创建工程、编译、仿真和调试。还详细讲解了3-8译码器的原理和在Verilog中的实现,以及如何在ModelSim中进行电路仿真和测试。

本文介绍了ModelSim和Quartus这两款硬件描述语言仿真工具的下载、安装步骤,以及它们在电路设计中的基本用法,包括创建工程、编译、仿真和调试。还详细讲解了3-8译码器的原理和在Verilog中的实现,以及如何在ModelSim中进行电路仿真和测试。

1013

1013

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?