一、概述:

MIPI M-PHY专为需要快速通信通道以支持高分辨率图像、高视频帧速率和大型显示器或存储器的数据密集型应用而设计。这是一款多功能PHY,能够为工程师提供可跨行业平台开发的配置选项和功能,以有效解决多个市场和用例。

MIPI M-PHY用作MIPI CSI-3,MIPI DigRF,MIPI LLI和MIPI UniPro协议的物理层。MIPI M-PHY支持这些原生MIPI联盟协议以及来自PC生态系统的协议,以提供允许移动设备和PC之间融合的技术桥梁。使用MIPI M-PHY的PC工业协议包括JEDEC的UFS,PCI-SIG的Mobile PCIexpress和USB IF的SuperSpeed Inter Chip(SSIC)。

MIPI M-PHY与MIPI UniPort-M接口中的MIPI UniPro传输层相结合,用于移动设备中的创新网络实现。

在M-PHY协议中本地端TX和对端RX采用差分线进行传输。

MIPI M-PHY还使设计人员能够灵活地使用光学介质来实现系统内的高速连接。光学实现可以被配置为数米长的物理连接,以支持诸如汽车这样大平台的设计。

下面来简单地对比一下三种MIPI PHY物理层规范。

| 特性 | M-PHY | D-PHY | C-PHY |

| 主要用例 | 性能驱动、双向通信/网络接口 | 高效单向流式接口,带内低速反向通道 | 高效单向流式接口,带内低速反向通道 |

| HS时钟方法 | 嵌入式时钟 | DDR源同步时钟 | 嵌入式时钟 |

| 通道补偿 | 均衡化 | 数据偏斜控制,相对于时钟 | 编码以减少数据,计时频率 |

| 最小配置和引脚 | 各方向上1个通道,双单工,各通道上2个引脚(共4个) | 1个通道加时钟,单工,4个引脚 | 1个通道(三路),单工,3个引脚 |

| 最大发射器摆动幅度 | SA:250mV(峰值),LA:500mV(峰值) | LP:1300mV | (峰值),HS:360mV(峰值) |

| 各通道的数据速率(HS) | HS-G1:1.25,1.45 Gb/s,HS-G2:2.5,2.9 Gb/s,HS-G3:5.0,5.8 Gb/s;(线路速率为8b10b编码) | 80 Mbps至约2.5 Gbps(合计) | 80 Msym/s至2.5 Gsym/s乘以2.28 bits/sym,或最大5.7 Gbps(合计) |

| 各通道的数据速率(LS) | 10kbps – 600 Mbps | < 10 Mbps | < 10 Mbps |

| 各端口的带宽(3或4个通道) | 约为4.0 - 18.6 Gb/s(总带宽) | 每个4通道端口最大约为10 Gbps(合计) | 每个3通道端口最大约为17.1 Gbps(合计) |

| 每个端口的典型引脚(3或4个通道) | 10(4个通道TX,1个通道RX) | 10(4个通道,1个通道时钟)9(3个通道) | |

| 版本 | v4.1(2017年3月) | v2.1(2017年3月) | v1.2(2017年3月) |

二、M-PHY的原理和特性

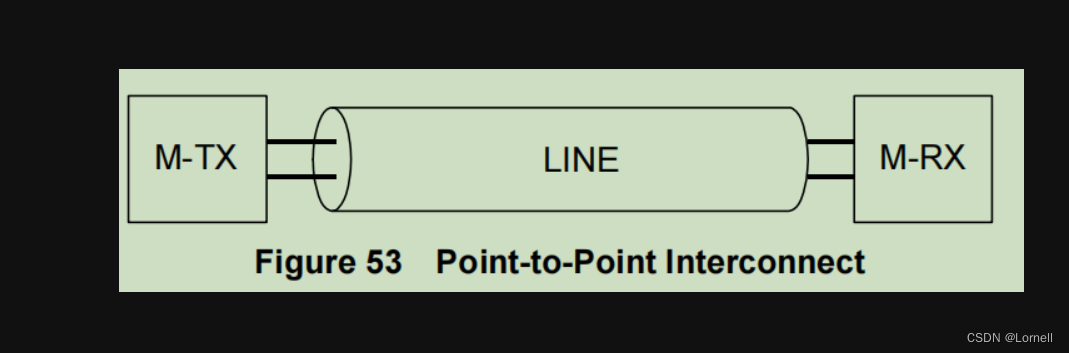

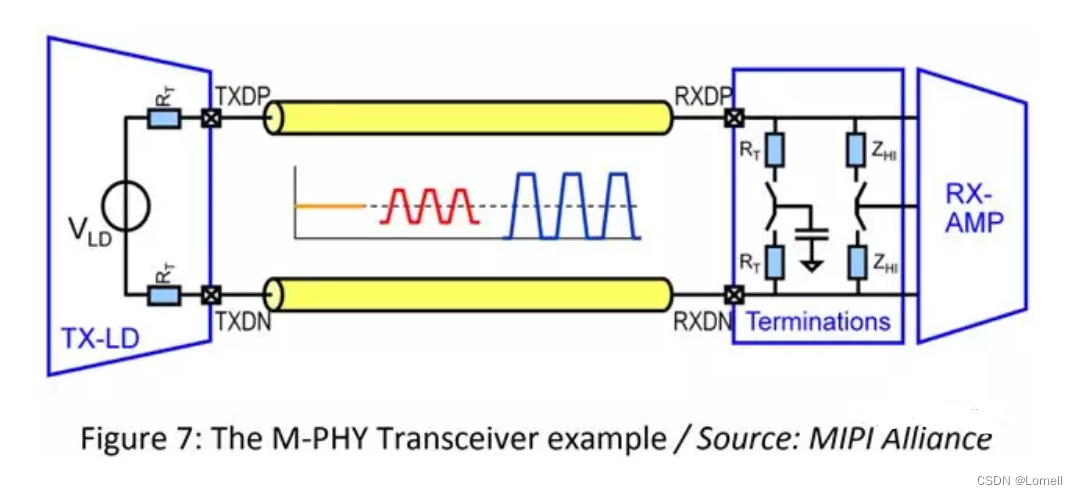

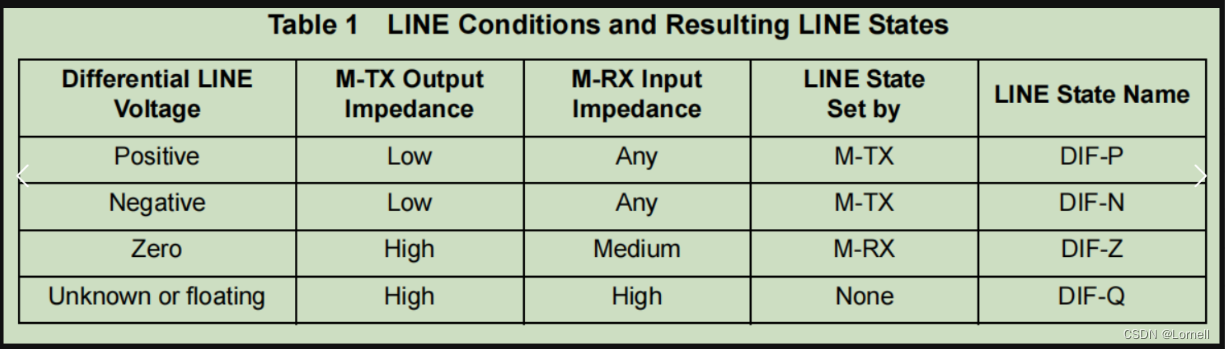

LINE被定义为M-TX和传导LANE信号的M-RX之间的互连。这些信号包括用于高速和低速数据传输的差分信号。因此,一条LINE应通过平衡、差分的点对点传输线路来实现。

一个LINE可能由几条级联传输线路组成,如印刷电路板、柔性箔或电缆连接,这些连接也可能包括通孔和连接器。

一个M-PHY LANE是一个M-TX和一个M-RX之间的单向连接,使用一个LINE作为互连。总体的LANE性能是由这三个元素的组合来决定的。下图显示了一个简单的点对点互连。

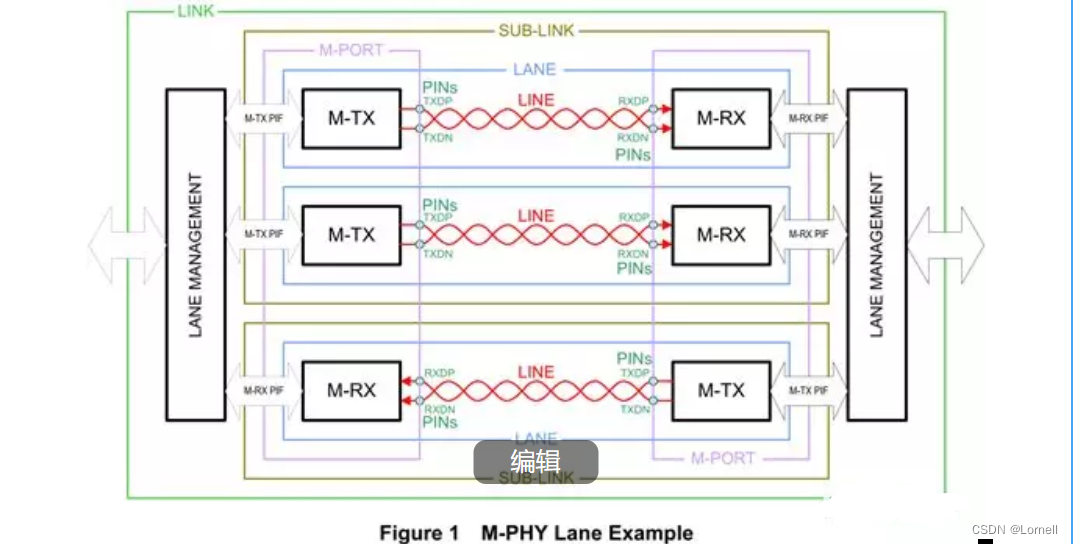

M-PHY的通道结构如下图所示:

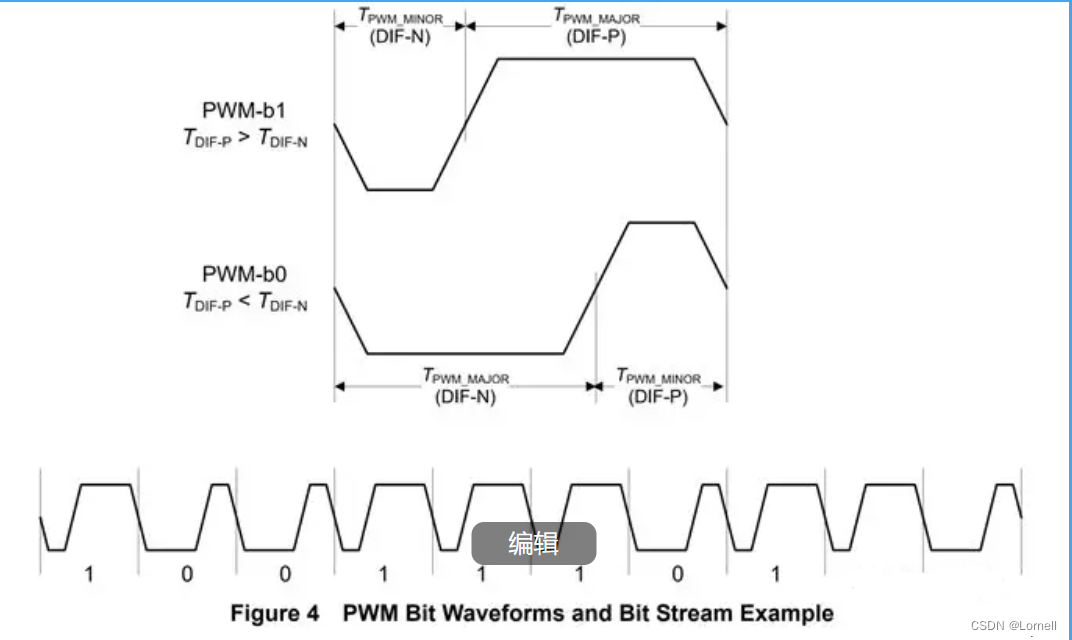

M-PHY使用FIXED-RATIO和FIXED-MINOR两种格式的PWM信号,对于FIXED-RATIO, TPWM_MAJOR和TPWM_MINOR分别占一个bit周期的2/3和1/3;对于FIXED-MINOR,TPWM_MINOR时间固定,TPWM_MAJOR与bit周期成比例。

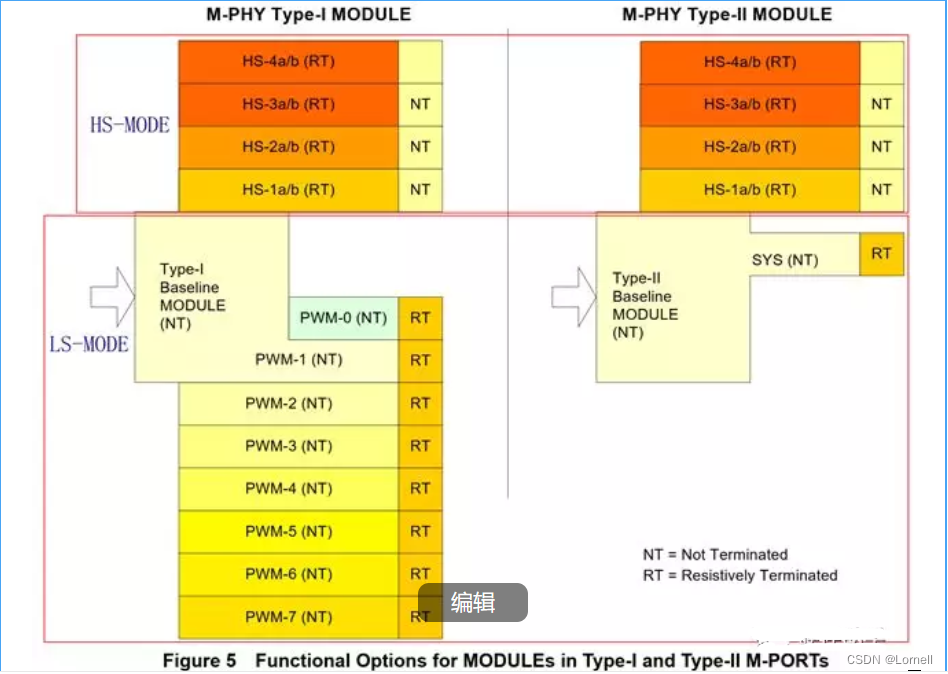

HS-MODE和LS-MODE支持的速率等级如下表所示:

传输:

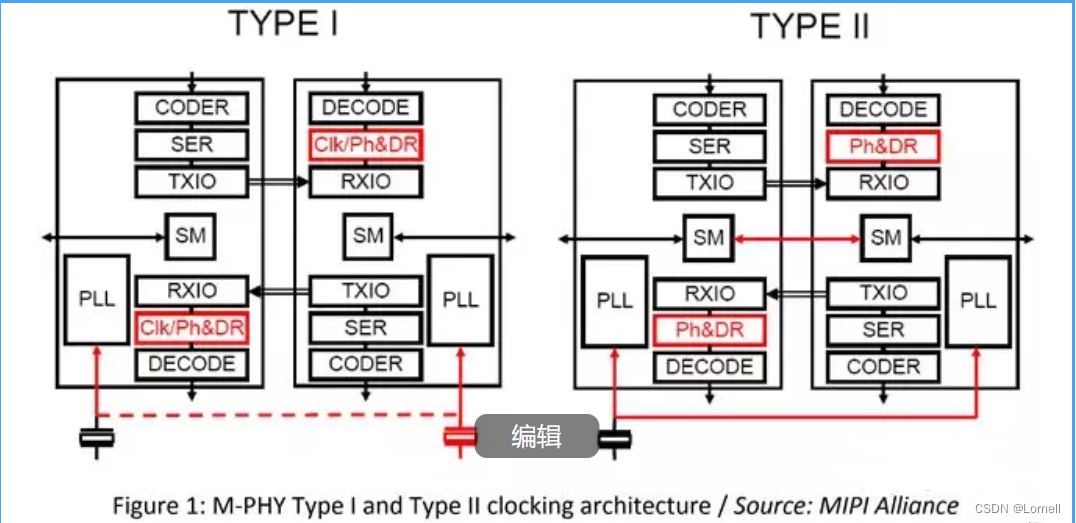

其中LS-MODE为必须支持的模式,有可以分为Type-I和Type-II两种,详细见下图所示:

| 模式 | 等级 | |

| HS-MODE(Gbps级别速率) | HS-G1:1.25/1.45 Gbps(默认的) HS-G2~4,速率是上一级的两倍 | |

| LS-MODE(必须支持)(Mbps级别) | Type-I(PWM signaling) | PWM-G0,可选的 PWM-G1:3~9Mbps(默认的) PWM-G2~7,速率是上一级的两倍 |

| Type-II(SYS(system-clock synchronous, NRZ signaling)) | ||

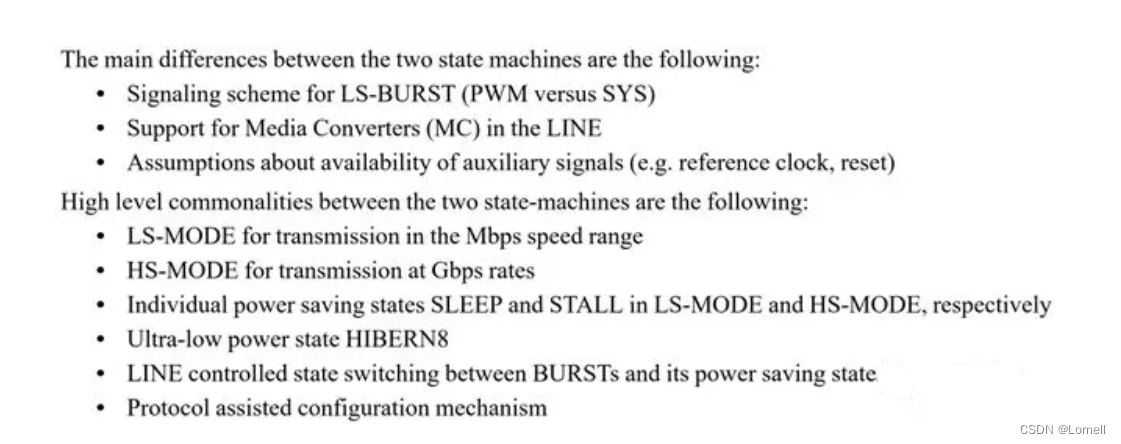

高速和低速模式的区别和共性如下:

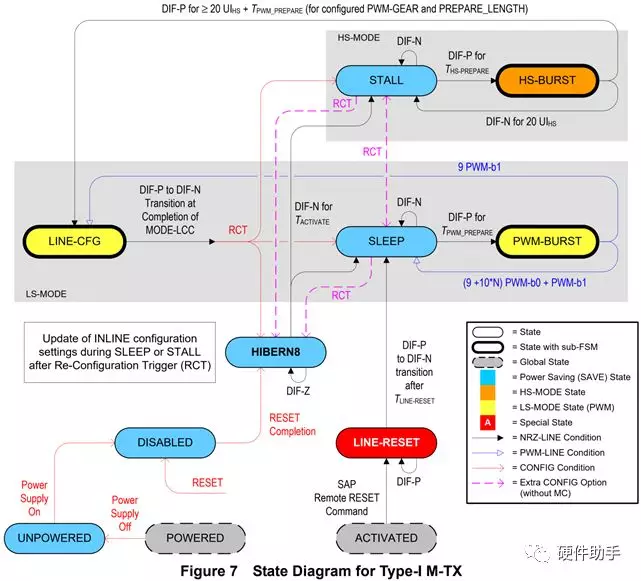

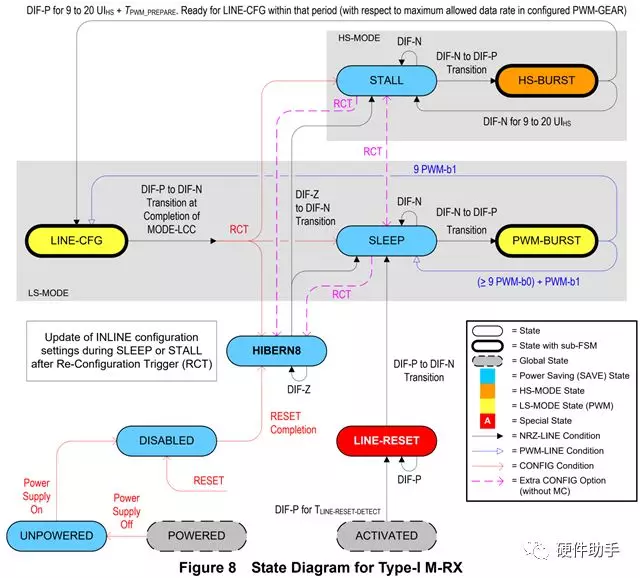

M-TX和M-RX的状态机是相似的,但是状态转移条件是不一样的,因此针对两端的状态机分别进行定义。

每种状态机都有两种操作模式:HS-MODE和LS-MODE,每种操作模式又包括一个数据传输状态(BURST)和模式特有的省电状态(SAVE)。

HS-MODE的SAVE状态是STALL,LS-MODE的省电状态是SLEEP。LS-MODE的BURST状态包括Type-I型的PWM-BURST和Type-II型的SYS-BURST。LS-MODE的Type-I型多一个LINE-CFG状态。每种模式的状态如下:

- HS-MODE: STALL, HS-BURST

- LS-MODE(Type-I MODULE): SLEEP, PWM-BURST, LINE-CFG

- LS-MODE(Type-II MODULE): SLEEP, SYS-BURST

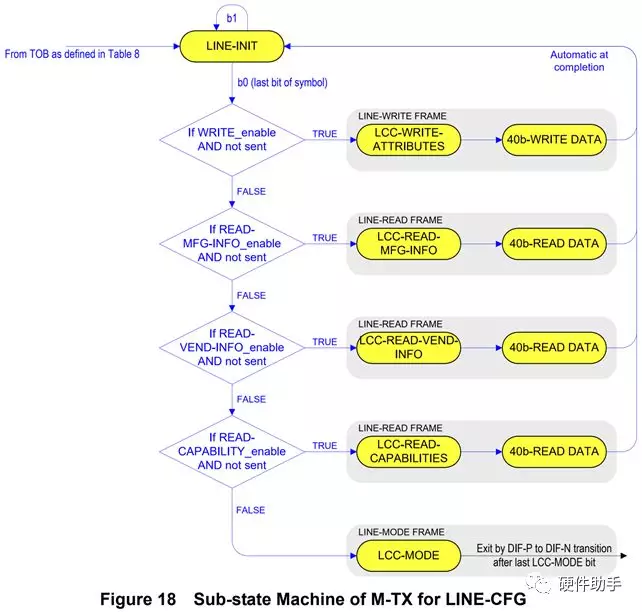

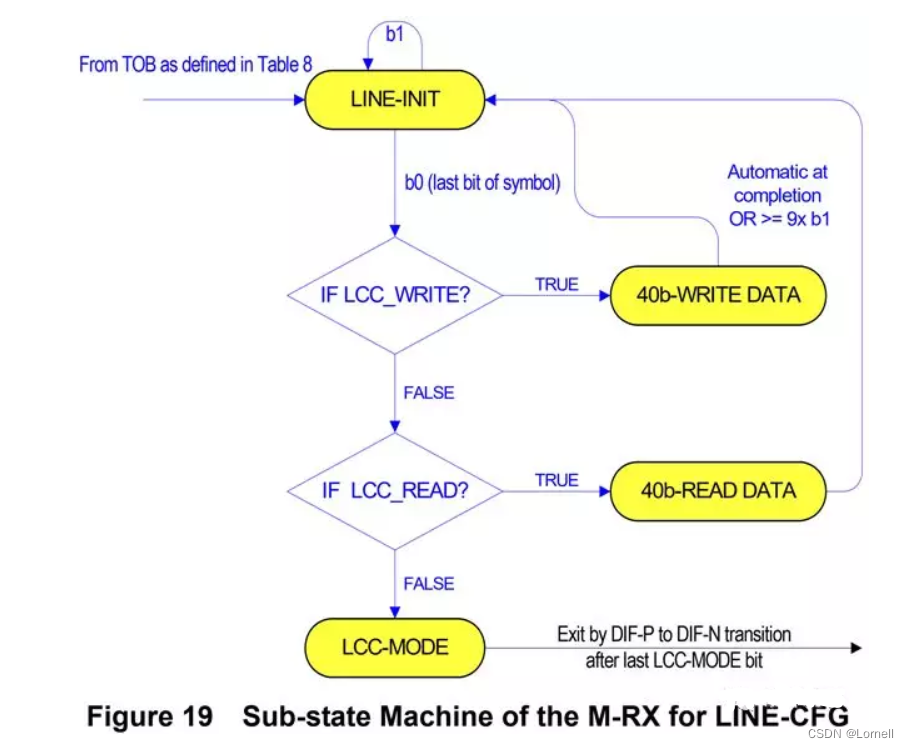

其中,BURST状态和LINE-CFG状态包含子有限状态机。

每种状态机包括五种SAVE状态:一种每种操作模式特定的SAVE状态,一种超低功耗下的状态(HIBERN8),两种系统控制的省电状态,分别如下:

- STALL(HS-MODE)

- SLEEP(LS-MODE)

- HIBERN8(Ultra-low power state where configuration is retained)

- DISABLED(POWERED, but not enabled due to a Power-on Reset, or alocal RESET via the Protocol Interface (Type-II MODULE only))

- UNPOWERED(No power supply)

此外,还有两种特殊用途的BREAK状态:

- LINE-RESET(Embedded remote reset via the LINE)

- LINE-CFG(Configuration for Media Converters; Type-I MODULE only)

最后是两种全局通用的状态:

- POWERED (any state in the state machine, except UNPOWERED)

- ACTIVATED (all states within HS-MODE or LS-MODE taken together)

Type-I MODULE的特性如下:

- PWM self-clocked LS signaling

- Operation with independent local reference clocks; might benefitfrom shared reference clock if available

- Fully embedded control within the LANE (additional auxiliary signalsare not required)

- Support for Media Converters in the LINE

三、电气特性

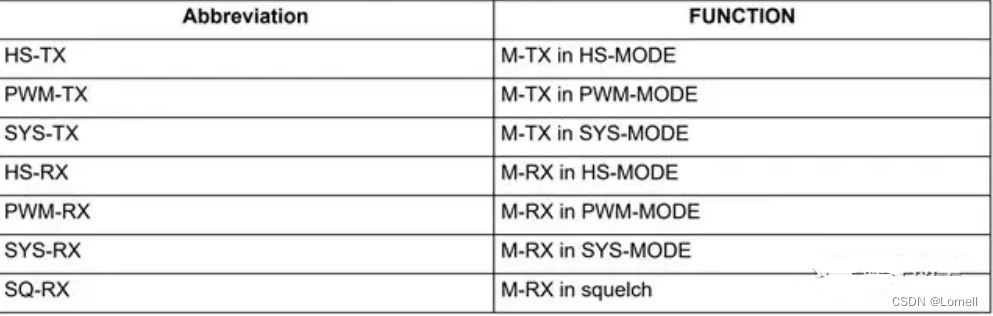

电气特性说明中用到的缩写如下表:

113

113

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?