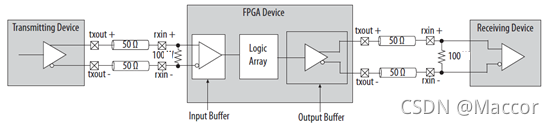

Altera的FPGA顶部、底部和左右侧会有真LVDS 输入缓冲器和LVDS I/O缓冲器。(不同封装 不同系列的器件LVDS的位置,数量会有差异)

LVDS 输入缓冲器支持具有100-Ω 的片上差分匹配(RD OCT)。

可将LVDS I/O缓冲器配置成LVDS 输入( 不带RD OCT) 或者真LVDS 输出缓冲器。

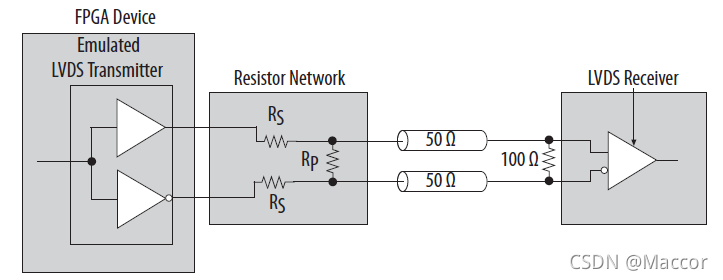

也可以将器件顶端、底部和右侧的LVDS 管脚配置成伪LVDS 输出缓冲器,把两个单端输出缓冲器和一个电路板上的电阻网络一起使用,来支持LVDS、mini- LVDS 和RSDS 标准。

大部分系列的FPGA支持行列I/O bank 上的LVDS。

行I/O 支持100-Ω RD OCT 的真 LVDS 输入和输出缓冲器。列I/O 支持不带RD OCT 的真LVDS 输入缓冲器。

可将行和列LVDS 管脚配置成伪LVDS 输出缓冲器,它把两个单端输出缓冲器和一个外部电阻网络一 起使用,来支持LVDS、mini- LVDS 和RSDS 标准。

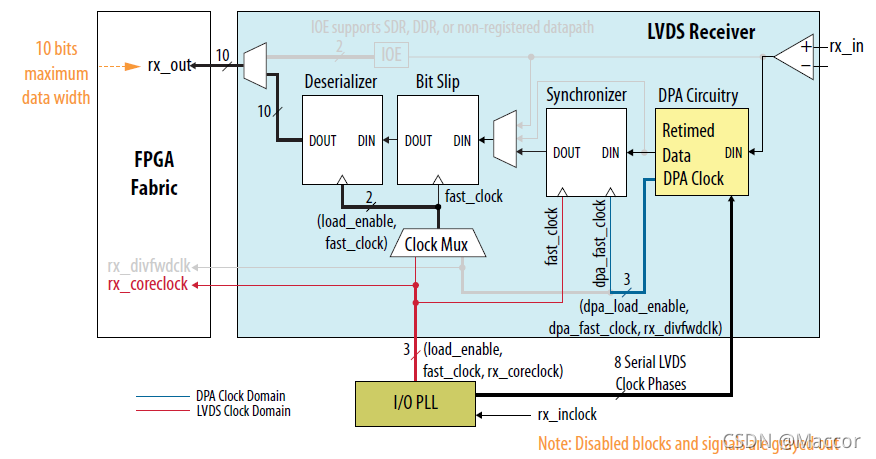

有些高端的器件为LVDS 提供单端 I/O refclk 支持。 专用SERDES 和DPA 电路在器件右侧I/O bank 和行I/O bank 中实现,这可以进一步提高器件中LVDS 接口的性能。列 I/O bank,没有SERDES 电路,如果需要串行收发需要在逻辑中实现。

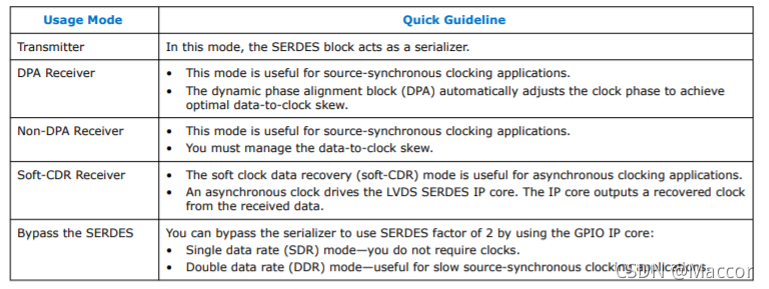

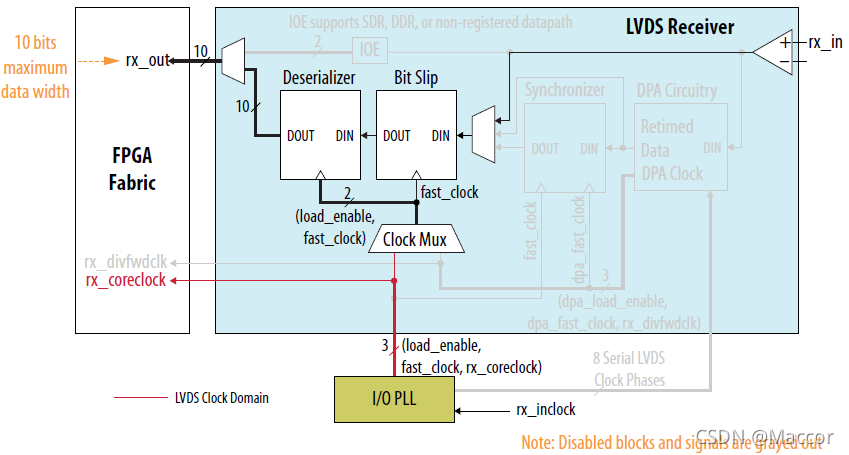

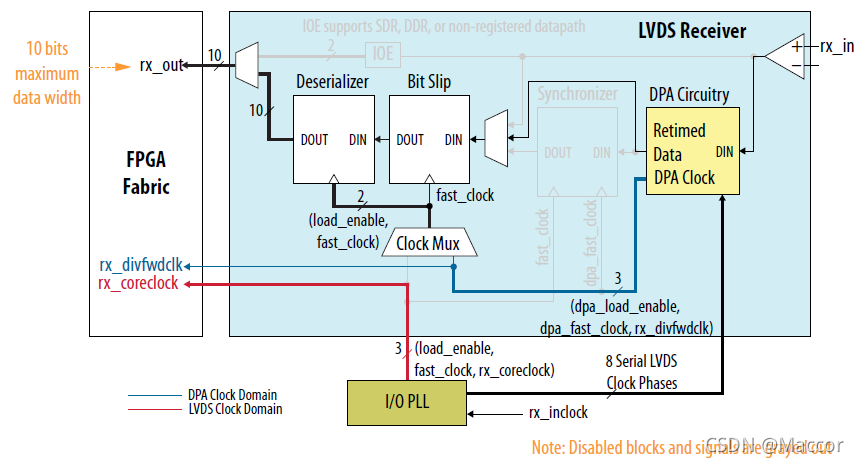

DPA Mode

Non-DPA Mode

Soft-CDR Mode

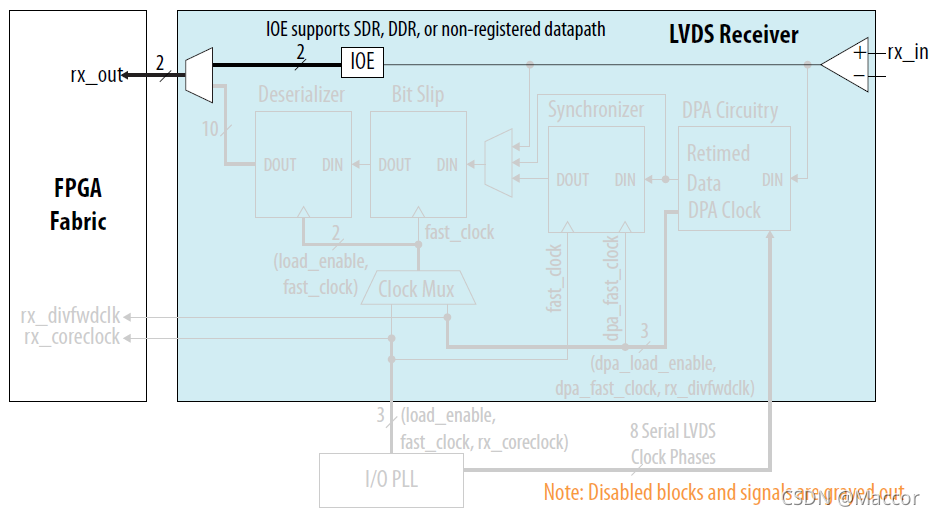

Deserializer Bypass

用于 DPA MODE 和 non-DPA MODE 接收时 , I/O PLL参考时钟必须来自FPGA的专用时钟引脚(不适用于发送)。该引脚可以来自同一BANK也可以是其他I/O BANK。需要注意的是当参考时钟来自其它BANK,需要在QSF文件里声明一下:

set_instance_assignment -name GLOBAL_SIGNAL GLOBAL_CLOCK -to <name of top-level

reference clock input port>

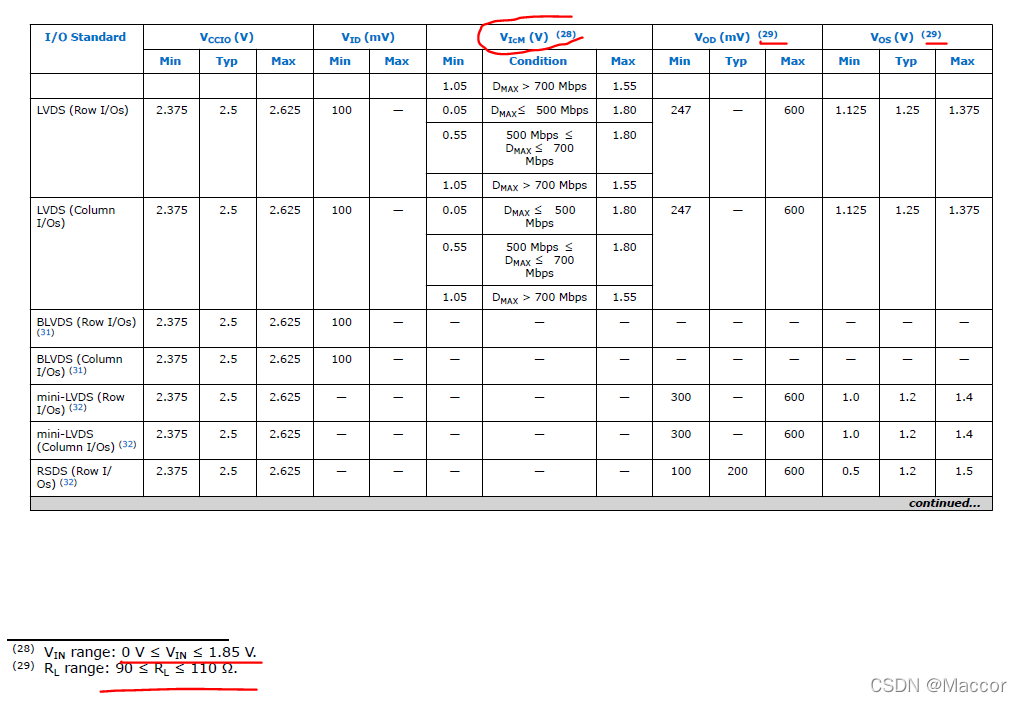

当I/O 缓冲器配置成带RD OCT 使能的LVDS 输入时,需要根据器件datasheet将VCCIO 和VCCPD 设置为需要的电平标准,一般是2.5 V。

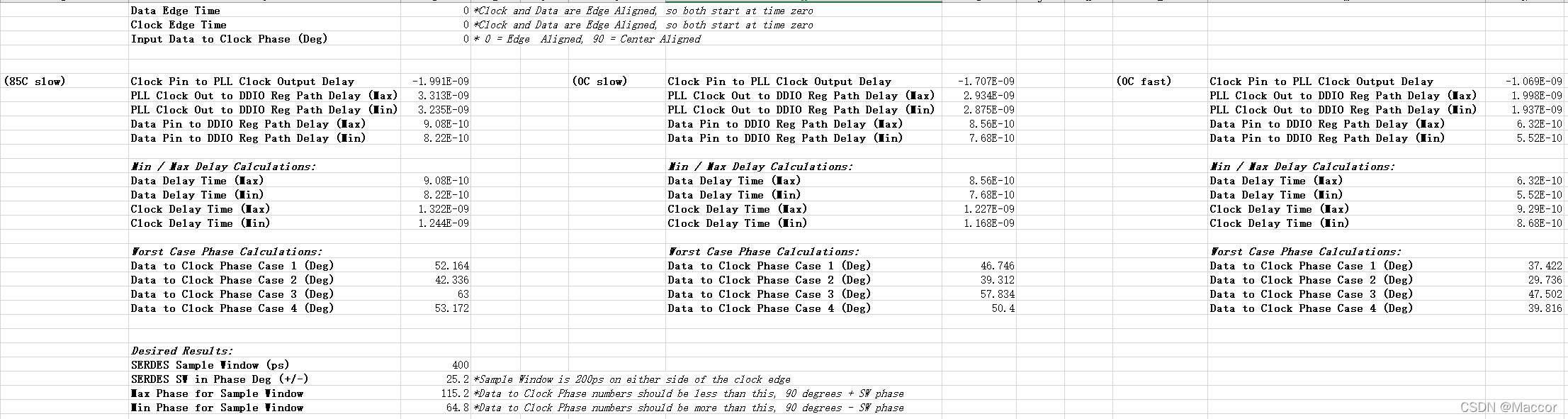

下图所列参数可作为LVDS时序约束的参考:

1081

1081

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?