LVDS(全称Low-Voltage Differential Signaling,低压差分信号)是一种高速、低功耗的差分信号传输技术,广泛应用于数字通信、视频传输、高速数据接口等领域。

如下图所示,LVDS使用一对相位相反的差分信号传输数据,通过两者电压差来判断逻辑值,在发送端单端转差分,在接收端差分转单端。使用差分信号在外部传输时抗干扰能力更强,外部噪声同时作用与两根差分数据线,那么两者电压差基本不受影响。

差分信号用于信号传输,但是在FPGA内部数据处理时,需要将差分信号变为单端使用,所以就需要将外来的差分信号转为单端,可以使用IBUFDS原语实现,将内部的单端信号转为差分信号输出,可以使用OBUFDS原语实现。

IBUFDS原语:

上图中,左侧的输入管脚I和IB从FPGA焊盘输入的外部信号,其中I为差分信号的正端P端,IB为差分信号的负端P端;

该原语可以将差分信号转换为单端信号,右侧的O为原语输出的单端信号,O的值如下:

当I=1,IB为0,O为1;

当I=0,IB为1,O为0;

当I=IB时,此时原语不会工作,会保持之前的值不变;

原语的例化形式如下:

7系器件:

IBUFDS #(

.DIFF_TERM(“FALSE”), // Differential Termination

.IBUF_LOW_PWR(“TRUE”), // Low power=“TRUE”, Highest performance=“FALSE”

.IOSTANDARD(“DEFAULT”) // Specify the input I/O standard

) IBUFDS_inst (

.O(O), // Buffer output

.I(I), // Diff_p buffer input (connect directly to top-level port)

.IB(IB) // Diff_n buffer input (connect directly to top-level port)

);

Ultrascale+器件:

IBUFDS IBUFDS_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB(IB) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

可以看到两个原语的端口一致,不过7系的原语多了三个参数;

参数说明:

参数DIFF_TERM:差分终端电阻,控制是否启用FPGA内部的差分终端电阻,用于匹配传输线阻抗(通常为100Ω),减少信号反射。

“TRUE”:启用内部终端电阻,适用于未外接终端电阻的差分信号链路(如LVDS长距离传输)。

“FALSE”:禁用内部终端电阻,需外接物理电阻(常见于短距离或已预匹配阻抗的电路)。

参数IBUF_LOW_PWR:低功耗模式,控制输入缓冲器的功耗与性能平衡。

“TRUE”:低功耗模式,适用于对功耗敏感的场景(如电池供电设备),但可能降低信号带宽和抗噪能力。

“FALSE”:高性能模式,提升信号处理速度,适用于高速接口(如Camera Link)。

例如低速传感器接口选"TRUE",千兆以太网或高速ADC接口选"FALSE"。

参数IOSTANDARD:输入电平标准,指定输入信号的电气标准,确保FPGA引脚电平与外部设备兼容。

常见值:

“LVDS_25”:LVDS差分信号,1.25V共模电压(默认值,Bank供电电压为2.5V)。

“LVDS”:LVDS差分信号,1.25V共模电压(默认值, Bank供电电压为1.8V)。

“LVCMOS18”:单端1.8V LVCMOS电平。

“DEFAULT”:自动适配Bank默认电平,但需确保FPGA Bank供电与外部信号匹配。

其中Xilinx 7系列FPGA的HP Bank仅支持1.2V~1.8V电平,HR Bank支持3.3V电平,需结合实际使用的Bank类型选择。

其中差分的输入端口需直接连接到顶层的输入端口;

且I和IB极性相反,原语才能正常工作;

关于Ultrascale+器件,UltraScale+系列对I/O逻辑进行了重构,部分参数(如DIFF_TERM)默认集成到I/O Bank的全局配置中,而非通过原语单独设置。

例如差分终端电阻(DIFF_TERM)的启用/禁用由Vivado的I/O约束文件(XDC)统一管理。

电平标准(IOSTANDARD)通过FPGA Bank的电压配置自动适配,减少手动参数设置需求。

Ultrascale+器件功耗与性能的自动化控制逻辑将IBUF_LOW_PWR参数在UltraScale+器件中移除,改为由工具根据设计时序和功耗约束自动选择最优模式。

当前UltraScale+器件可通过属性约束替代参数:

在UltraScale+中,原语参数的功能被转移到I/O端口属性中。例如:

(* IOSTANDARD = “LVDS_25”, DIFF_TERM = “TRUE” *)

IBUFDS ibufds_inst (.O(O), .I(I), .IB(IB));

这种方式将电平标准和终端电阻配置直接绑定到端口,而非原语内部参数去控制。

IBUFDS原语仿真;

测试模块:

module top_7series_ibufds(

input wire clk,

input wire rst,

input wire din_p,

input wire din_n,

output wire dout

);

IBUFDS #(

.DIFF_TERM(“FALSE”), // Differential Termination

.IBUF_LOW_PWR(“TRUE”), // Low power=“TRUE”, Highest performance=“FALSE”

.IOSTANDARD(“DEFAULT”) // Specify the input I/O standard

) IBUFDS_inst (

.O(dout), // Buffer output

.I(din_p), // Diff_p buffer input (connect directly to top-level port)

.IB(din_n) // Diff_n buffer input (connect directly to top-level port)

);

endmodule

testbench:

设置两个随机的信号输入,然后仿真查看原语对于输入的处理结果,其中每100ns产生随机的输入,且两个输入极性不一定相反;

`timescale 1ns / 1ps

module tb;

reg clk;

reg rst;

reg data_p;

reg data_n;

wire dout;

initial begin

clk = 0;

rst = 1;

#100

rst = 0;

end

initial begin

data_p = 0;

data_n = 0;

while(1)begin

#100

data_p = $random;

data_n = $random;

end

end

top_7series_ibufds inst_top_7series_ibufds (

.clk(clk),

.rst(rst),

.din_p(data_p),

.din_n(data_n),

.dout(dout)

);

endmodule

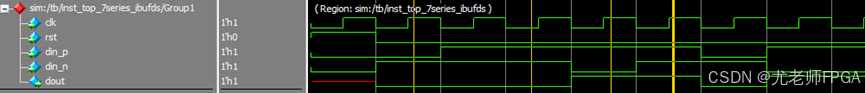

仿真结果:

可以看到,

在第1个黄线处,data_p输入0,data_n输入1,此时输出为0,输出有效;

在第2个黄线处,data_p输入1,data_n输入1,那么输出就保持了之前第1个黄线处的有效输出0,此时原语不工作;

在第3个黄线处,data_p输入1,data_n输入0,此时输出为1,输出有效;

在第4个黄线处,data_p输入1,data_n输入1,输出又保持了之前第3个黄线处的有效输出1,此时原语不工作;

仿真的结果符合原语的特性;

8168

8168

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?