原文地址:http://blog.sina.com.cn/s/blog_65a8ca540100kwi4.html

module series_det(clk,rstn,a,b);

input clk,rstn;

input a;

output reg b;

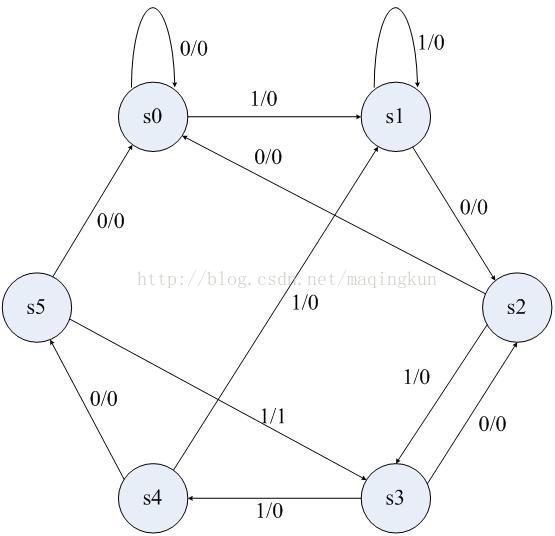

parameter s0=0,s1=1,s2=2,s3=3,s4=4,s5=5;

reg [2:0]s;

always@(posedge clk)

if(!rstn) begin s<=s0;b<=0; end

else case(s)

s0:

if(a) begin s<=s1;b<=0;end

else begin s<=s0;b<=0;end

s1:

if(a) begin s<=s1;b<=0;end

else begin s<=s2;b<=0;end

s2:

if(a) begin s<=s3;b<=0;end

else begin s<=s0;b<=0;end

s3:

if(a) begin s<=s4;b<=0;end

else begin s<=s2;b<=0;end

s4:

if(a) begin s<=s1;b<=0;end

else begin s<=s5;b<=0;end

s5:

if(a) begin s<=s3;b<=1;end

else begin s<=s0;b<=0;end

default:

begin s<=s0;b<=0;end

endcase

endmodule

1147

1147

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?