Latency

PCIe链路的Latency包含

• Data payload size of a TLP

• Core latency between the Application Layer and the Link (varies between Receive and Transmit transactions)

• Switch latency

• Completer latency, such as SDRAM read latency and SRAM mailbox read latency

• PCI Express to PCI/PCI-X bridge latency and latency inherent to a PCI component

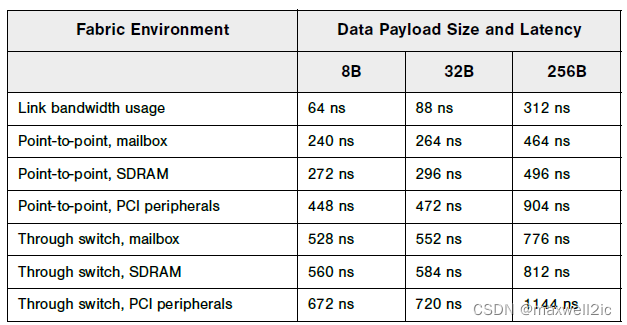

下表列出一些实测典型应用场景下read request transaction的latency

Maximum Effective Bandwidth

有效带宽的计算公式如下:

Maximum Effective Bandwidth = data / (data + overhead)

其中PCIe链路的overhead包括3个方面

1. PHY层编码方案

Gen1/Gen2情况下,数据包按照8b/10b编码,即8bit的数据要编码为10bit的数据,多了2bit的非数据bit,编码效率为80%。例如Gen2x16最大支持 5 * 8 / 10 * 16 = 8 GB/s的带宽。

从Gen3开始,数据包按照128b/130b方式编码,即128bit的数据编码为13

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

697

697

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?