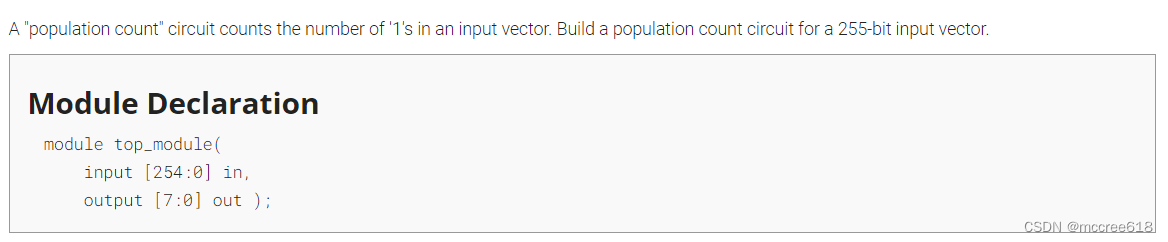

·255-bit population count

module top_module(

input [254:0] in,

output [7:0] out );

integer i;

always @(*) begin

out = 0;

for (i=0;i<$bits(in);i++)

if (in[i] == 1'b1)

out = out + 1'b1;

else

out = out + 1'b0;

end

endmodule

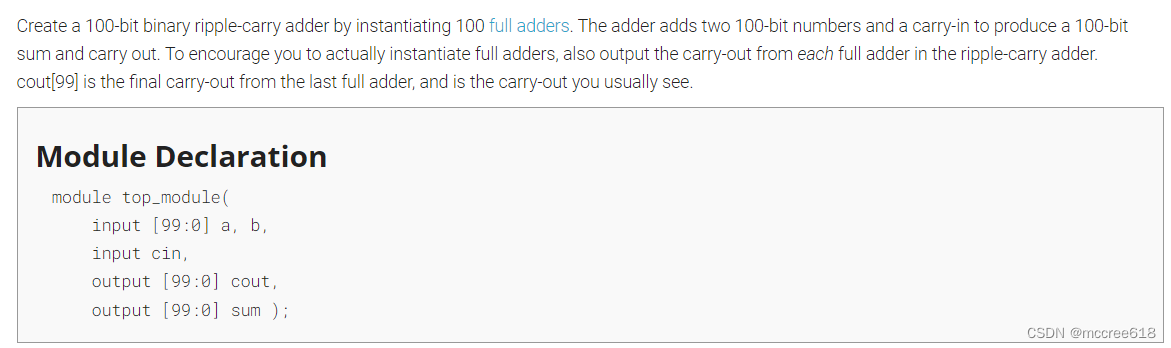

·100-bit binary adder

注意事项:需使用generate产生可生成多次实例的循环,语法可参照(6条消息) Verilog中generate的使用(转载)_竖条你要听话的博客-CSDN博客_verilog中generate用法![]() https://blog.csdn.net/qq_41624212/article/details/122834972需特别注意的两个点:

https://blog.csdn.net/qq_41624212/article/details/122834972需特别注意的两个点:

1、循环中的参量需用genvar声明。 2、for循环后需接begin并指出实例对象名称

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

genvar i;

generate

for(i=0;i<$bits(a);i++) begin: adder

if(i==0)

add1 adder(a[i], b[i], cin, sum[i], cout[i]);

else

add1 adder(a[i], b[i], cout[i-1], sum[i], cout[i]);

end

endgenerate

endmodule

module add1 (input a, input b, input cin, output sum, output cout);

assign sum = a ^ b ^ cin;

assign cout = (a&b)|(a&cin)|(b&cin);

endmodule

299

299

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?