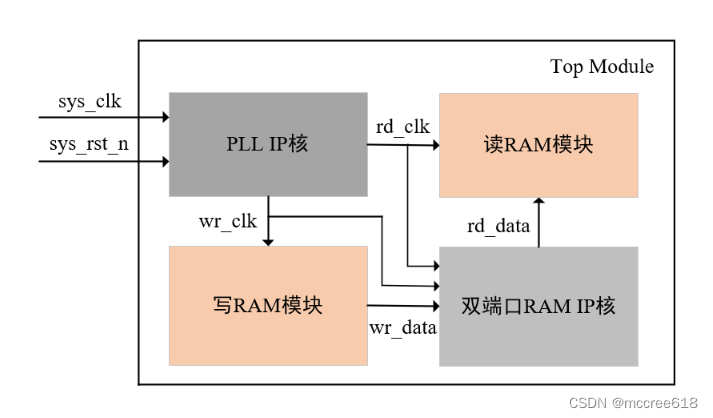

设计系统框图

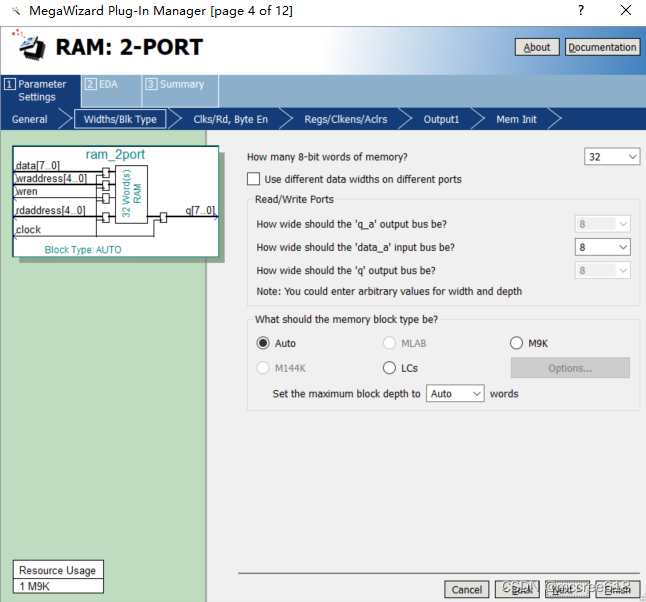

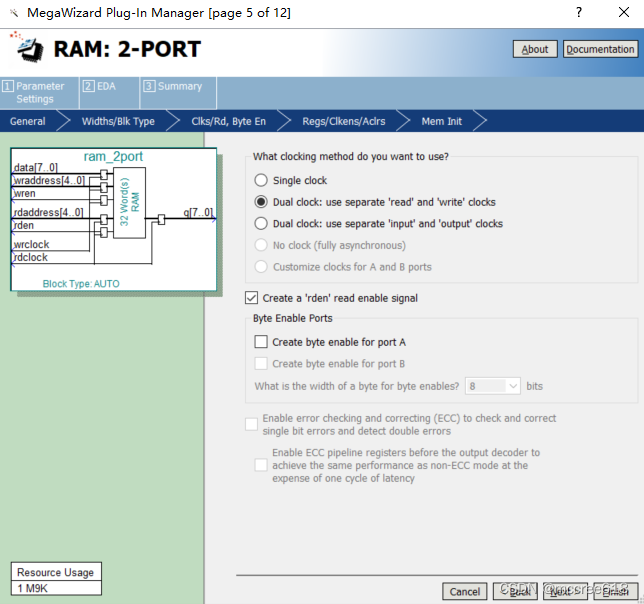

一、创建 双端口RAM IP核

为实现跨时钟域同步操作,还需创建PLL核模块,以获取50Mhz及25Mhz的时钟

二、模块RTL实现

Top module:

module ram_2port_ip(

input sys_clk,

input sys_rst_n

);

wire ram_r_en;

wire ram_w_en;

wire [7:0]ram_w_data;

wire [4:0]ram_w_addr;

wire [7:0]ram_r_data;

wire [4:0]ram_r_addr;

wire clk_50m;

wire clk_25m;

wire locked;

wire rst_n;

assign rst_n = sys_rst_n & locked;

pll_clk u0 (

.areset ( ~ sys_rst_n ),

.inclk0 ( sys_clk ),

.c0 ( clk_50m ),

.c1 ( clk_25m ),

.locked ( locked)

);

ram_wr u1(

.sys_

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?