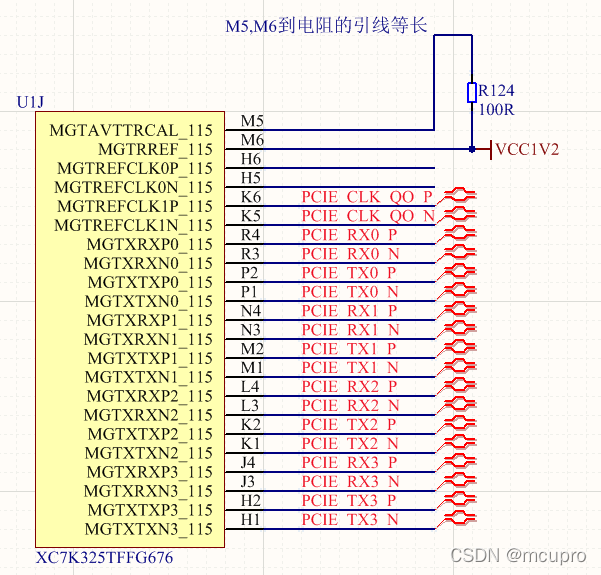

在做新的一版SDR平台时候有一个疑问就是,就是关于K7高速口的分配,要用到6组高速口接SFP,其中QSFP占用4对,单路SFP两个占用两对。这些高速对是否可以任意分配到高速口上呢,这就是接下来试验要解决的问题。

首先从已经有的经验,之前做PCIEX4时候那高速线是可以任意成组分配的。一成组分配我们说的意思是,比如tx1_p,tx1_n,rx1_p,rx1_n这四根信号线可以对应的跟tx2_p,tx2_n,rx2_p,rx2_n一一交换,并且一交换就要交换四根 。

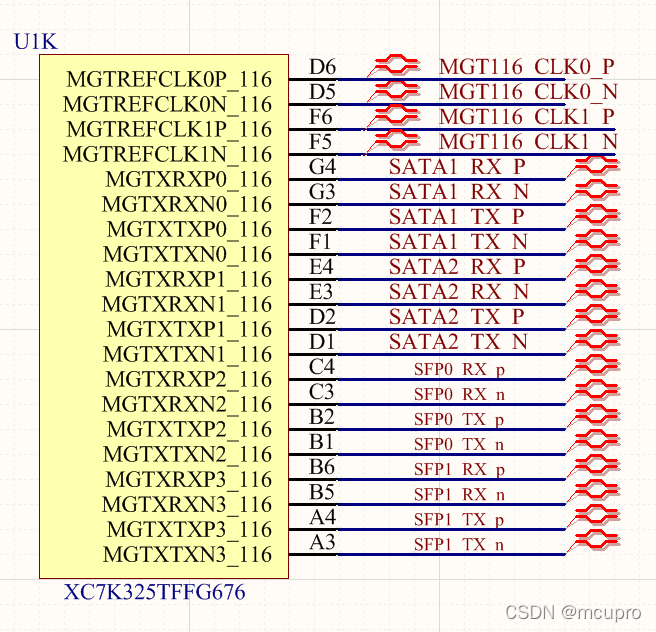

我这里利用现有一个用到7K325的10G光口项目,用到了两路光口,我就分别将这两路尝试连接7K325的8组高速接口上,看是否编译通过并且生产最终的bit流文件。

下面是完整的XDC约束文件:

set_property PACKAGE_PIN F6 [get_ports ref_clk_p0]

create_clock -period 6.400 -name ethclk0 -waveform {0.000 3.200} [get_ports ref_clk_p0]

set_property PACKAGE_PIN G12 [get_ports tx_disable0]

set_property IOSTANDARD LVCMOS25 [get_ports tx_disable0]

set_property PACKAGE_PIN J13 [get_ports tx_disable1]

set_property IOSTANDARD LVCMOS25 [get_ports tx_disable1]

# set_property PACKAGE_PIN A4 [get_ports mgt_tx_p0]

# set_property PACKAGE_PIN B2 [get_ports mgt_tx_p1]

set_property PACKAGE_PIN D2 [get_ports mgt_tx_p0]

set_property PACKAGE_PIN F2 [get_ports mgt_tx_p1]

set_property PACKAGE_PIN A15 [get_ports led_up]

set_property IOSTANDARD LVCMOS25 [get_ports led_up]

set_property PACKAGE_PIN B12 [get_ports led_dwn]

set_property IOSTANDARD LVCMOS25 [get_ports led_dwn]

set_false_path -from [get_pins {tengbaser_infra0_inst/ten_gig_eth_pcs_pma_core_support_layer_i/ten_gig_eth_pcs_pma_shared_clock_reset_block/reset_pulse_reg[0]/C}] -to [get_pins {tengbaser_infra0_inst/ten_gig_eth_pcs_pma_core_support_layer_i/ten_gig_eth_pcs_pma_shared_clock_reset_block/gttxreset_txusrclk2_sync_i/sync1_r_reg*/PRE}]

#set_clock_groups -name asyncclocks_eth0_usr_clk -asynchronous -group [get_clocks -of_objects [get_cells -hierarchical -filter {name=~*clk_counter*}]] -group [get_clocks -include_generated_clocks ref_clk_p0_CLK]

set_property CONFIG_VOLTAGE 2.5 [current_design]

set_property CFGBVS VCCO [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 33 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.SPI_32BIT_ADDR Yes [current_design]

set_property BITSTREAM.CONFIG.TIMER_CFG 2000000 [current_design]

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_false_path -from [get_pins {tengbaser_infra0_inst/ten_gig_eth_pcs_pma_core_support_layer_i/ten_gig_eth_pcs_pma_shared_clock_reset_block/reset_pulse_reg[0]_replica/C}] -to [get_pins {tengbaser_infra0_inst/ten_gig_eth_pcs_pma_core_support_layer_i/ten_gig_eth_pcs_pma_shared_clock_reset_block/gttxreset_txusrclk2_sync_i/sync1_r_reg[*]/PRE}]

其中我就是修改下图中红框的两个tx_p的引脚号,之后进行编译看是否成成BIT流文件的。

这里为什么没有设置mgt_tx_n0和mgt_tx_n1以及接受通道呢,道理很简单,高速差分对是确定的,指定差分对的一个,就指定了这个收发器,指定了这个收发器也就确定了rx_p,rx_n,tx_p,tx_n。

编译时间太长,等待编译出结果之后我再续写

下班后就回家了,远程看了看编译通过顺利生成BIT流文件。最终的结论是:每一组GTX收发器都可以接10G SFP光口。

上图是远程查看编译结果。

{{aAxvOXMOIvVUoXMxvoxiowMwWV8xxWTxoxOIOVIUUOvwVOUiIoUvvTMMVMwovWHWX8vOUOwvv8TovIoiUHMx8ovwmIOoWwHXoxTmMwIVioXoH8vVHOMoiHIoVU8VvmvIWXTvvOvv8xvMovOWMWOwUWiX8UmooOTvvwUIoTwvmWUoiTw8VmvoHWwMIUWOixiowiUoiXwiwwMMIiIXHwUmOWUVmXXwV8iHWOTUiwTU8xwOoV8HVmTWZz}}

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?