一.RAM简介

1.1RAM种类简介

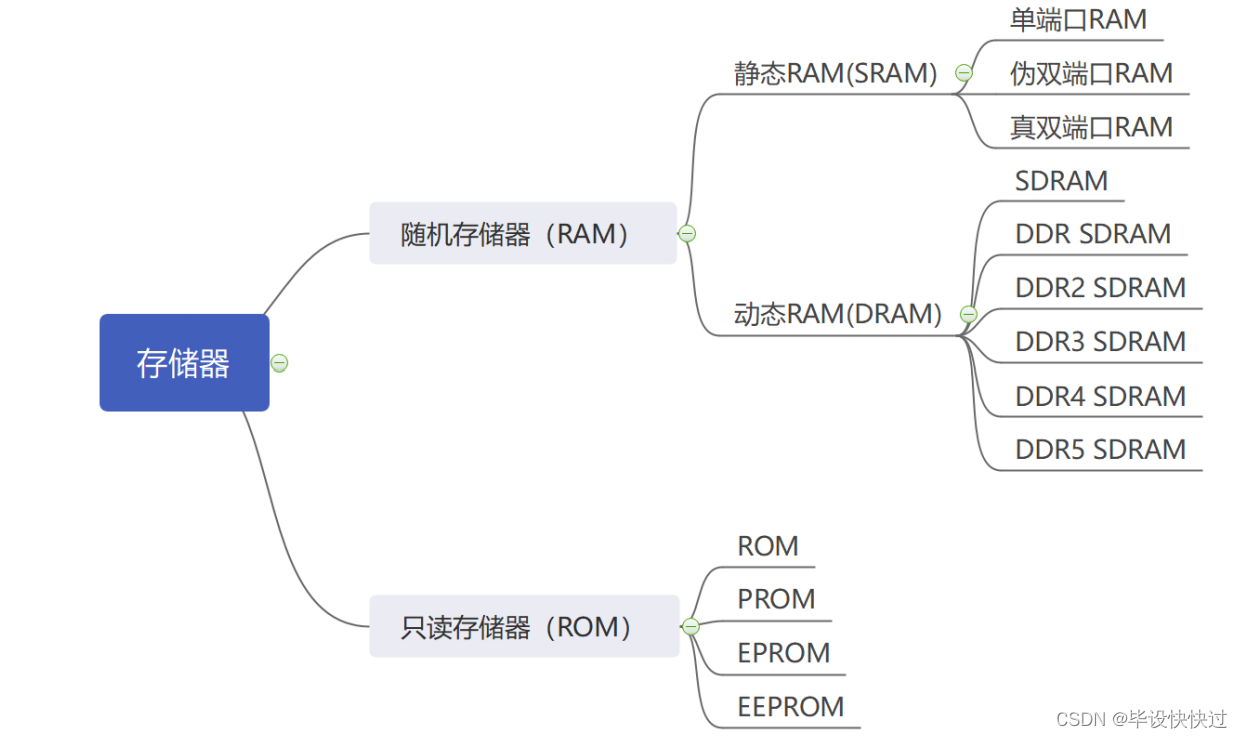

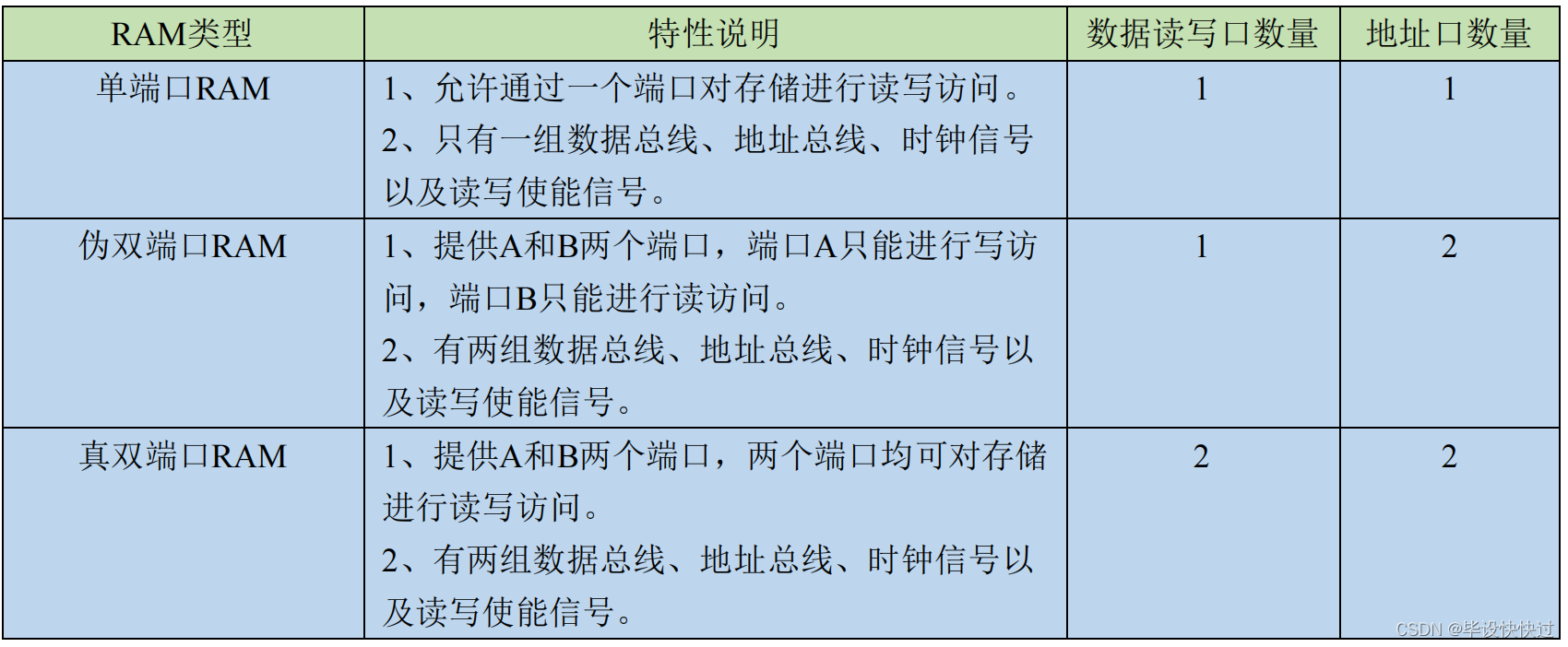

RAM(Random Access Memory)随机访问存储器,包含静态和动态RAM。静态 RAM 只要有供电,它保存的数据就不会丢失,一般包括单端口 RAM(Single Port RAM,缩写为 SP RAM)、简单双端口 RAM(Simple Dual Port RAM,缩写为 SDP RAM,也叫伪双端口 RAM)和真双端口 RAM(True Dual Port RAM,缩写为 TDP RAM)。而动态 RAM 在供电的情况下,还需要根据其要求的时间来对存储的数据进行刷新,才能保持存储的数据不会丢失,一般包括 SDRAM 和 DDR SDRAM。

ROM(只读存储器),只读存储器一般包括 PROM、EPROM 和 EEPROM 等,是非易失性的存储器。

1.2RAM IP核简介

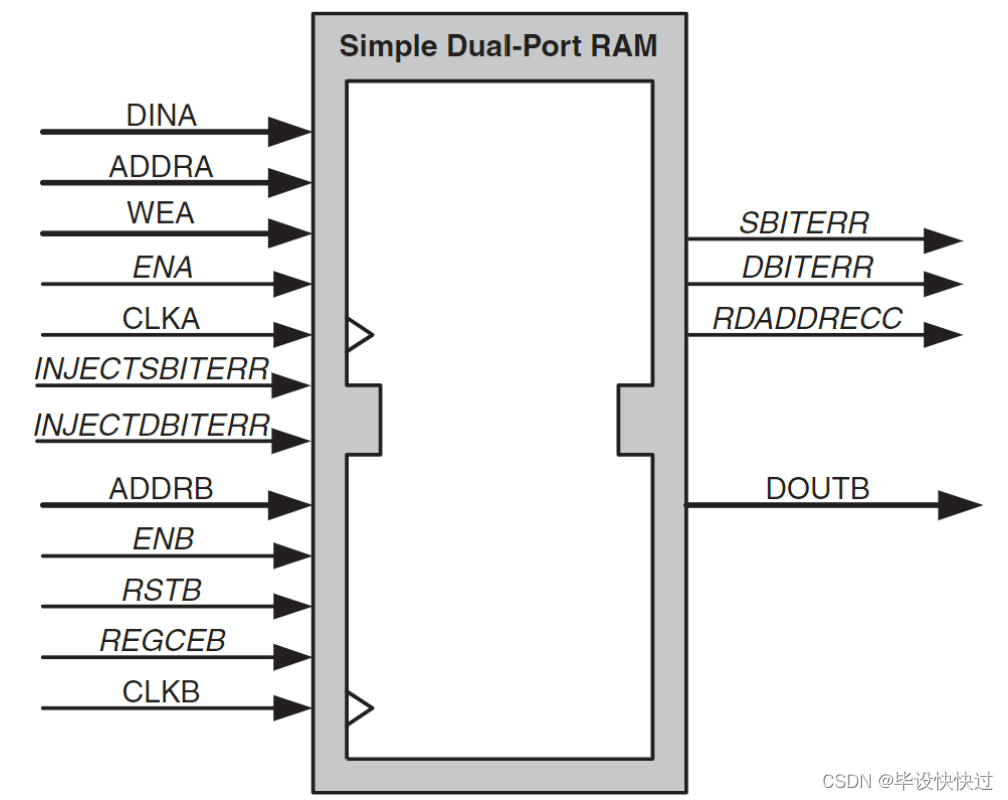

这里以伪双端口RAM为例进行介绍。简单双端口 RAM 的端口 A 只能写不能读,端口 B 只能读不能写。

DINA:写数据(数据数值);

ADDRA:写数据地址;

ENA:写使能端,该值为高,DINA的值才可以被写进ADDRA中;

WEA:写使能,高电平表示向RAM中写入数据,低电平表示从RAM中读出数据;

ADDRB:读数据地址;

ENB:读使能端,该值为高,从ADDRB中读出数据

DOUTB:读数据(数据数值)。

二.实验任务

本章实验任务是将 Xilinx BMG IP 核配置成一个同步的伪双端口 RAM 并对其进行读写操作,然后通过仿真观察波形是否正确,最后将设计下载到 FPGA 开发板中,并通过在线调试工具对实验结果进行观察。

三.RAM IP核配置

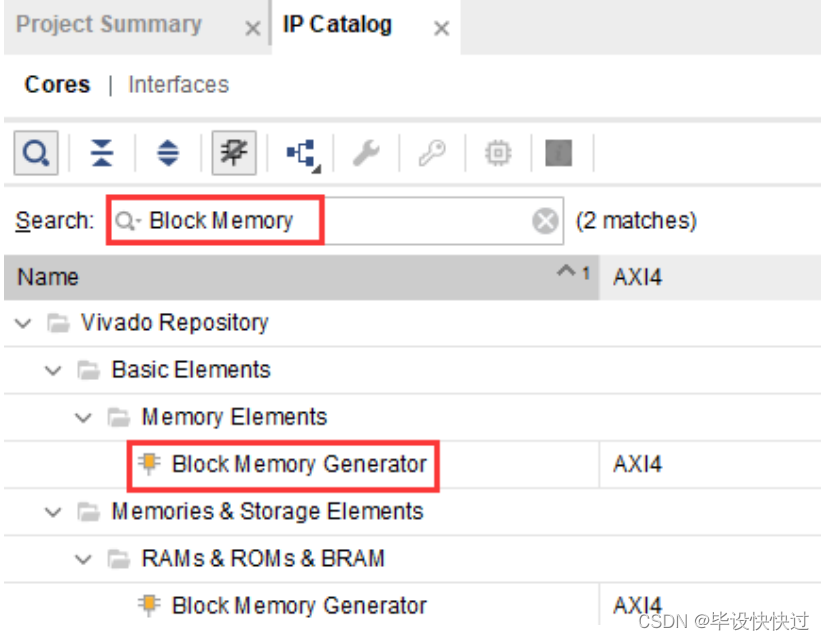

1.搜索RAM IP核

2.memory type 中选择”简单双端口“模式,其余保持默认。

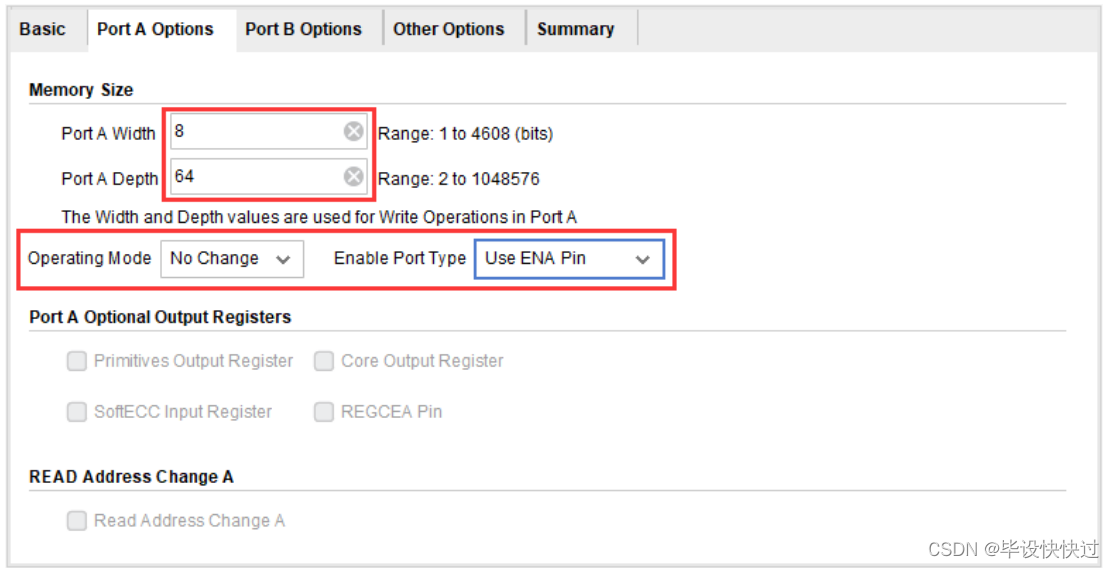

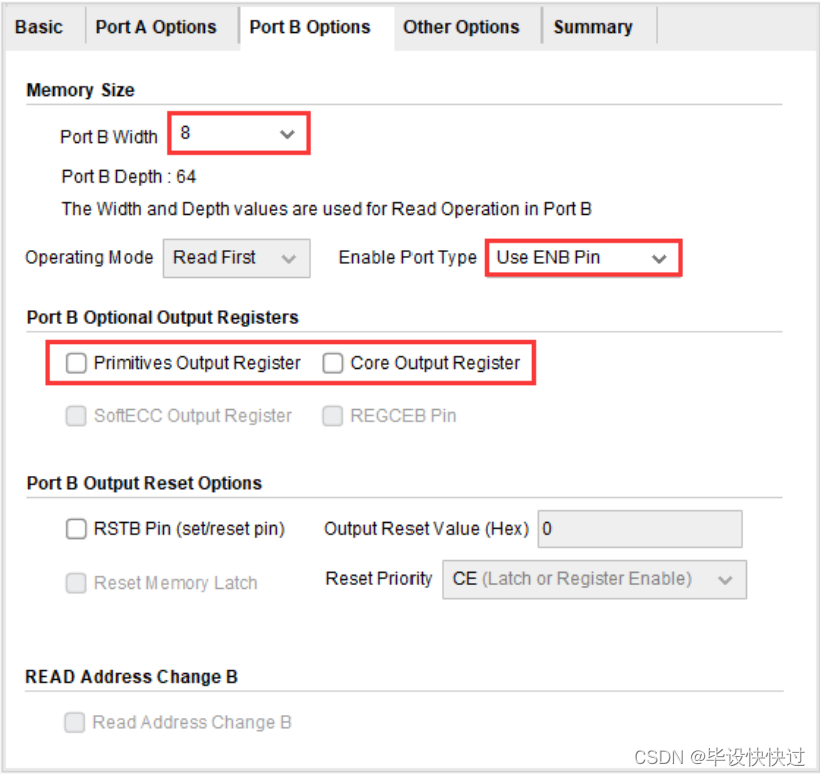

3. 分别对读/写端口进行配置。

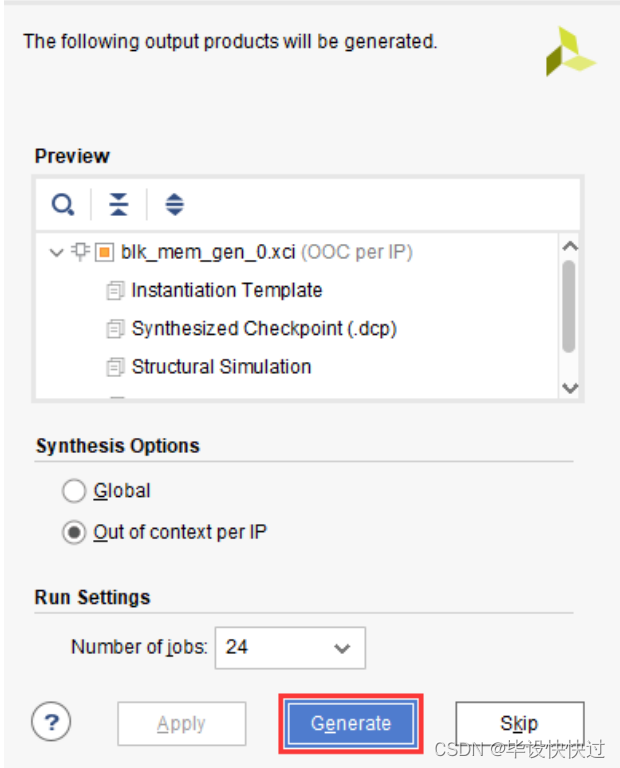

4.其余选项默认,最后生成IP核即可。

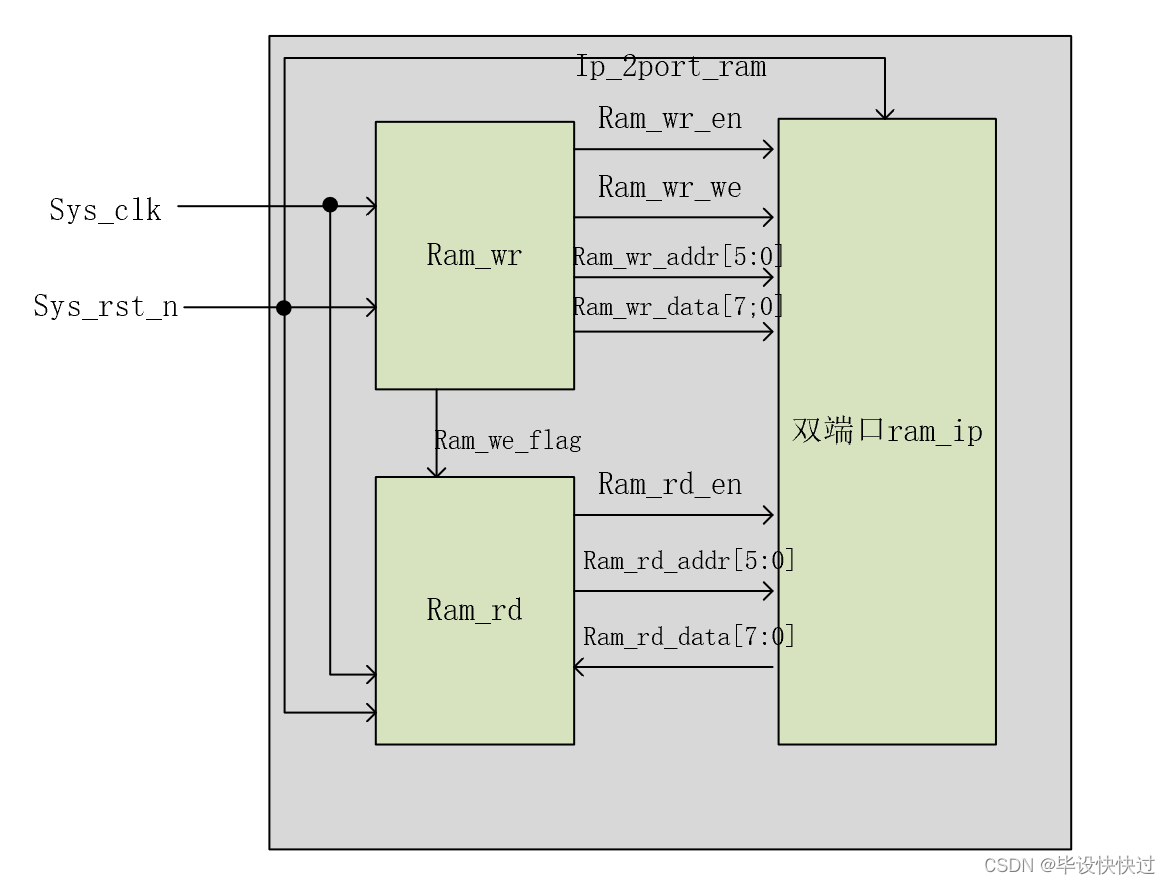

四.模块设计

五.波形图绘制

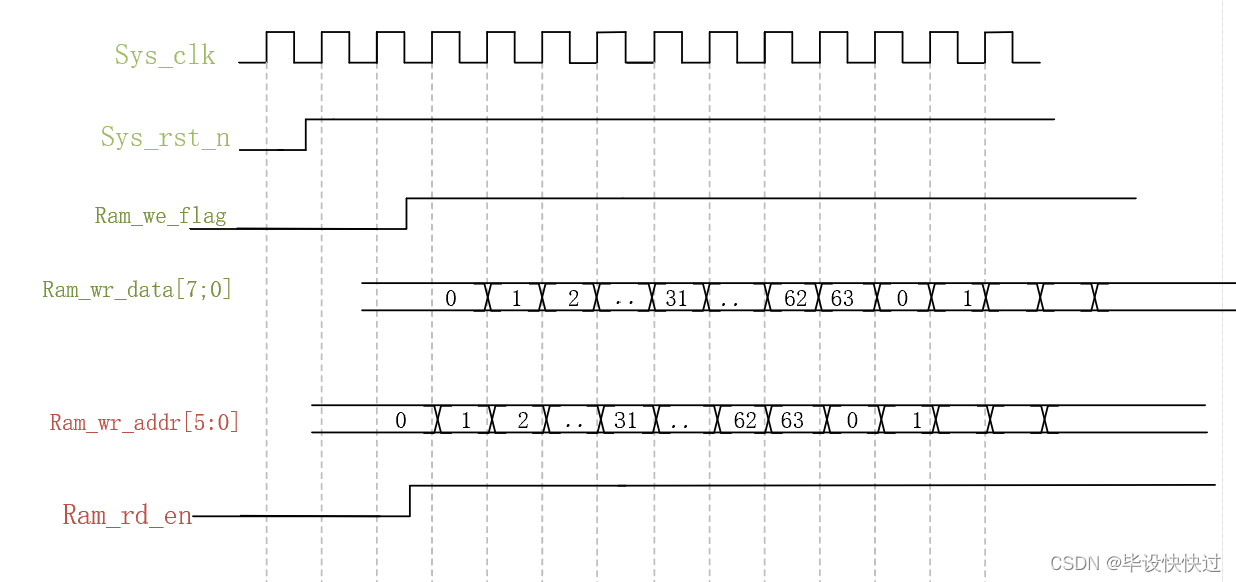

5.1写模块波形图绘制

系统清零信号结束后,en和we都为高电平,进入读数据模式,实验要求读数据深度是64,宽度8,则此时每来一个时钟脉冲,就会在写数据地址上写入一个数据,从0 开始写,到63截止,因为数据深度为64。在写数据写到31时,写标志位(中间信号)翻转,则读模块开始读数据。这里添加写标志位的目的是防止同时对某一地址进行同写同读操作,从而避免掉发生”读写冲突“或者”写写冲突“的情况。

5.2 读模块波形图绘制

当系统复位结束后,en与we_flag保持一致,只要写标志位为高电平,读使能立即赋值为1,进入读数据模块。每来一个时钟脉冲,就从读地址端读出一个数据。

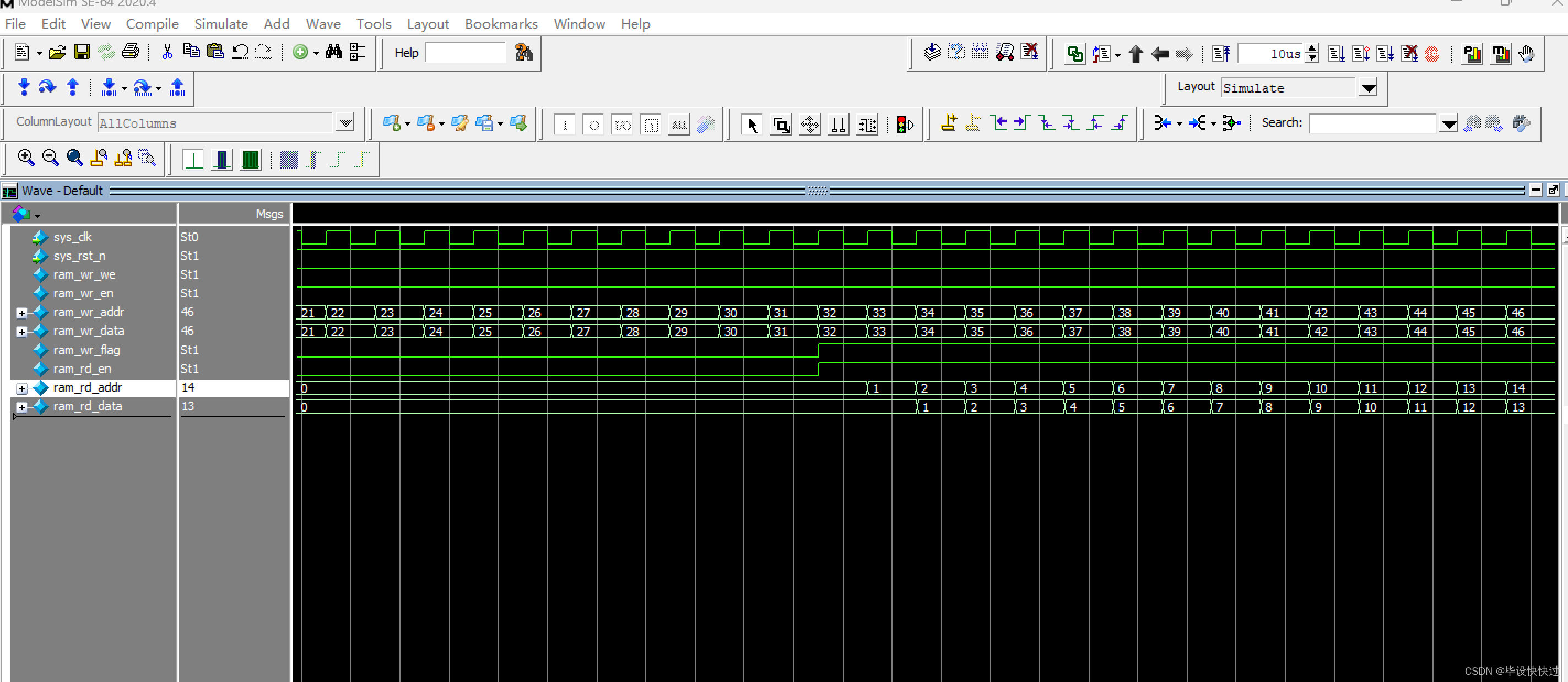

六.vivado和modelsim联合仿真验证

可以看出和预设波形图完全一致,符合预期设计。

七.板级验证和ILA在线调试分析

7.1ILA

ILA(Integrated Logic Analyzer)集成逻辑分析仪:可定制的集成逻辑分析仪(ILA)IP核是一种逻辑分析仪内核,可用于监控设计的内部信号。ILA内核包括现代逻辑分析仪的许多高级功能,包括布尔触发方程和边沿转换触发器。由于ILA内核与被监视的设计同步,因此应用于设计的所有设计时钟约束也会应用于ILA内核内的组件。

7.2下板验证

1.进行引脚约束。

2.对观察信号添加debug属性

3.进行综合

4.打开综合选项下的”set debug“,可以看出步骤2中添加debug属性的信号已经自动添加进来。然后保存即可。

4.打开综合选项下的”set debug“,可以看出步骤2中添加debug属性的信号已经自动添加进来。然后保存即可。

5.生成比特流文件

6.下板验证。可以看出与上面仿真波形一致。

1649

1649

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?