前言

同样是之前的网站,也PASS了网站的对比。不过呢,经过之前的“边长为5的等腰三角型”事件后,我对这网站的对比结果和PASS就不是那么信任了。具体是个什么事件呢,事情的经过是这个样子的,那一天我心血来潮看了看SHELL的题目:

打印边长为5的等腰三角形。

你的脚本应该输出

*

* *

* * *

* * * *

* * * * *

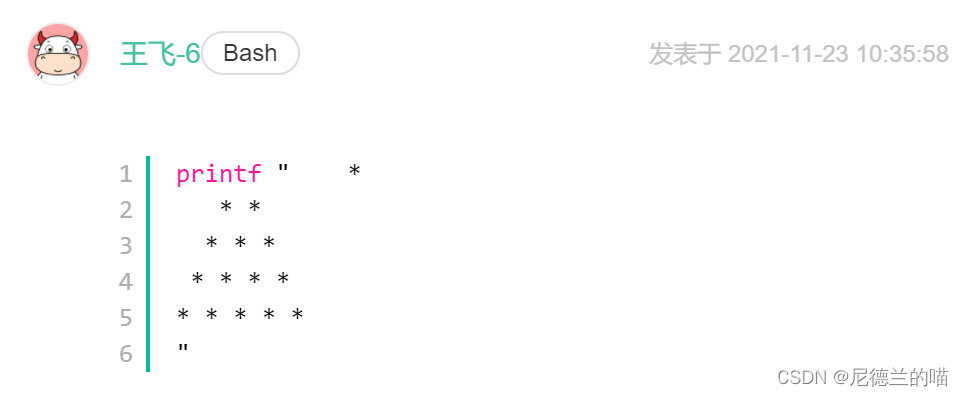

我一看这题有意思哈,然后手贱点开了评论:

啊啊啊哈哈哈哈哈哈嘎嘎嘎哈哈哈或哈哈奥奥奥或或过!

然后我头铁试了一下:

哈哈哈哈哈哈~~~空气中充满了欢快的气氛。

所以呢这导致我对网站的评判结果不太信任,那么这个题就顺着说下我的解题好了,不保证一定是对的啊;

题目

题目如下:

在data_en为高期间,data_in将保持不变,data_en为高至少保持3个B时钟周期。表明,当data_en为高时,可将数据进行同步。

本题中data_in端数据变化频率很低,相邻两个数据间的变化,至少间隔10个B时钟周期。

接口如下:

module mux(

input clk_a ,

input clk_b ,

input arstn ,

input brstn ,

input [3:0] data_in ,

input data_en ,

output reg [3:0] dataout

);

endmodule解题思路

跨异步DUX结构,结构图应该还比较简单,之前的博文里总结过(如果结果想错了那就一条道走到黑吧~):

按照这个结构进行解题,先把跨异步打拍模块做出来。我希望做一个打拍可配置的单比特跨异步模块,所以很显然的我需要用到generate语法,但是这个语法我记得很差,尤其不知道怎么和always一起使用,基本就会例化模块,那么变通下,我先做寄存器模块(请忽略位宽不匹配问题):

module dffr#(

parameter WIDTH = 1

)(

input clk,

input rst_n,

input [WIDTH -1:0]in,

output [WIDTH -1:0]out

);

reg [WIDTH -1:0]out;

always @(posedge clk or negedge rst_n)begin

if(~rst_n) out <= 0;

else out <= in;

end

endmodule有了打拍模块,做单比特跨异步模块就简单很多了:

module sync_cell #(

parameter SYNC_CYC = 2

)(

input clk,

input rst_n,

input in,

output out

);

wire [SYNC_CYC :0]in_dff;

assign in_dff[0] = in;

assign out = in_dff[SYNC_CYC];

genvar i;

generate

for(i=1; i<=SYNC_CYC; i=i+1)begin: inst_rtl

dffr u_dffr[i](clk, rst_n, in_dff[i-1], in_dff[i]);

end

endgenerate

endmodule那么接下来要做的就是把控制信号打拍送到B时钟域,然后检测信号上升沿,采样即可:

module mux(

input clk_a ,

input clk_b ,

input arstn ,

input brstn ,

input [3:0] data_in ,

input data_en ,

output reg [3:0] dataout

);

wire data_en_sync;

wire data_en_sync_ff;

wire data_en_sync_ch;

sync_cell u_sync(clk_b, brstn, data_en, data_en_sync);

dffr u_data_en_sync_ff(clk_b, brstn, data_en_sync, data_en_sync_ff);

assign data_en_sync_ch = (data_en_sync == 1) && (data_en_sync_ff == 0);

always @(posedge clk_b or negedge brstn)begin

if(~brstn) dataout <= 0;

else if(data_en_sync_ch) dataout <= data_in;

end

endmodule

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?