所用Linux系统为openSUSE64位,软件为VCS2012

在Linux下对verilogHDL进行功能仿真时非常必要的,下面提供两种常见方式。

1.脚本方式

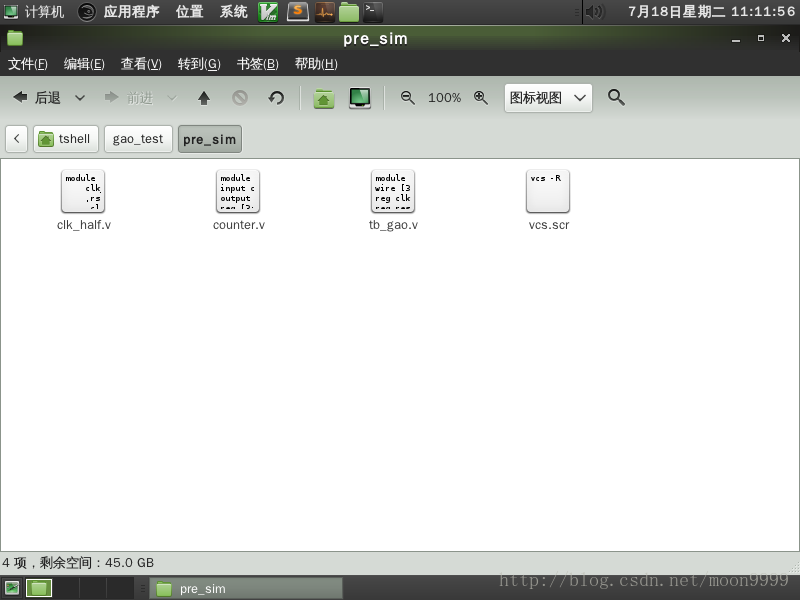

1)建立工作文件夹pre_sim,并将tb文件和所有.v文件复制进入此文件夹

mkdir pre_sim

2)修改testbench文件

为输出波形文件,在testbench文件中加入如下语句

initial begin

$dumpfile("counter.vcd"); //待输出的波形文件名,可更改

$dumpvars(0,u0); //u0为testbench中实例化的顶层文件名称,注意根据实际情况修改该名字

end

initial #1000 $finish; //仿真电路的时间

在openSUSE 64位Linux系统中,使用VCS2012进行Verilog HDL的功能仿真有两种常见方法:脚本方式和命令行方式。脚本方式涉及创建pre_sim文件夹,编辑testbench文件以输出波形,然后运行vcs.scr脚本;命令行方式则包括在vcs_test文件夹中放置工程文件,直接在终端运行vcs命令并观察图形界面中的波形。

在openSUSE 64位Linux系统中,使用VCS2012进行Verilog HDL的功能仿真有两种常见方法:脚本方式和命令行方式。脚本方式涉及创建pre_sim文件夹,编辑testbench文件以输出波形,然后运行vcs.scr脚本;命令行方式则包括在vcs_test文件夹中放置工程文件,直接在终端运行vcs命令并观察图形界面中的波形。

订阅专栏 解锁全文

订阅专栏 解锁全文

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?