我们的目标是┏ (゜ω゜)=☞芯片前端全栈工程师~喵!

前言

最近因为可能要写一个基于axi4协议的ddr模型(纯学习),正好也赶上我创作瓶颈了所以就把axi协议里的一些概念拿出来复习复习。

概念理解

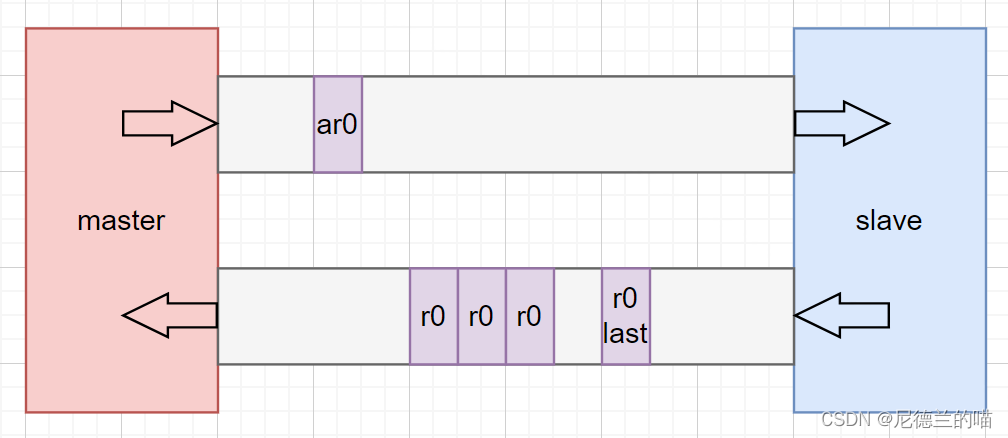

outstanding适用于需要反馈的接口协议,比如AXI协议中的ar请求就需要rdata(last)作为反馈,如下图一个arlen==3的ar0_req,对应的就是返回4笔rdata,最后一笔rdata携带last标志。当master收到r0_last时候,ar0_req这笔请求才能算是结束:

那么这个时候master就面临着选择了:是等这笔ar0_req的返回信息都收全再发下一笔呢,还是不管不顾的接着发呢?显然,不等这一笔返回而继续发送请求的收益是最大的,这使得发送与接收得以解耦达到流水的效果,不阻塞后续的操作,这个概念就是outstanding。对于axi协议,如果允许在没有收回任何一笔last(resp)的情况下允许对外发送N笔ar/aw请求,则outstanding最大值为N。

但是显然outstanding不能是无限大的,一是过大会过度占用外部总线带宽,二是内部需要保留ostd的相关信息。比如乱序返回,那内部需要有报错已发出的请求id的entry,即使顺序返回内部也需要个计数器记录回没回完。尤其对于读的ostd控制要更加严格,因为如果master没有能力接收需求的数据,阻塞在通路上可能会造成死锁。

对于axi读请求,master的数据接收能力可以表示为:

master所需最大缓存能力 = outstanding * (burst_length+1) * 带宽如outstanding为16,burst_length为3,带宽为32B,则master至少应该能够接收2048B数据,不阻塞总线。那么一个master如何确定需要多大的outstanding值呢?可以参考下面这个公式:

ostd * (burst+1) * 带宽 / 有效带宽 = 访存延时大概的意思可以理解为,通路上所有的数据在被用光的时候,下一个返回的数据可以续上。显然,burst_length越大ostd可以越小,带宽利用率(有效带宽/带宽)越大ostd越大,访存延时越大ostd越大。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?