FPGA入门学习—LED驱动电路设计:

基础功能:驱动8个LED循环亮灭

module设计文件:

`timescale 1ns / 1ps

module LED_Display_8(

input clk,

input rst_n,

output reg [7:0]LED

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

LED <= 8'd0;

else if(LED == 8'd0)

LED <= 8'b0000_0001;

else if(LED == 8'b1000_0000)

LED <= 8'b0000_0001;

else

LED <= LED<<1;

end

endmodule

module仿真文件:

`timescale 1ns / 1ps

module tb_LED_Diaplay_8;

reg clk;

reg rst_n;

wire [7:0]LED;

initial begin

clk = 0;

rst_n = 0;

#200; rst_n = 1;

end

always#50 clk = ~clk;

LED_Display_8 u_LED_Display_8(

.clk(clk),

.rst_n(rst_n),

.LED(LED)

);

endmodule

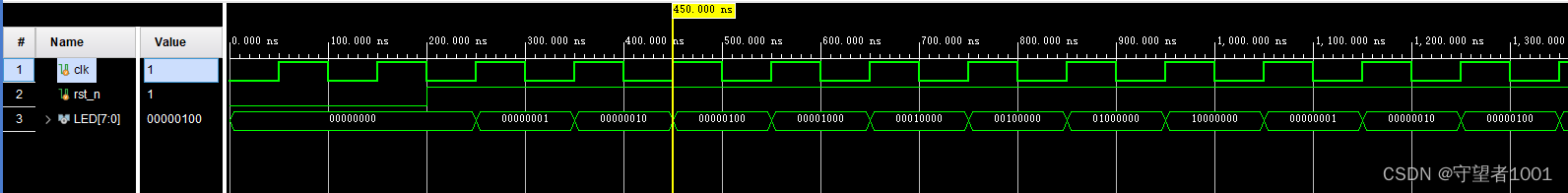

仿真波形图:

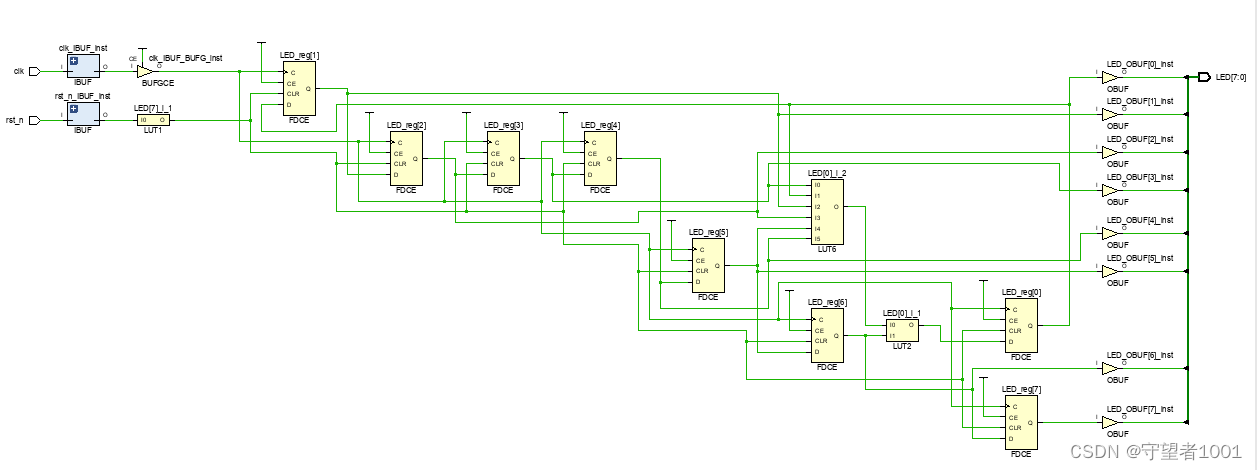

综合原理图:

4748

4748

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?