ZYNQ学习_1-FPGA实现I/O点亮LED灯

文章目录

前言

这里用于记录小白的FPGA学习过程

使用的硬件平台:ZYNQ7020

参考资料:ALINX 《ZYNQ开发平台教程》

开发工具:Vivado_2018.03

一、学习目标

实现效果:

1.开发板上LED灯按1Hz的频率正常闪烁;

硬件资源:

| 名称 | 引脚 | 描述 |

|---|---|---|

| LED1 | M14 | I/O输出 |

| LED2 | M15 | I/O输出 |

| LED3 | K16 | I/O输出 |

| LED4 | J16 | I/O输出 |

| rst_n | N15 | I/O按键用作复位引脚 |

| sys_clk | U18 | 时钟输入引脚 |

学习内容:

1. Vivado工程创建

2. 编写Verilog语言

3. 添加引脚绑定

4. 时序约束

5. 仿真实现

6. 程序下载

7. 在线ILA调试

二、详细实现步骤

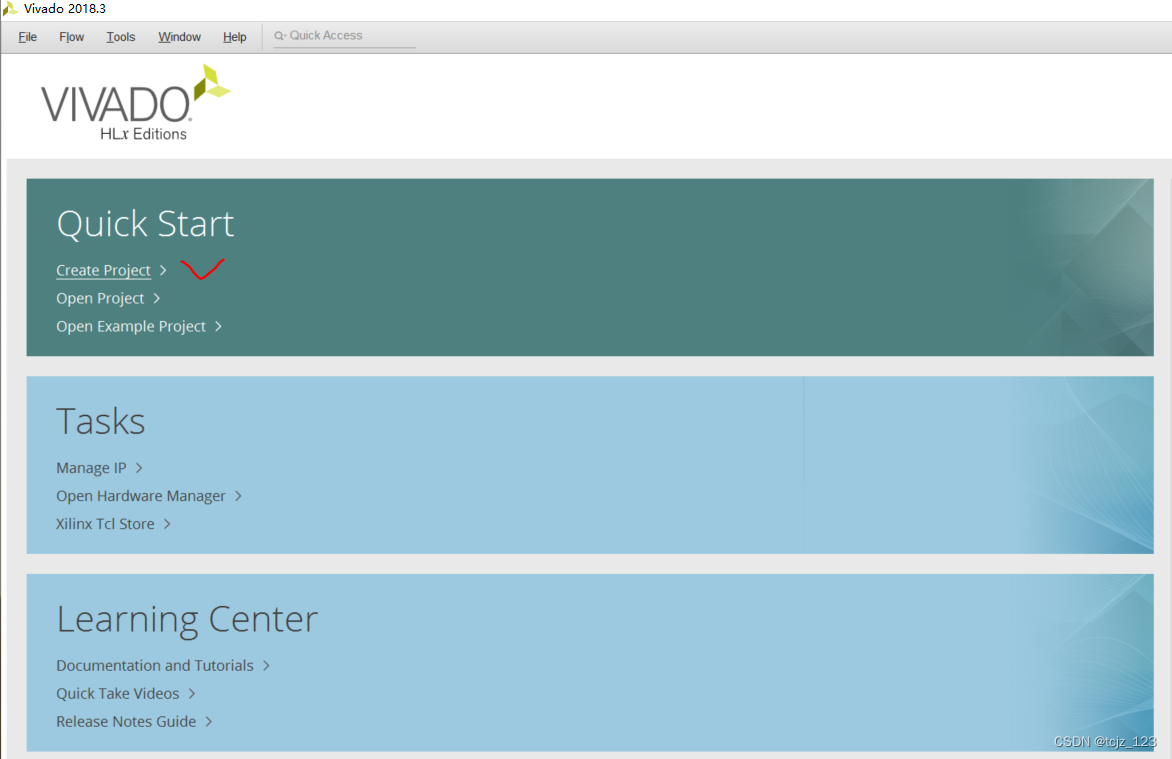

1.创建Vivado工程

-

点击“Create Project”,选择“next”,设置路径与工程名称,

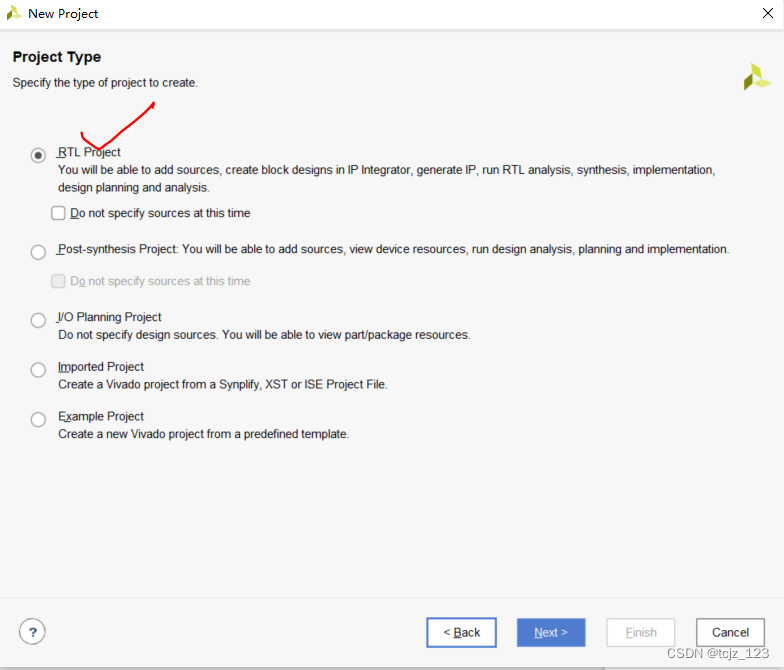

-

选择"RTL Project"

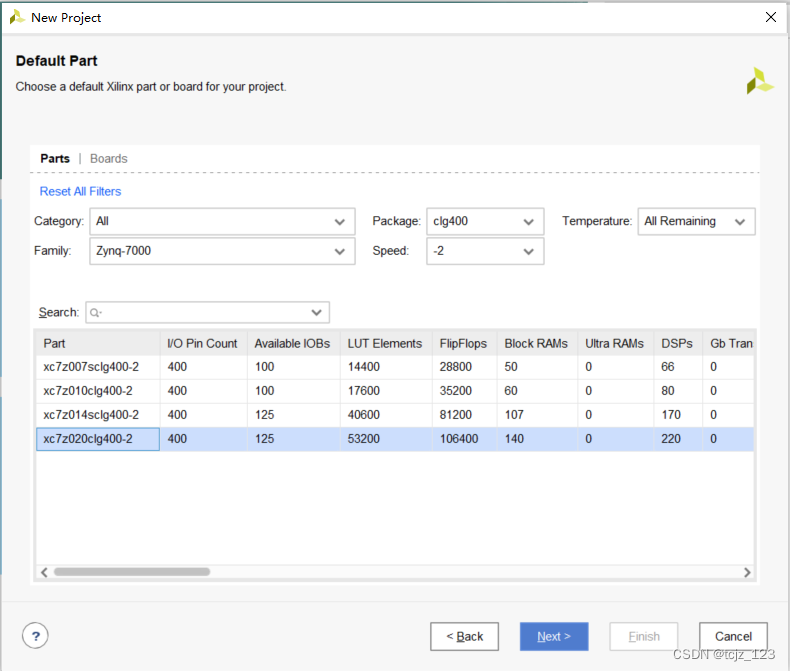

-

选择产品系列,点击Finish

2.创建VerilogHDL文件

-

选择“Add Sources”,选择“Add or create design sources”,选择下一步

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

983

983

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?