FPGA入门学习—异步复位&同步复位:

首先要知道什么是异步复位和同步复位:

- 异步复位:简单来说就是复位信号和系统的时钟信号的触发是相互独立的;

- 同步复位:复位信号只有在时钟信号的变化边沿才有效,二者不相互独立。

下面用简单的逻辑来比较二者的区别:

异步复位:

`timescale 1ns / 1ps

//测试同步/异步复位的区别

module test_reset(

input clk,

input rst_n,

input a,

output reg b

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

b <= 0;

else

b <= a;

end

endmodule

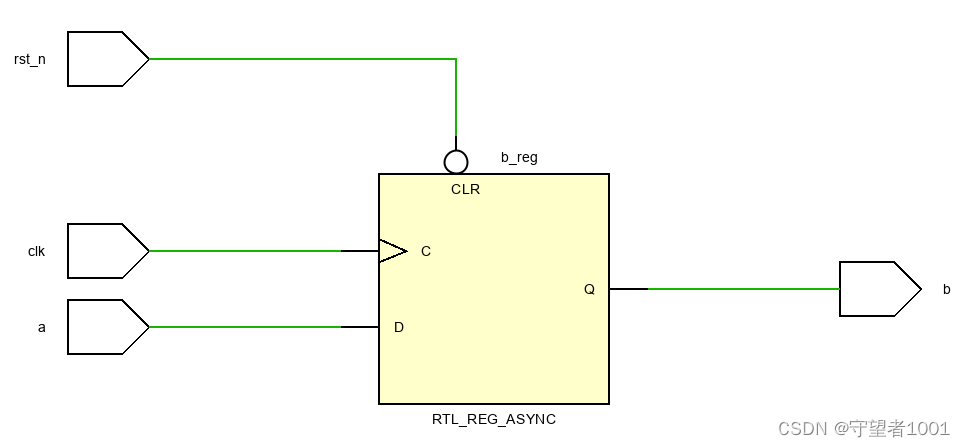

RTL分析原理图:

同步复位:

`timescale 1ns / 1ps

//测试同步/异步复位的区别

module test_reset(

input clk,

input rst_n,

input a,

output reg b

);

always @(posedge clk) begin

if(!rst_n)

b <= 0;

else

b <= a;

end

endmodule

相比于异步复位,同步复位的always语句为 always @(posedge clk)

RTL分析原理图:

比较两种复位方式的结果我们可以发现,异步复位是将复位信号作为触发器的复位端来使用,而同步复位则是将其当成一个普通的输入信号。也可以看到同步相对于异步增加了一个二选一的多路选择器,这也势必会增加FPGA内部的资源消耗。

1033

1033

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?